峰值保持電路是用于捕捉變化的輸入信號的峰值,是利用記錄儀記錄峰值的關鍵電路,其有各種電路結構,分析也相對簡單。

電路設計最簡單的就是功能設計,比如設計峰值保持器,最頭疼的就是設計時要求電路滿足一定的指標,比如要求峰值保持器滿足2mv的跟蹤精度、能對4Mhz的波形進行跟蹤,一下子問題就復雜了,在不講指標要求的情況下,談電路設計是毫無意義的,這里介紹兩種經典實現:一種是TI公司的參考設計,采用高速運放;另一種是采用高速比較器的實現方式。

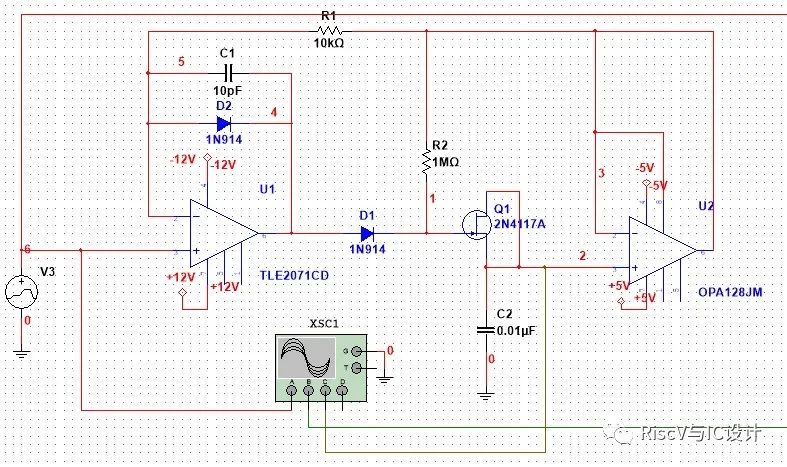

1)采用高速運放

- 此電路的Q1是保持開關,這里使用JFET原因是其反向漏電流遠遠小于二極管或晶體管;

- U2是TI的靜電計運放,其輸入偏置電流非常低,可以達到十幾fA,因而電容C2基本不會向外放電;

- C2電容最好采用聚苯乙烯電容,其容量范圍(100pF~0.01uF),具有負溫度系數、絕緣電阻高達100GΩ、極低泄漏電流;

- D2電容的主要作用是讓運放不要開環應用,始終工作在線性狀態,因為運放開環應用時,其內部的放大管可能工作在深度飽和狀態,當狀態開關切換時會比較慢,這也是運放與比較器的最大區別!一般有指標要求時,都不會用運放當比較器使用,因為這會使運放內部管子工作在開關截止狀態,開關切換速度慢。

2)采用高速比較器

此電路更加簡潔,工作速度更快,可以跟蹤MHz以上的信號,是非常實用的電路

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

二極管

+關注

關注

147文章

9702瀏覽量

167559 -

比較器

+關注

關注

14文章

1658瀏覽量

107428 -

JFET

+關注

關注

2文章

142瀏覽量

22157 -

峰值保持電路

+關注

關注

2文章

4瀏覽量

13586 -

偏置電流

+關注

關注

1文章

118瀏覽量

13187

發布評論請先 登錄

相關推薦

峰值檢測電路的基本組成

峰值檢測電路(Peak Detection Circuit),又稱為峰值檢測器(Peak Detector),是一種用于測量信號波形中最大值(正峰值)或最小值(負

用THS4631做一個峰值保持電路的緩沖級遇到的疑問求解

各位,我用THS4631做一個峰值保持電路的緩沖級。具體就是接成普通的電壓跟隨器形式。+/-5v供電。測量時發現輸出(pin6)是一個4.2v的高電平。而我的輸入實際只是1v的正弦波。單獨測試

發表于 09-24 07:35

設計一個峰值保持電路,在較高頻率下(10khz以上)電路就不正常,為什么?

我要設計一個峰值保持電路,在低頻時工作正常。但是在較高頻率下(10khz以上)電路就不正常。請問是什么原因呢?怎么設計峰值

發表于 09-10 08:31

LMH6601是不是跨導型,能不能做峰值保持電路呢?

我想做個峰值保持電路,跨導型的查到了4個放大器,但是我感覺LMH6601不像是跨導型。有哪位比較懂的幫忙看下數據手冊,LMH6601是不是跨導型,能不能做峰值

發表于 09-09 06:17

做一個峰值保持器,用opa615仿真時保持住微弱信號?

請教一下,最近要做一個峰值保持器,頻率為5M,信號幅值為0.05-2.5v的脈沖,用opa615仿真時發現只有信號1.3v以上才可以保持住,1.3v以下的信號就完全不行了。請問有什么方法可以

發表于 08-27 08:01

OPA615做峰值保持電路遇到的兩個問題求解

按照OPA615手冊設計的電路制作后,有兩個問題1.無法保持峰值,只能根據HOLD信號控制鎖定點。2.保持信號的衰減嚴重,有一個較為明顯的下降,不足以維持我AD的采樣。

發表于 08-23 08:23

按照OPA615 datasheet中提供的電路圖搭建峰值保持電路,輸出峰值誤差較大的原因?

按照OPA615 datasheet中提供的電路圖搭建峰值保持電路,輸入64MHz方波(VCXO提供),Vpp=1.5V(0~1.5V),二極管用的是1N4148,電容用50pF,

發表于 08-22 06:43

OPA615峰值無法保持怎么解決?

您好,我閱讀Datasheet上面SOTA兩種上升時間為2ns和10ns

然后我按照Figure48(雙峰值探測電路)進行仿真。保持結果的上升時間為10ns,需要保持的脈沖寬度為8n

發表于 08-22 06:10

根據opa615的datasheet搭建了峰值保持電路,效果不理想是什么原因導致的?

各位大大,本人根據網上資料以及opa615的datasheet搭建了峰值保持電路,但是效果很不理想,當電容是27pf的時候,control端給5v高電壓時是電壓跟隨現象。當電容變為100pf的時候,是

發表于 08-21 08:15

請問500M帶寬的峰值保持電路是否可行?

需要采集的信號 為每50ms 1個10ns寬度脈沖.需要記錄該脈沖的最大幅度和對應的時刻(精確至MS).我的想法是用峰值保持電路+低速AD 來實現這一功能,不知道能否實現,若能實現.希望推薦相應的器件和參考

發表于 08-21 06:54

OPA860做峰值保持電路,無法實現峰值保持的功能是為什么?

我用opa860芯片做峰值保持電路,輸入為10ns的脈沖信號,我在論壇里看到有類似的帖子,并且按照上面的電路原理圖用Tina仿真,仿真結果是能夠實現

發表于 08-01 07:46

峰值保持電路后方接入了OPA357作為跟隨器,掉電速度很快是什么原因?

峰值保持電路后方接入了OPA357作為跟隨器,原理圖如下,然而在不接跟隨器的情況下他的掉電速度反而比接跟隨器的更慢,請教一下原因,有什么推薦的芯片作為跟隨器來延長他的保持時間不讓他掉電

發表于 08-01 07:11

經典電路分析:峰值保持電路

經典電路分析:峰值保持電路

評論