FPGA發(fā)展到今天,SerDes(Serializer-Deserializer)基本上是器件的標(biāo)配了。從PCI發(fā)展到PCI-E,從ATA發(fā)展到SATA,從并行ADC接口到JESD204,從RIO到Serial RIO……等等,都是在借助SerDes來提高數(shù)據(jù)傳輸?shù)男阅堋erDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶手冊(cè)的內(nèi)容只是描述了相對(duì)粗略的概念以及使用方法,并不能完全解釋SerDes是怎么工作的。在使用SerDes的過程中,設(shè)計(jì)者有太多的疑惑:為什么在傳輸?shù)倪^程中沒有時(shí)鐘信號(hào)?什么是加重和均衡?抖動(dòng)和誤碼是什么關(guān)系?各種抖動(dòng)之間有什么關(guān)系?時(shí)鐘怎么恢復(fù)?等等這些問題,如果設(shè)計(jì)者能夠完全理解這些問題,那么對(duì)于SerDes的開發(fā)也不再是難事。本文試著從一個(gè)SerDes用戶的角度來理解SerDes是怎么設(shè)計(jì)的。

SerDes的價(jià)值

并行總線接口

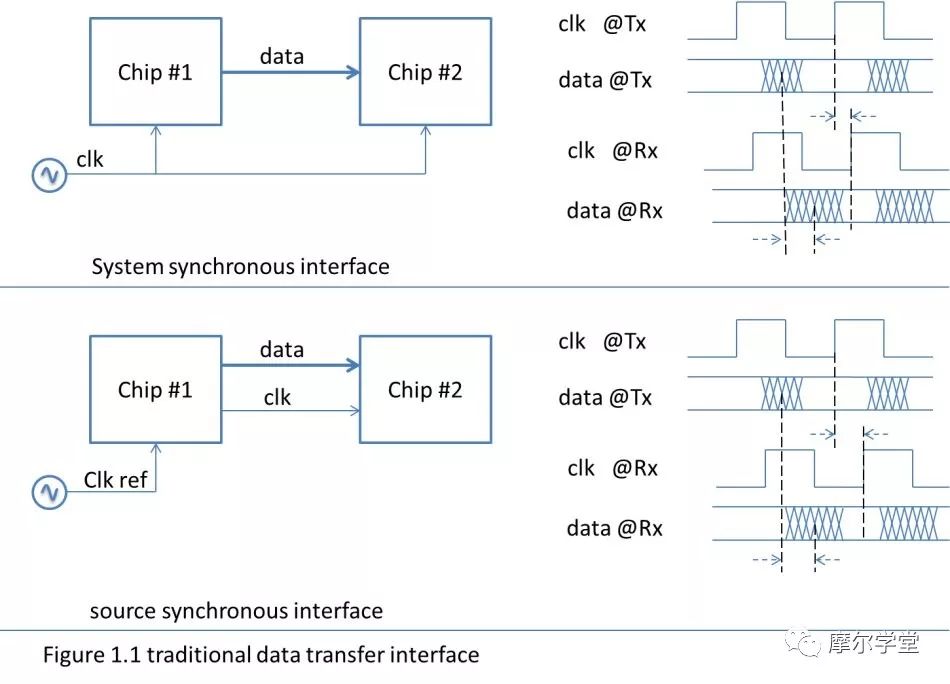

在芯片之間的數(shù)據(jù)傳輸,最早的時(shí)候是以串行傳輸?shù)姆绞酵瓿傻模S著數(shù)據(jù)量的越來越大,串行數(shù)據(jù)傳輸?shù)娜秉c(diǎn)變得特別明顯:速率太低。所以芯片設(shè)計(jì)者就想著增加數(shù)據(jù)傳輸?shù)奈粚挘貌⑿械姆绞絺鬏敂?shù)據(jù),這樣相對(duì)于串行傳輸就有更高的傳輸速率。芯片之間的互聯(lián)通古系統(tǒng)同步或者源同步的并行接口傳輸數(shù)據(jù)。圖1.1演示了系統(tǒng)同步和源同步并行接口。

隨著接口頻率的提高,在系統(tǒng)同步接口方式中,有幾個(gè)因素限制了有效數(shù)據(jù)串口寬度的繼續(xù)增加。

時(shí)鐘到達(dá)兩個(gè)芯片的傳播延時(shí)不相等(clock skew)

并行數(shù)據(jù)各個(gè)bit的傳播延時(shí)博相等 (data skew)

時(shí)鐘的傳播延時(shí)和數(shù)據(jù)的傳播延時(shí)不一致(skew between data and clock)

雖然可以通過在目的芯片(chip #2)內(nèi)使用PLL補(bǔ)償時(shí)鐘延時(shí)差(clock skew),但是PVT(Process Verification Test)變化時(shí),時(shí)鐘沿是的變化量和數(shù)據(jù)延時(shí)的變化量是不一樣的。這又進(jìn)一步惡化了數(shù)據(jù)窗口,即無法通過簡單的、不斷增加的數(shù)據(jù)總線數(shù)達(dá)到增加數(shù)據(jù)傳輸速率的目的。

源同步接口方式中,發(fā)送端Tx把時(shí)鐘伴隨數(shù)據(jù)一起發(fā)送出去,限制了clock skew對(duì)有效數(shù)據(jù)窗口的危害。通常在發(fā)送測芯片內(nèi)部,源同步接口把時(shí)鐘信號(hào)和數(shù)據(jù)信號(hào)當(dāng)作一樣來處理,也就是讓它和數(shù)據(jù)信號(hào)經(jīng)過相同的路徑,以保證相同的延時(shí)。這樣PVT變化時(shí),時(shí)鐘和數(shù)據(jù)會(huì)朝著同一個(gè)方向增大或者減小相同的量,對(duì)skew最有利。

我們來做一些合理的典型假設(shè),假設(shè)一個(gè)32bit數(shù)據(jù)的并行總線:

發(fā)送端的數(shù)據(jù)skew = 50 ps (很高的要求)

PCB總線引入的skew = 50 ps (很高的要求)

時(shí)鐘的周期抖動(dòng)jitter = +/- 50 ps (很高的要求)

接收端觸發(fā)器采樣窗口 = 250 ps (Xilinx V7 高端器件的IO觸發(fā)器)

可以大致估算出并行接口的最高時(shí)鐘 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz(SDR).

利用源同步接口,數(shù)據(jù)的有效窗口可以提高很多,通常頻率都是在1GHz以下。在實(shí)際使用中可以見到如SPI4.2接口的時(shí)鐘可以高達(dá)DDR 700HNz * 16 bits位寬。DDR Memory接口也是一種源同步接口,如DDR3在FPGA中可以做到大約800MHz的時(shí)鐘(DDR)。

要提高接口的傳輸帶寬有兩種方法:一種是提高時(shí)鐘頻率;一種是加大數(shù)據(jù)位寬。那么數(shù)據(jù)位寬是不是可以無限制地加大呢?這就要牽扯到另外一個(gè)非常重要的問題----同步切換噪聲(SSN)。

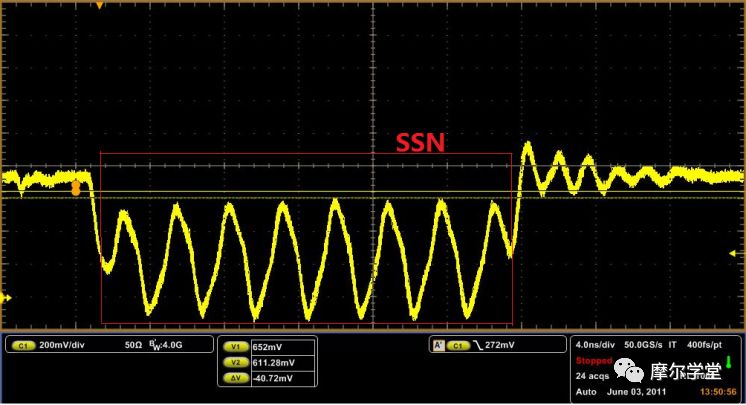

SSN的計(jì)算公式:SSN = L * N * di/dt

L是芯片封裝電感,N是數(shù)據(jù)位寬,di/dt是電流變化的斜率。隨著頻率的提高,數(shù)據(jù)位寬的增加,SSN成為提高傳輸帶寬的主要瓶頸。圖1.2是一個(gè)DDR3串?dāng)_的例子。途中低電平的理論值在0V,由于SSN的影響,低電平表現(xiàn)為震蕩,震蕩噪聲的最大值達(dá)610mv,因此噪聲余量只有1.5V/2 - 610mV = 140mV。

因此也不可能靠無限地提高數(shù)據(jù)位寬來繼續(xù)增加帶寬。一種解決SSN的辦法是使用差分信號(hào)替代單端信號(hào),使用差分信號(hào)可以很好地解決SSN的問題,代價(jià)是使用更多的芯片引腳。使用差分信號(hào)仍然解決不了數(shù)據(jù)skew的問題,很大位寬的差分信號(hào)再加上嚴(yán)格的時(shí)序限制,給并行接口帶來了很大的挑戰(zhàn)。

SerDes接口

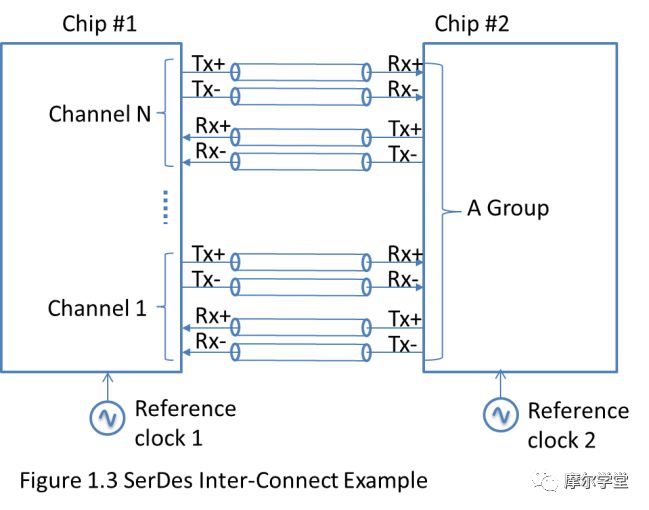

源同步接口的時(shí)鐘頻率已經(jīng)遇到瓶頸,由于信道(channel)的非理想特性,在繼續(xù)提高頻率,信號(hào)會(huì)被嚴(yán)重?fù)p傷,這就需要采用均衡和數(shù)據(jù)時(shí)鐘相位檢測等技術(shù)。這也就是SerDes所采用的技術(shù)。SerDes是串行器和解串器的簡稱。串行器也成為SerDes發(fā)送端(Tx),解串器也成為接收端(Rx)。圖1.3是一個(gè)N對(duì)SerDes收發(fā)通道的互連演示,一般N小于4.

可以看到,SerDes不傳送時(shí)鐘信號(hào),這也是SerDes最特別的地方,SerDes在接收端集成了CDR(Clock Data Recovery)電路,利用CDR從數(shù)據(jù)的邊沿信息中抽取時(shí)鐘,并找到最優(yōu)的采樣位置。

SerDes采用差分方式傳送數(shù)據(jù)。一般會(huì)有多個(gè)通道的數(shù)據(jù)放在一個(gè)group中以共享PLL資源,每個(gè)通道仍然是相互獨(dú)立工作的。

SerDes需要參考時(shí)鐘(Reference Clock),一般也是差分的形式以降低噪聲。接口端Rx和發(fā)送端Tx的參考時(shí)鐘可以允許幾百個(gè)ppm的頻差(plesio-synchronous system),也可以是同頻的時(shí)鐘,但是對(duì)相位差沒有要求。

做個(gè)簡單的比較,一個(gè)SerDes通道(Channel)使用4個(gè)引腳(Tx+/-, Rx+/-),目前的FPGA可以做到高達(dá)28Gbps。而一個(gè)16bit的DDR3-1600的線速率為1.6Gbps*16 = 25Gbps,卻需要50多個(gè)引腳。這樣對(duì)比之下可以看出SerDes在傳輸帶寬上的優(yōu)勢。

相比于源同步接口,SerDes的主要特點(diǎn)包括:

SerDes在數(shù)據(jù)線中時(shí)鐘內(nèi)嵌,不需要傳送時(shí)鐘信號(hào)。

SerDes通過加重/均衡技術(shù)可以實(shí)現(xiàn)高速長距離傳輸,如背板。

SerDes使用了較少的芯片引腳。

中間類型

也存在一些介于SerDes和并行接口之間的接口類型,相對(duì)源同步接口而言,這些中間類型的接口也使用串行器和解串器,同時(shí)也傳送用于同步的時(shí)鐘信號(hào)。這類接口如視頻顯示接口7:1 LVDS等。

SerDes結(jié)構(gòu)

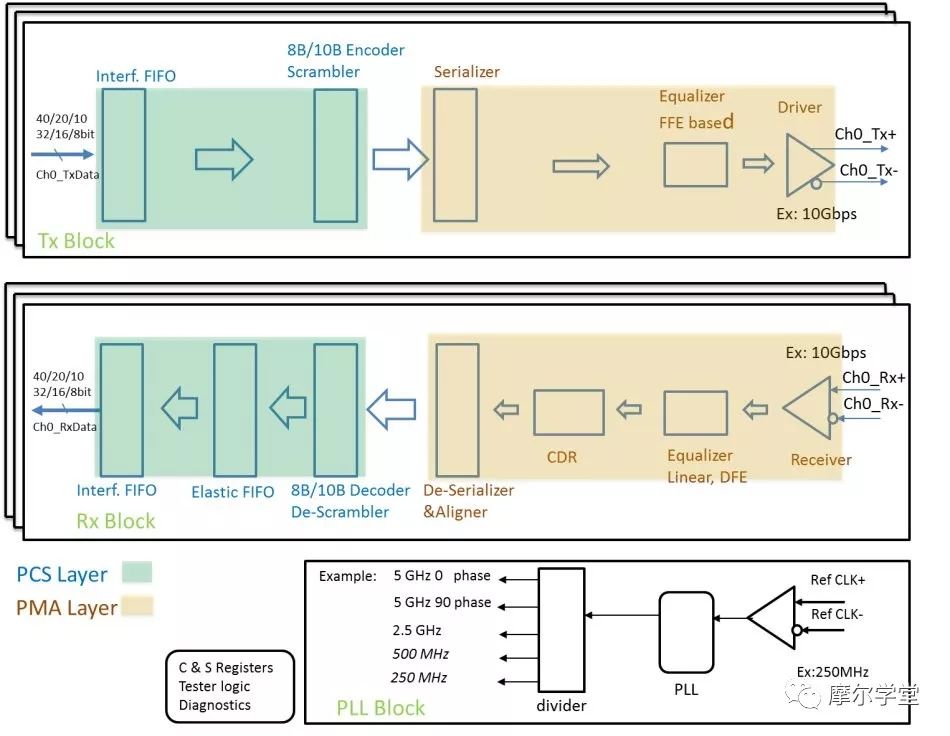

SerDes的主要構(gòu)成可以分為三部分:PLL模塊,發(fā)送模塊Tx,接收模塊Rx。為了方便維護(hù)和測試,還會(huì)包括控制和狀態(tài)寄存器,換回測試,PRBS測試等功能。如圖2.1

圖中藍(lán)色背景子模塊為PCS層,是標(biāo)準(zhǔn)的可綜合CMOS數(shù)字邏輯,可以使用硬件邏輯實(shí)現(xiàn),也可以使用FPGA軟邏輯實(shí)現(xiàn),相對(duì)容易理解。褐色背景的子模塊是PMA層,是數(shù)模混合CML/CMOS電路,是理解SerDes區(qū)別于并行接口的關(guān)鍵,也是本文討論的重點(diǎn)內(nèi)容。

發(fā)送方顯(Tx)信號(hào)的流向:FPGA邏輯(Fabric)發(fā)送過來的并行信號(hào),通過接口FIFO(Interface FIFO),發(fā)送到 8B/10B編碼器(8B/10B encoder)或擾碼器(scambler),以避免數(shù)據(jù)含有較多的0或者較多的1。之后送給串行器(Serializer)進(jìn)行并串轉(zhuǎn)換。串行數(shù)據(jù)警告過均衡器(equalizer)調(diào)理,由驅(qū)動(dòng)器(driver)發(fā)送出去。

接收方向(Rx)信號(hào)的流向,外部串行信號(hào)由線性均衡器(Linear Equalizer)或者DFE(Decision Feedback Equalizer)結(jié)構(gòu)均衡器條例,去除一部分確定性抖動(dòng)(Deterministic jitter).CDR從數(shù)據(jù)中恢復(fù)出來采樣時(shí)鐘,經(jīng)解串器變?yōu)閷?duì)齊的并行信號(hào)。8B/10B解碼器(8B/10B decoder)或解擾其(de-scambler)完成解碼或者解擾。如果是異步時(shí)鐘系統(tǒng)(Plesio-synchronous system),在用戶FIFO之前還應(yīng)該有彈性FIFO來補(bǔ)償頻差。

PLL負(fù)責(zé)產(chǎn)生SerDes各個(gè)模塊所需要的時(shí)鐘信號(hào),并管理這些時(shí)鐘之間的相位關(guān)系。以圖中線速率10Gbps為例,參考時(shí)鐘頻率250MHz。Serializer/Deserializer至少需要5GHz 0相位時(shí)鐘和5GHz 0相位時(shí)鐘和5GHz 90度相位時(shí)鐘,1GHz(10bit并行)/1.25GHz(8bit并行)時(shí)鐘等。

一個(gè)SerDes通常還需要調(diào)試能力,例如偽隨機(jī)碼劉產(chǎn)生和比對(duì),各種環(huán)回測試,控制狀態(tài)寄存器以及訪問接口,LOS檢測,沿途測試等。

串行器解串器

串行器(Serializer)把并行信號(hào)轉(zhuǎn)化為串行信號(hào),解串器(Deserializer)把串行信號(hào)轉(zhuǎn)化為并行信號(hào),一般地,并行信號(hào)為8/10bit或者16/20bit寬度,串行信號(hào)為1bit寬度(也可以分階段串行化,如8bit->4bit->2bit->1bit以降低equalizer的工作頻率)。采用擾碼(scrambled)的協(xié)議和SDH/SONET,SMPTE SDI使用8/16bit的并行寬度,如PCI-Express采用8B/10B編碼的協(xié)議,GbE使用10bits/20bits寬度。

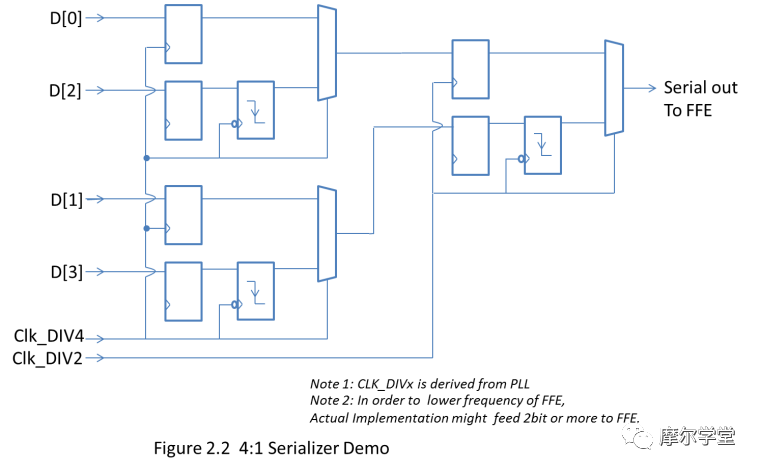

一個(gè)4:1的串行器圖下圖2.2所示.8:1或16:1的串行器采用類似的方法實(shí)現(xiàn)。在實(shí)現(xiàn)時(shí),為了降低均衡器的工作頻率,串行器會(huì)先把并行數(shù)據(jù)變?yōu)?bit,送給均衡器濾波,最后一步再做2:1串行化。

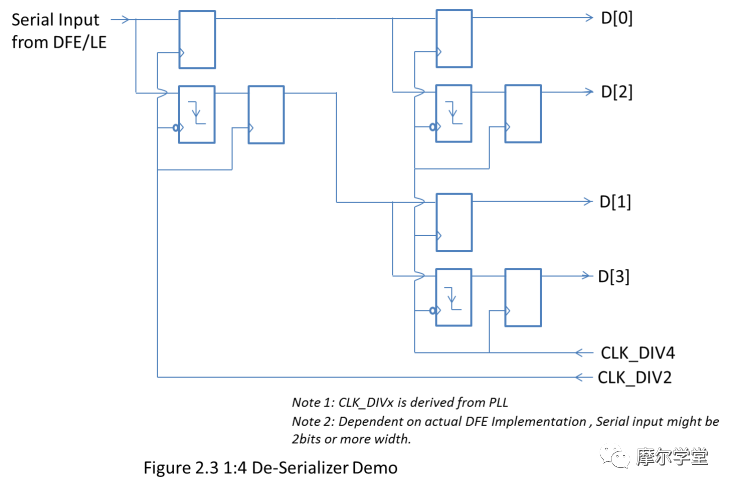

一個(gè)1:4的解串器如圖2.3所示,8:1或16:1的解串器采用類似的實(shí)現(xiàn)。實(shí)現(xiàn)時(shí),為了降低均衡器的工作頻率,均衡器工作在DDR模式下,解串器的輸入是2bit或者更寬。

串行器解串器的實(shí)現(xiàn)采用雙沿DDR的工作方式,利用面積換速度的策略,降低了電路中高頻率電路的比例,從而降低了電路的噪聲。

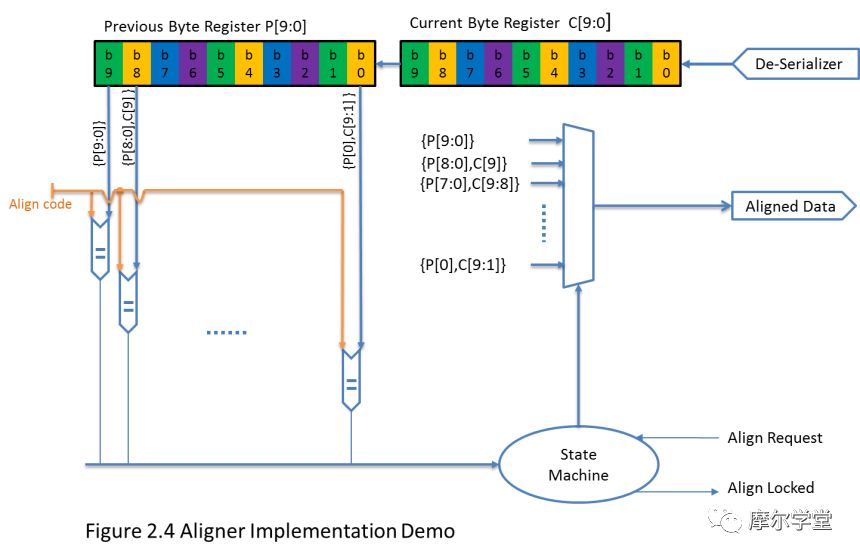

接收方向除了解串器以外,一般還有對(duì)齊功能邏輯(Aligner)。相對(duì)SerDes發(fā)送端,SerDes接收端起始工作的時(shí)刻是任意的,接收器正確收到的第一個(gè)bit可能是發(fā)送并行數(shù)據(jù)的任意bit位置。因此需要對(duì)齊邏輯來判斷從什么bit位置開始,以組成正確的并行邏輯。對(duì)齊邏輯通過在串行數(shù)據(jù)流中搜索特征碼字(Alignment Code)來決定串并轉(zhuǎn)換的起始位置。比如8B/10B編碼的協(xié)議通常用K28.5(正碼10‘b1110000011,負(fù)碼:10’b0001111100)來作為對(duì)齊字。圖2.4為一個(gè)對(duì)齊邏輯的演示。通過滑窗,逐bit比對(duì),比找到對(duì)起碼(Align-Code)的位置,經(jīng)過多次在相同的位置找到對(duì)起碼之后,狀態(tài)機(jī)鎖定位置并選擇相應(yīng)的位置輸出對(duì)齊數(shù)據(jù)。

發(fā)送均衡器(Tx Equalizer)

SerDes信號(hào)從發(fā)送芯片到達(dá)接收芯片所經(jīng)過的路徑成為信道(Channel),包括芯片封裝,PCB總線,過孔,電纜,連接器等元件。從頻域上看,信道可以簡化為一個(gè)低通濾波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止頻率,就會(huì)一定程度上損傷信號(hào)。均衡器的作用就是不讓信道對(duì)信號(hào)的損傷。

發(fā)送端的均衡器采用FFE(Feed Forward Equalizers)結(jié)構(gòu),發(fā)送端的equalizer也稱作加重器(emphasis).加重分為去加重(de-emphasis)和預(yù)加重(pre-emphasis)。de-emphasis降低差分信號(hào)的擺幅(swing).Pre-emphasis增加差分信號(hào)的擺幅。FPGA大部分使用de-emphasis的方式,加重越強(qiáng),信號(hào)的平均幅度就越小。

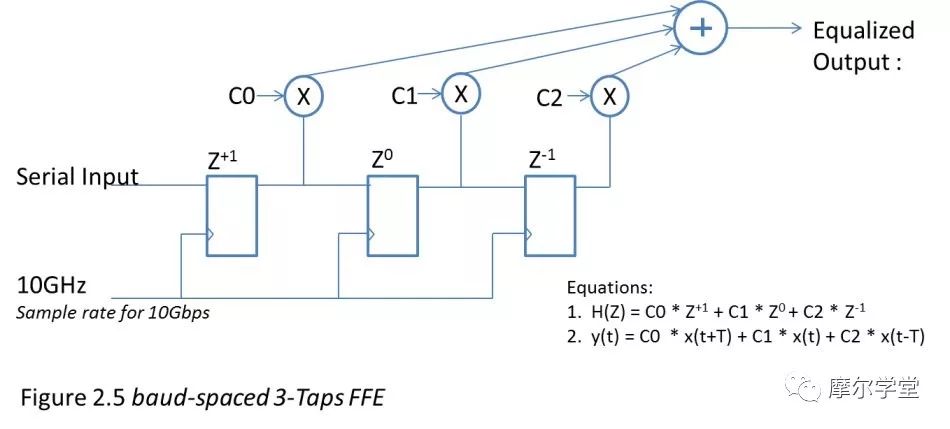

發(fā)送測均衡器設(shè)計(jì)為一個(gè)高通濾波器(HPF),大致為信道頻響H(f)的反函數(shù),F(xiàn)FE(Feed Forward Equalization 前行反饋均衡)的目標(biāo)是讓到達(dá)接收端的信號(hào)為一個(gè)干凈的信號(hào),F(xiàn)FE的實(shí)現(xiàn)方式有很多,典型的例子如下圖2.5所示:

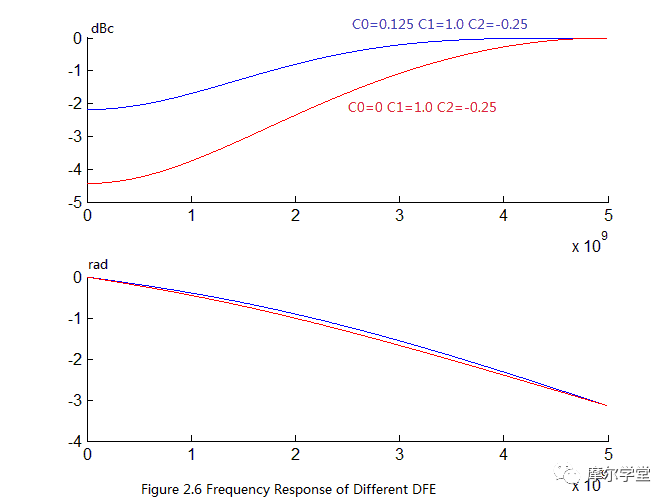

調(diào)節(jié)濾波器的系數(shù)可以改變?yōu)V波器的頻響,以補(bǔ)償不同的信道特性,一般可以動(dòng)態(tài)配置。以10Gbps線速率為例,圖2.6為DFE頻率響應(yīng)演示,可以看到對(duì)于C0 = 0, C1 = 1, C2 = -0.25的配置,5GHz處高頻增益比低頻區(qū)域高出4dB,從而補(bǔ)償信道對(duì)高頻頻譜的衰減。

采樣時(shí)鐘的頻率限制了這種FFE,最高只能補(bǔ)償?shù)紽s/2(上例中Fs/2 = 5GHz)。根據(jù)采樣定理,串行數(shù)據(jù)里的信息都包含在5GHz以內(nèi),從這個(gè)角度看也就足夠了。如果要補(bǔ)償Fs/2以上的頻率,就要求DDE高于Fs的工作頻率,或者連續(xù)時(shí)間域?yàn)V波器(Continuous Time FFE).

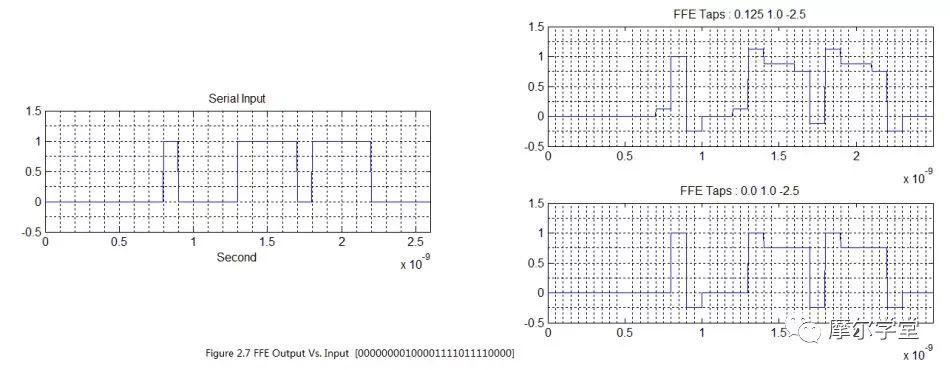

圖2.7為DFE時(shí)序?yàn)V波效果的演示,以10Gbps線速率為例,一個(gè)UI = 0.1 ns = 100 ps.演示的串行數(shù)據(jù)碼流為二進(jìn)制[00000000100001111011110000].

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605996 -

PCI

+關(guān)注

關(guān)注

4文章

671瀏覽量

130473 -

總線接口

+關(guān)注

關(guān)注

0文章

83瀏覽量

30782 -

SerDes

+關(guān)注

關(guān)注

6文章

201瀏覽量

35043 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

453瀏覽量

28664

原文標(biāo)題:深入理解SerDes系列之一

文章出處:【微信號(hào):moorexuetang,微信公眾號(hào):摩爾學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

GMII、SGMII和SerDes的差異總結(jié)

請(qǐng)問6678中的srio的serdes和以太網(wǎng)的serdes是共用還是各自有自己的serdes?

主serdes和奴隸serdes,如果我使用主人,奴隸能使用嗎

SerDes是怎么工作的

參考時(shí)鐘對(duì)SERDES性能的影響

Cadence與是德科技在PAM4領(lǐng)域深度合作

SERDES的優(yōu)勢 SERDES演變的看法

介紹一種采用光SerDes而非電SerDes的高速收發(fā)器

為什么我們需要SERDES?SERDES的優(yōu)點(diǎn)有哪些?

汽車以太網(wǎng)發(fā)明人押寶SerDes!一文詳解車載SerDes技術(shù)

SerDes是怎么設(shè)計(jì)的?(一)

SerDes是怎么設(shè)計(jì)的?(一)

評(píng)論