層次化設(shè)計適當(dāng)下非常流行的設(shè)計思路,隨著芯片的規(guī)模越來越大,fullchip的數(shù)據(jù)量和復(fù)雜度和過去已經(jīng)不能同日而語了,無論是工具的runtime還是QoR,直接完成full-chip的工作越來越不現(xiàn)實。所以,在這里,就需要引入 層次化的設(shè)計(hierarchy design) 的概念,

從芯片的規(guī)劃開始,層次化的理念貫穿整個設(shè)計流程,下面的各個設(shè)計方面都會受到不同程度的影響

RTL

UPF

verification

DFT

Timing constraint

synthesis

EC

layout

STA

stream-out

layout verification

Power analysis

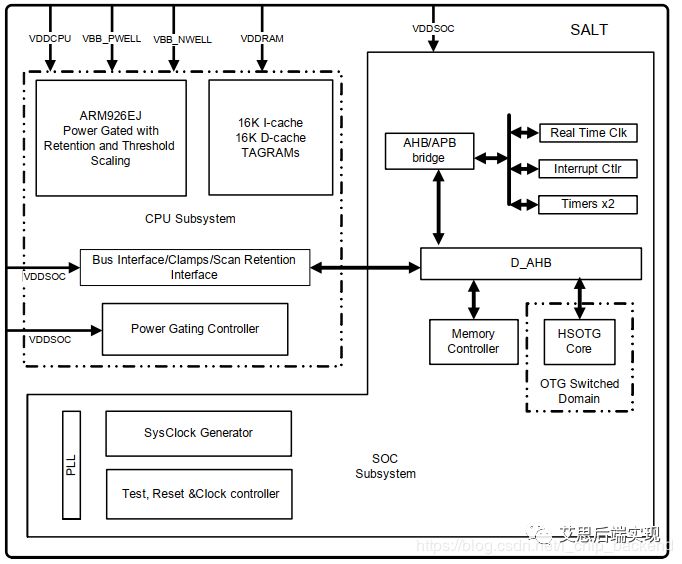

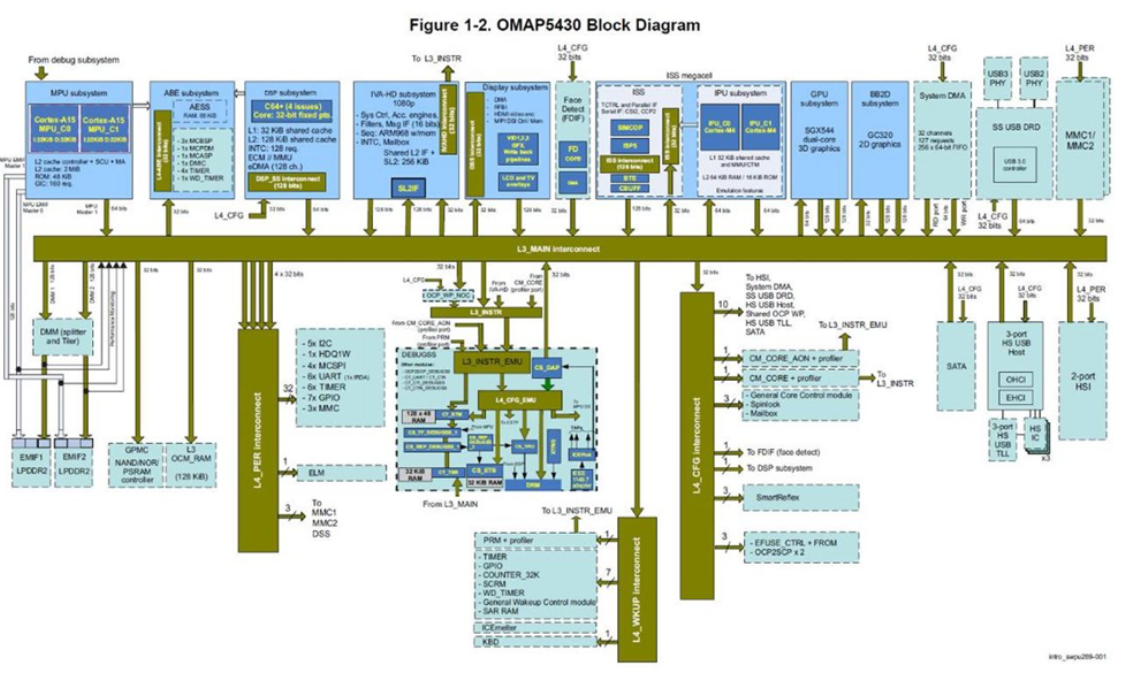

一個項目的開始,需要根據(jù)實際的需要確定層次,這主要是基于模塊功能規(guī)模,一起來看下面這個實例

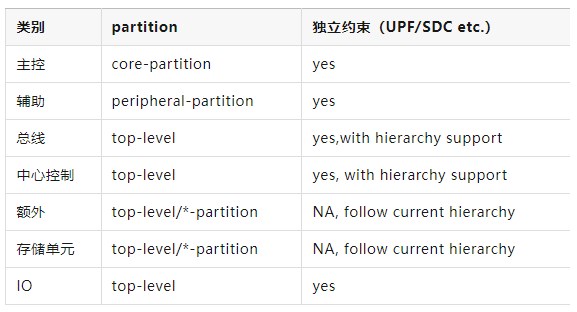

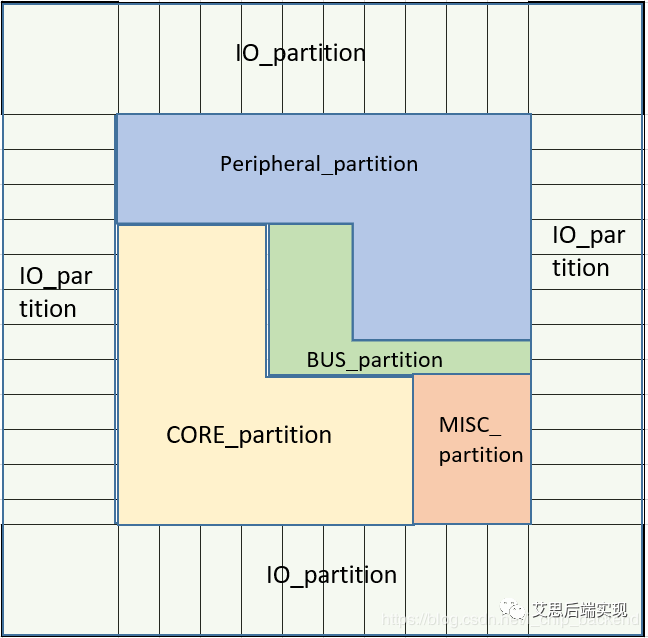

可以看出,從整個SOC的設(shè)計當(dāng)中,主要的partition分割是兩種,top和none-top。理論上講,所有的none-top,互相之間都沒有依賴關(guān)系(dependency),除非它本身也是一個小top,具體可見下面的示例:

這里的top和sub-top_1就是所謂的hierarchy design,在一個芯片里邊,top通常只有一個,但是可能會有多個sub-top,甚至是sub-sub-top,這取決于芯片層次化的深度和芯片的復(fù)雜度。可以預(yù)見,層次化越多,單個partition的復(fù)雜度會降低,但是給top的partition劃分帶來了更多的工作量,譬如

UPF

SDC

physical partition boundary

還有一個影響就是dependency,所有的sub-top,都和top一樣,在后端實現(xiàn)的時候(synthesis/layout),任何的top的后端工作,都需要sub partition的支持,譬如上圖,要想開始sub-top1的synthesis,就必須先要完成 sub_par_1_1,sub_par_1_2,sub_par_1_3的綜合工作。

這就是runtime的瓶頸。實際項目中,為了減少這方面的影響,通常都會有一些變通的手段,來快速支持頂層設(shè)計,這個小技巧的具體細(xì)節(jié),也會在本系列文章里邊提及。

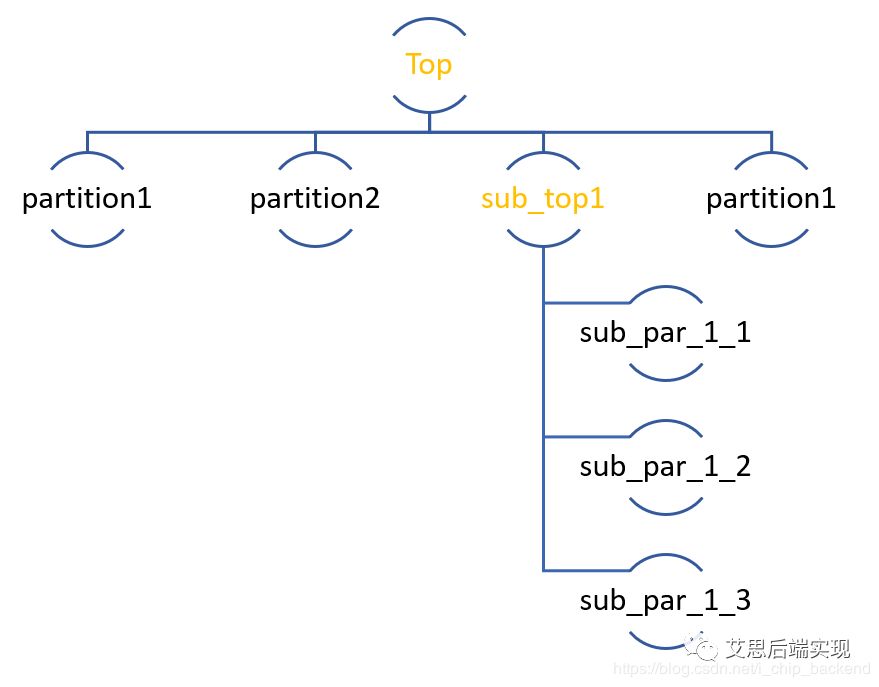

業(yè)界里邊還有一種更為前衛(wèi)的partition的設(shè)計,被稱為abut-partition的設(shè)計,簡單的講就是沒有top的概念,所有的partition都是完全貼合的,譬如下面這個floorplan的partition的框圖

這種架構(gòu)更為簡練,所有的設(shè)計全部都推到了partition,從物理實現(xiàn)上來講,top level已經(jīng)不包含任何的leaf cell,所有的存在就是一些連線關(guān)系、PG、terminal以及co-design routing了,這種極簡的abut設(shè)計有其優(yōu)越性,也有一些限制。

一個完整的層次化設(shè)計,在代碼設(shè)計階段,就應(yīng)該樹立層次化的理念。這里邊主要由以下幾個考量

簡化大規(guī)模設(shè)計的必經(jīng)之路

后端實現(xiàn)的真實需求

驗證和設(shè)計的一致性

相關(guān)配套、支持文件的參照點(SDC、UPF等等)

從架構(gòu)入手,合理分布RTL的層次結(jié)構(gòu),讓整個設(shè)計看起來張弛有道。這個思路體現(xiàn)如下

前端設(shè)計人員按照下面的思路過程來設(shè)計代碼

完成inst1的模塊代碼設(shè)計

完成inst1的內(nèi)部連線

完成inst2的模塊代碼設(shè)計

完成inst2的內(nèi)部連線

完成top-level的模塊代碼設(shè)計

完成top-level的連線

可以看到,這里邊涉及了三個部分的設(shè)計

inst1

inst2

top-level

通常來講,合理的分配各個模塊可以加速full-chip的收斂。從上面的例子可以看出,top-level的東西比較簡單,只有一個控制邏輯和PAD,主要的功能都在子模塊里邊,這樣的好處是非常明顯的

子模塊的實際內(nèi)容多,但是總體規(guī)模不會很大,綜合和版圖的可控性會很好

相互關(guān)聯(lián)密切的功能IP封裝在一個模塊里,有利于時序收斂和后端工具優(yōu)化

top-level的主要用途就是穿線,以及中心控制和PAD等等,有利于整體功能布局的規(guī)劃,主要精力要放到interface的時序上,以及可繞通性。

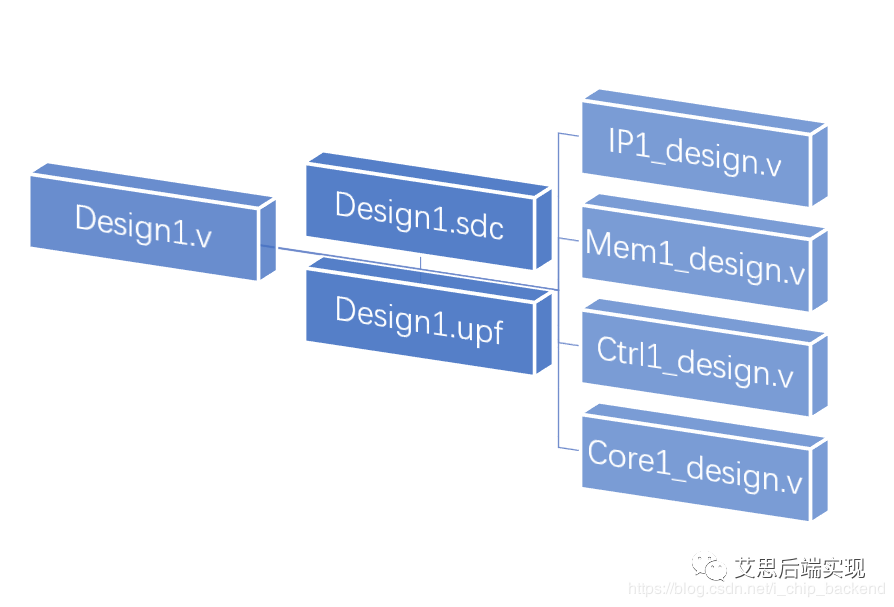

每一個模塊都有一套自己獨立的文件結(jié)構(gòu),譬如inst1對應(yīng)的是design1,整個design1的文件架構(gòu)類似如下:

有了這些文件,design1的綜合就可以開始了。綜合的流程通常比較簡單,這里不做過多的討論,基本流程可以參見下面的列表

HDL analysis 和 elaboration

read_sdc和read_upf 以及一些基礎(chǔ)配置

運行compile_ultra和DFT insertion

創(chuàng)建Block Abstraction view

生成DDC和網(wǎng)表

重要的第四步時一定要執(zhí)行的,這里生成了后面層次化設(shè)計的重要信息。

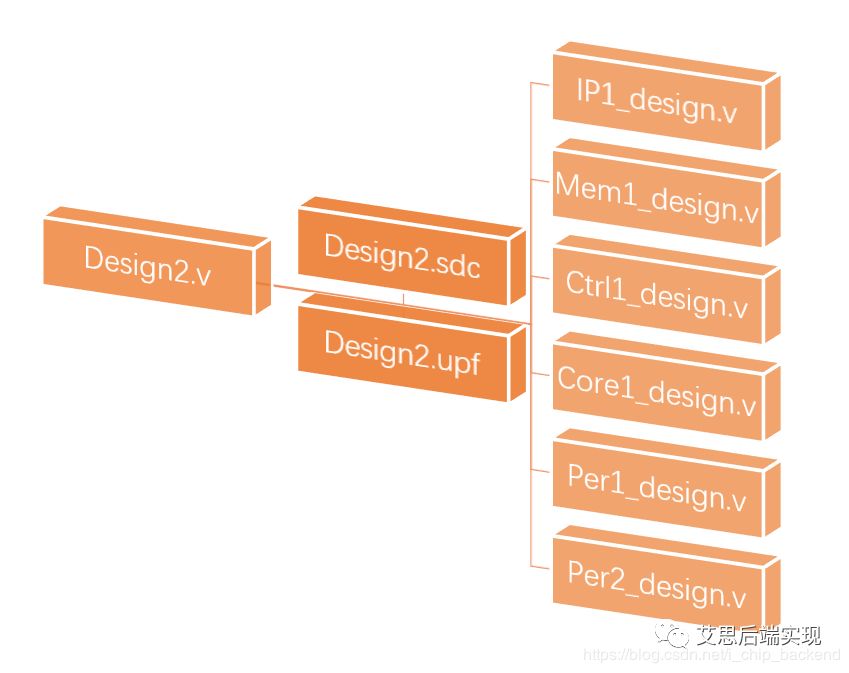

對應(yīng)的,這里也列一下inst2(design2)的文件目錄結(jié)構(gòu)

使用綜合器,分別可以得到下面的文件

design1.ddc 和 design1.v

design2.ddc 和 design1.v

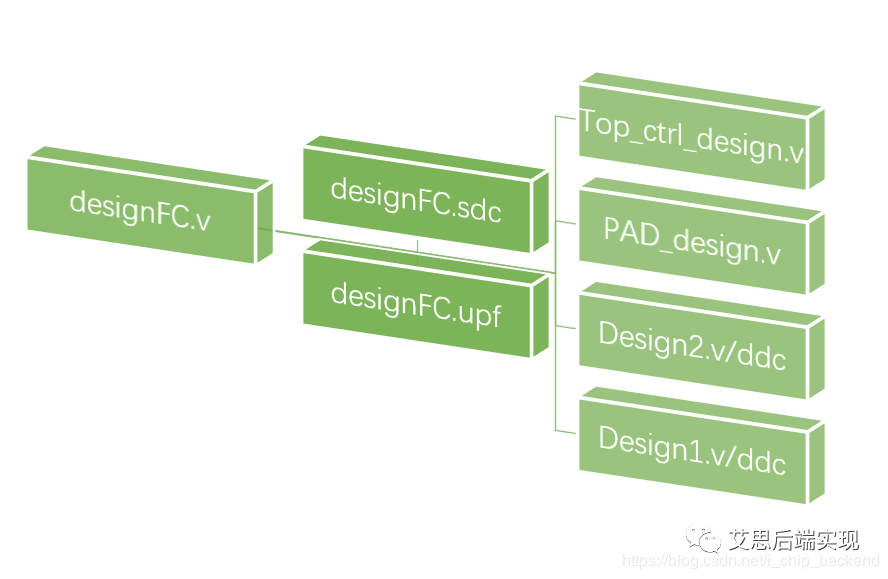

基于不同的DCT/DCG環(huán)境,可以開始根植于如下目錄結(jié)構(gòu)的頂層綜合

頂層綜合的思路會有一些不同,具體流程如下

配置block implementation的狀態(tài)

讀入底層帶有Block Abstraction的DDC(不要讀入子模塊netlist,會導(dǎo)致非常多的困惑),工具回顯如下例

HDL analysis 只分析top-level的verilog,譬如:top_ctrl_design.v、PAD_design.v 、designFC.v

elaboration的時候,一定要注意一下子模塊的鏈接狀態(tài),保證模塊信息都可以被正確掛載進來

在保證link無誤的情況下,讀入designFC.sdc和designFC.upf,運行compile_ultra和DFT insertion

生成DDC和網(wǎng)表,完成top-level的綜合

對應(yīng)的,在做層次化的設(shè)計的時候, 需要注意下面的事項:

調(diào)用底層模塊的時候,一定要使用帶有block Abstraction的DDC,DDC里邊包含了block的

時序約束信息

UPF信息

時鐘結(jié)構(gòu)信息

邊界時序信息

top-level的UPF只有頂層的low power需求

頂層的LS、ISOLATION的需求,如果被約束的cell在頂層

頂層和block的PG連接關(guān)系

top-level的SDC包含了整個top-level和block-level的時序約束

頂層的SDC一定要和block的SDC,在block級別呈現(xiàn)出高度的一致性,譬如純粹block 內(nèi)部的MCP、false path等等

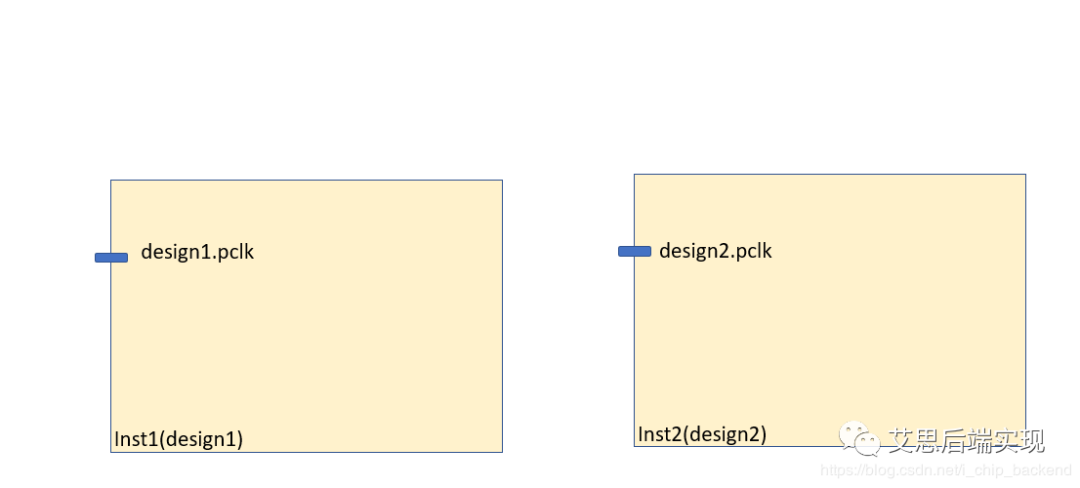

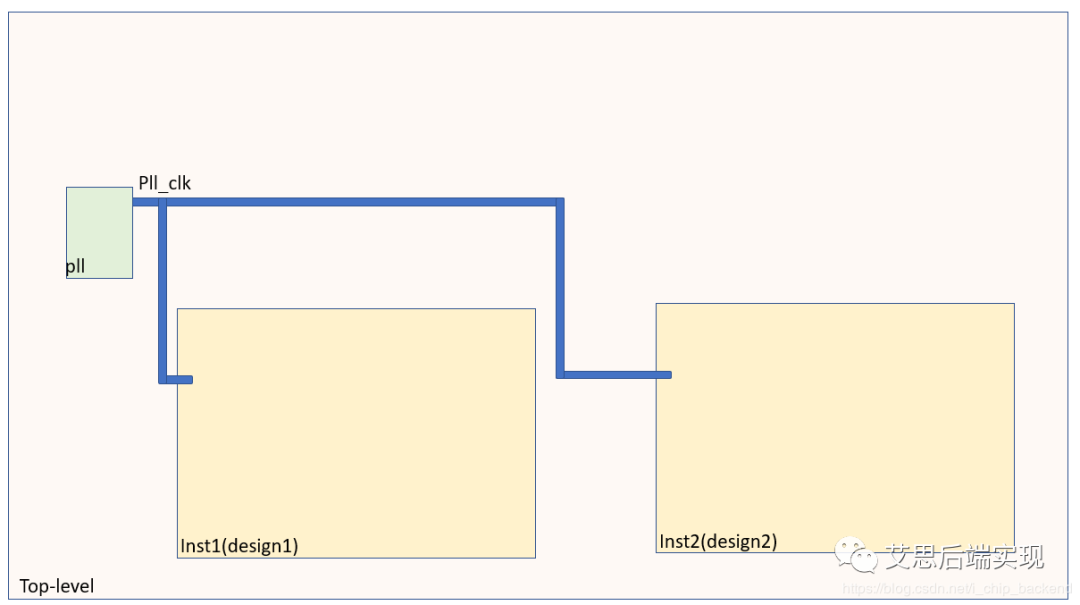

如果時鐘的源頭在頂層,block級別的clock無需二次聲明,譬如下面示例

在design1/desing2綜合的時候,分別在各自的sdc里邊定義pclk,如果把視角放到頂層,那么畫風(fēng)是這樣的

可以看到,從toplevel來看的話,以前的design1/design2的pclk,其實都是從top-level的pll驅(qū)動的,在top-level構(gòu)建SDC的時候,只需要生命pll的clock就可以了(Pll_clk),剩下的就交給工具自動衍生。

寫到這里,相信讀者們對層次化設(shè)計流程有一個比較具體的了解了。

審核編輯:劉清

-

DDR

+關(guān)注

關(guān)注

11文章

715瀏覽量

65528 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1028瀏覽量

55008 -

SoC芯片

+關(guān)注

關(guān)注

1文章

617瀏覽量

35040 -

PHY

+關(guān)注

關(guān)注

2文章

305瀏覽量

51864 -

SDC

+關(guān)注

關(guān)注

0文章

49瀏覽量

15581

原文標(biāo)題:芯片中的層次化的設(shè)計(hierarchy design)

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

使用層次式電路時,發(fā)現(xiàn)Descend Hierarchy是灰色的,不可選

【AD問答 11】 怎么創(chuàng)建層次化的原理圖形式

層次式電路設(shè)計與平坦式電路設(shè)計的區(qū)別

“按層次結(jié)構(gòu)使用”中的LUT數(shù)量不正確

映射報告怎么按層次結(jié)構(gòu)使用

包含層次結(jié)構(gòu)窗口完全空白

FPGA編輯器中的塊層次結(jié)構(gòu)不正確

在Vivado 2015.2塊設(shè)計上打開子層次結(jié)構(gòu)彈出一個新的Block Design窗口

層次結(jié)構(gòu)設(shè)計是否意味著將一個大模塊分成幾個子模塊?

層次化設(shè)計方法講解

談?wù)?/b>汽車芯片安全(下篇)

芯片設(shè)計復(fù)雜性處理之層次結(jié)構(gòu)概念分析

談?wù)勑酒械膶哟位脑O(shè)計(hierarchy design)

談?wù)勑酒械膶哟位脑O(shè)計(hierarchy design)

評論