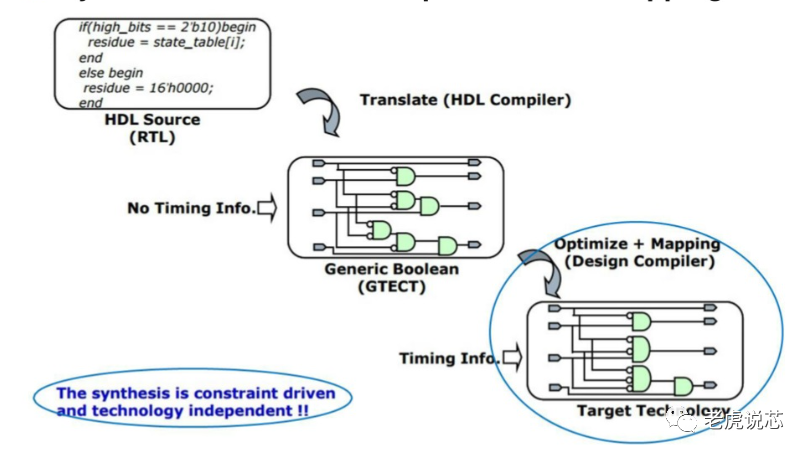

什么是Logic Synthesis?Logic Synthesis用于將輸入的高級語言描述(如HDL、verilog)轉換為門級電路的網絡表示。在這一階段,我們的目標是根據設計規范和約束,生成滿足性能目標和面積要求的優化電路。

Synthesis = translation + optimization + mapping

圖片來源:NTU

Synthesis的目標:通過Logic Synthesis,我們能夠實現以下目標:

最小化電路的面積:在滿足性能需求的前提下,盡可能減少電路所占用的芯片面積,以降低成本。

最大化電路的性能:通過優化電路結構和邏輯功能,最大化電路的速度。這涉及到對組合邏輯的優化、時序路徑的優化等。

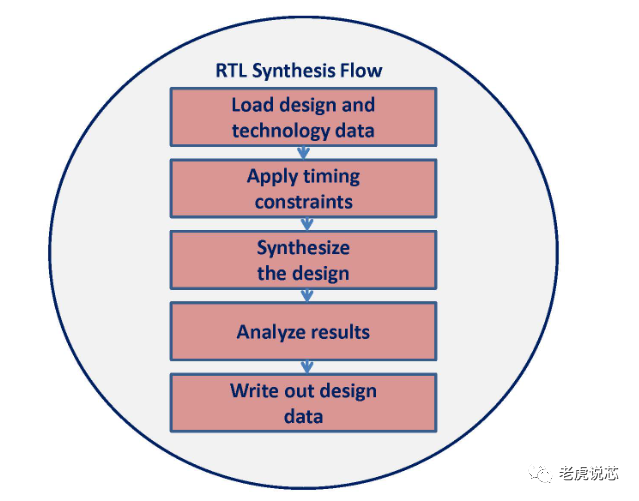

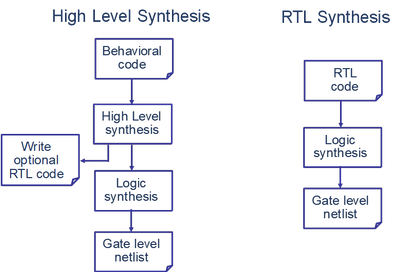

Synthesis的流程:

圖片來源:vlsiguru

a. 輸入文件準備:這包括HDL文件和庫文件的準備。HDL文件是我們的設計描述,而庫文件包含了各種邏輯元素和其性能特征。通過閱讀這些文件,我們可以了解電路的功能和特性。

b. 硬件約束條件:我們需要指定一些約束條件,比如時序要求、時鐘頻率等,以確保電路性能的正確性和穩定性。

c. Logic Synthesis:邏輯綜合工具將HDL文件轉換為門級網表。在這一步中,綜合工具會盡可能地進行邏輯和結構優化,以滿足性能和面積要求。

d. 優化和時序分析:在這個階段,我們將通過優化技術來改善電路的性能,并進行時序分析,以確保電路滿足預定的時序要求。

e. 報告和生成文件:最后,我們會生成各種報告,以便評估電路的性能和優化效果,并生成相應的文件,如門級網表、時序約束文件等。

Synthesis的輸入輸出:Logic Synthesis的輸入包括HDL文件和庫文件。HDL文件是我們的設計描述,可以是Verilog、VHDL等。庫文件則包含了電路元件的特性和延時信息。輸出是邏輯綜合工具生成的門級網表和其他輔助文件。

HDL文件和庫文件:HDL文件是我們設計的描述,它類似于編程語言,用于描述電路的邏輯功能和結構。而庫文件則包含了各種邏輯元素和其特性,如AND、OR門和其傳輸延時。

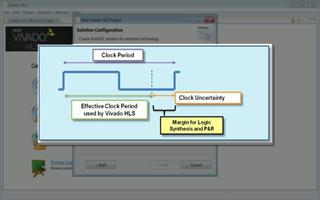

Constraints條件:在Logic Synthesis中,我們可以指定一些約束條件,以確保電路滿足性能要求和時序要求。這些約束條件可以包括時鐘頻率、時序限制、電源噪聲約束等。

Timing paths(時序路徑):電路中的信號傳輸路徑,通過時鐘邊沿的邏輯延時。在數字電路中,信號需要從一個邏輯塊傳輸到另一個邏輯塊,而這些傳輸路徑的延時就是時序路徑。可以類比為交通路線,信號就像車輛一樣在路線上行駛,而時序路徑則是車輛所需的時間,取決于路況和速度。

Timing Constraints(時序約束):指定電路中某些信號的最大或最小延時要求。時序約束是為了確保電路的工作時間滿足設計要求而設定的條件。類比為一個人規定的時間表,確保不同的任務在規定的時間內完成。比如,你有一個任務需要在10分鐘內完成,那么時序約束就是告訴你必須在10分鐘內完成,否則會超時。

IO Timing(輸入/輸出時序):確保輸入和輸出信號滿足指定的時序要求。這是指輸入和輸出信號在電路中所需的時間。它確保輸入信號正確地經過電路處理,并且輸出信號在預期的時間內提供給其他組件使用。可以類比為快遞服務,你將包裹寄出后,需要在規定的時間內送到收件人手中,以確保準時送達。

Area(面積):電路所占用的芯片表面積。在電路設計中,面積指的是電路所占用的芯片表面積。可以類比為房子的占地面積,一間房子占地越大,那么整個房子所需要的土地就越多。同樣,如果一個電路所需的面積越大,那么芯片的尺寸就會增加。

Combinational Delay(組合延時):組合邏輯電路的延時,即輸入到輸出的傳輸延時。在數字電路中,組合延時是指信號從輸入到輸出經過組合邏輯電路所需要的時間。可以類比為做飯的時間,將食材放入鍋中后,需要經過一定的時間才能出鍋。同樣,將輸入信號輸入到組合邏輯電路中,經過一定的時間,輸出信號才會出現。

設計環境、編譯策略和優化技術:在Logic Synthesis中,我們需要設置適當的設計環境,選擇合適的編譯策略和優化技術來實現設計目標。這包括優化技術、邊界優化、非組合元素優化等。

生成報告和文件:最后,我們會生成各種報告,如時序報告、面積報告等,以評估電路的性能和優化效果。我們還會生成相應的文件,如門級網表、時序約束文件等。

通過Logic Synthesis,我們能夠將高級語言描述的設計轉化為可以在芯片上實現的門級電路網絡。通過了解Logic Synthesis的流程、輸入輸出、約束條件和優化技術,我們能夠更好地應用這一技術,并對電路的性能進行分析和優化。

審核編輯:劉清

-

電源噪聲

+關注

關注

3文章

152瀏覽量

17517 -

時序約束

+關注

關注

1文章

115瀏覽量

13457 -

HDL語言

+關注

關注

0文章

47瀏覽量

8956 -

門級電路

+關注

關注

0文章

15瀏覽量

1998 -

時序路徑

+關注

關注

0文章

12瀏覽量

1412

原文標題:什么是Logic Synthesis?

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADVANCED ASIC CHIP SYNTHESIS

/*synthesis atera_chip_lc=“@pin”*/注釋里也能加pin腳約束嗎

float array synthesis創建兩個32位的存儲器

IO Planning (PlanAhead) post-synthesis時報錯

【工程源碼】【Modelsim常見問題】Analysis and Synthesis should be completed

Synthesis And Optimization Of

Digital Frequency Synthesis Demystified

Getting Started with Vivado High-Level Synthesis

新思科技推出下一代Design Compiler,進一步強化Synthesis領先地位

高層次綜合技術(High-level synthesis)的概念

Vivado Synthesis模塊化的設計方法

如何在Post Synthesis工程中加入XCI文件

什么是Logic Synthesis?Synthesis的流程

什么是Logic Synthesis?Synthesis的流程

評論