具有Cache的計算機,當CPU需要進行存儲器存取時,首先檢查所需數據是否在Cache中。如果存在,則可以直接存取其中的數據而不必插入任何等待狀態,這是最佳情況,稱為高速命中;

當CPU所需信息不在Cache中時,則需切換存取主儲器,由于速度較慢,需要插入等待,這種情況稱高速未命中;

在CPU存取主存儲器的時候,按照最優化原則將存儲信息同時寫入到Cache中以保證下次可能的高速緩存命中。

因此,同一數據可能同時存儲在主存儲器和Cache中。同樣,按照優化算法,可以淘汰Cache中一些不常使用的數據。

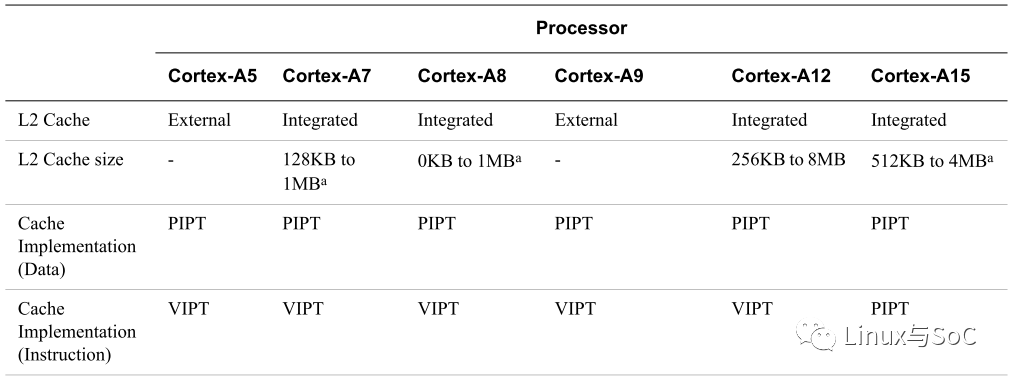

傳統的Socket架構通常采用兩級緩沖結構,即在CPU中集成了一級緩存(L1Cache),在主板上裝二級緩存(L2 Cache),而SlotⅠ架構下的L2 Cache則與CPU做在同一塊電路板上,以內核速度或者內核速度的一半運行,速度比Socket下的以系統外頻運行的L2 Cache更快,能夠更大限度發揮高主頻的優勢,當然對Cache工藝要求也更高。

?CPU首先在L1 Cache中查找數據,如找不到,則在L2Cache中尋找。

?若數據在L2 Cache中,控制器在傳輸數據的同時,修改L1Cache;

?若數據既不在L1 Cache中,又不在L2 Cache中,Cache控制器則從主存中獲取數據,將數據提供給CPU的同時修改兩級Cache。

?K6-Ⅲ則比較特殊,64KB L1 Cache,256KB Full Core Speed L2 Cache,原先主板上的緩存實際上就成了L3 Cache。

根據有關測試表明:

當512K2MB的三級緩存發揮作用時,系統性能還可以有2%10%的提高;

Tri-level成為PC系統出現以來提出的解決高速CPU與低速內存之間瓶頸最為細致復雜的方案;而且,今后Cache的發展方向也是大容。

在主存-Cache存儲體系中,所有的指令和數據都存在主存中,Cache只是存放主存中的一部分程序塊和數據塊的副本,只是一種以塊為單位的存儲方式。

Cache和主存被分為塊,每塊由多個字節組成。

由上述的程序局部性原理可知,Cache中的程序塊和數據塊會使CPU要訪問的內容在大多數情況下已經在Cache中,CPU的讀寫操作主要在CPU和Cache之間進行。

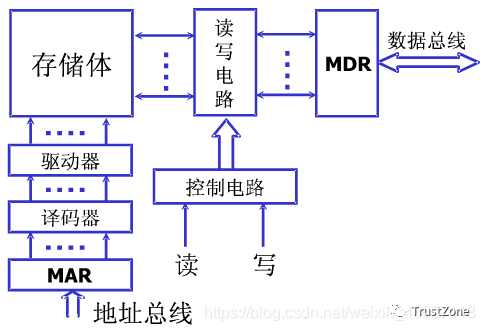

CPU訪問存儲器時,送出訪問單元的地址,由地址總線傳送到Cache控制器中的主存地址寄存器MAR,主存-Cache地址轉換機構從MA獲取地址并判斷該單元內容是否已在Cache中存有副本,如果副本已存在于Cache中,即命中。當命中時,立即把訪問地址變換成它在Cache中的地址,然后訪問Cache。

?存儲體由若跟個存儲單元組成,存儲單元由多個存儲元件組成

?存儲體----存儲單元(存儲一串二進制串)----存儲元件(存儲一個0/1)

?存儲單元:存放一串二進制代碼。

?存儲字:存儲單元中的二進制代碼

?存儲字長:存儲單元中二進制代碼位數。

?存儲單元按照地址進行尋址

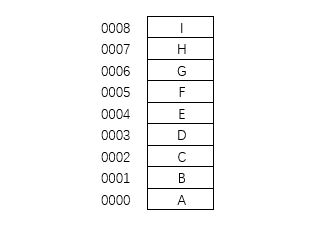

?MAR:存儲器地址寄存器,反應存儲單元個數。保存了存儲體的地址(存儲單元的編號),反應了存儲單元的個數。所以MAR的位數和存儲單元的個數有關。

?MDR:存儲器數據寄存器,反應存儲字長(存儲單元長度)。保存了要送入CPU中的數據或要保存到存儲體中的數據或者剛剛從存儲體中取出來來的數據。這個寄存器的長度和存儲單元的長度相同。

如果CPU要訪問的內容不在Cache中,即不命中,則CPU轉去直接訪問主存,并將包含此存儲單元的整個數據塊(包括該塊數據的地址信息)傳到Cache中,使得以后的若干次對內存的訪問可轉化為對Cache的訪問。

若Cache存儲器已滿,則需在替換控制部件的控制下,根據某種替換算法/策略,用此塊信息替換掉Cache中原來的某塊信息。

之前記得當時面試的時候讓我用golang手寫緩存管理算法,哈哈哈。

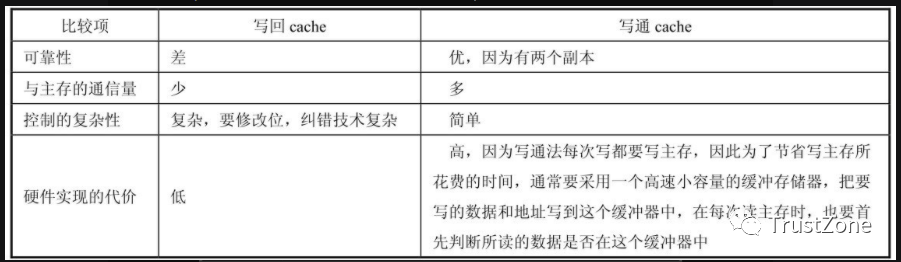

所以,要想提高系統效率,必須提高Cache命中率,而Cache命中率的提高則取決于Cache的映像方式和Cache刷新算法等一系列因素,同時Cache中內容應與主存中的部分保持一致,也就是說,如果主存中的內容在調入Cache之后發生了變化,那么它在Cache中的映像也應該隨之發生相應改變,反之,當CPU修改了Cache中的內容后,主存中的相應內容也應作修改。

-

存儲器

+關注

關注

38文章

7528瀏覽量

164345 -

cpu

+關注

關注

68文章

10904瀏覽量

213023 -

計算機

+關注

關注

19文章

7536瀏覽量

88643 -

Cache

+關注

關注

0文章

129瀏覽量

28433

發布評論請先 登錄

相關推薦

機械硬盤的工作原理是什么

Cache的工作原理

高速緩沖存儲器Cache的原理、設計及實現

cache結構與工作原理

什么是 Cache? Cache讀寫原理

深入理解Cache工作原理

Cache工作原理講解 Cache寫入方式原理簡介

Cache工作原理是什么

Cache工作原理是什么

評論