1.1 FVF BasedLDO

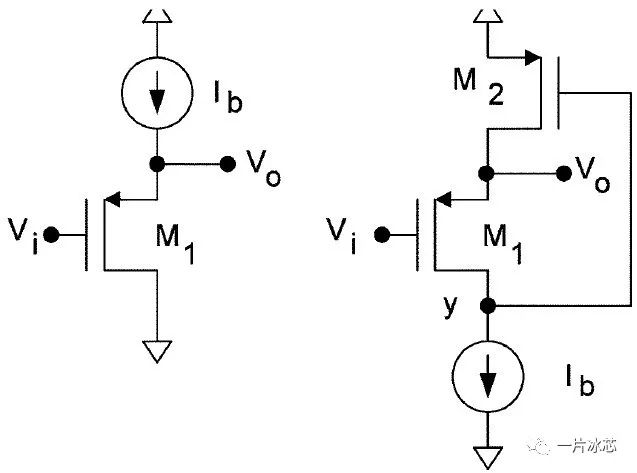

FVF全稱為Flipped Voltage Follower是一種輸出阻抗很低的新型源跟隨器,其擁有更大的電流驅(qū)動能力,相對傳統(tǒng)單管源跟隨器輸出阻抗減小了gm2ro1倍,如圖1所示,其中g(shù)m2為M2管的跨倒,ro1為M1管的小信號電阻 ^[1-2]^ 。

(a)單管源極跟隨器(b)FVF

Fig1. 單管源極跟隨器及FVF源級跟隨器

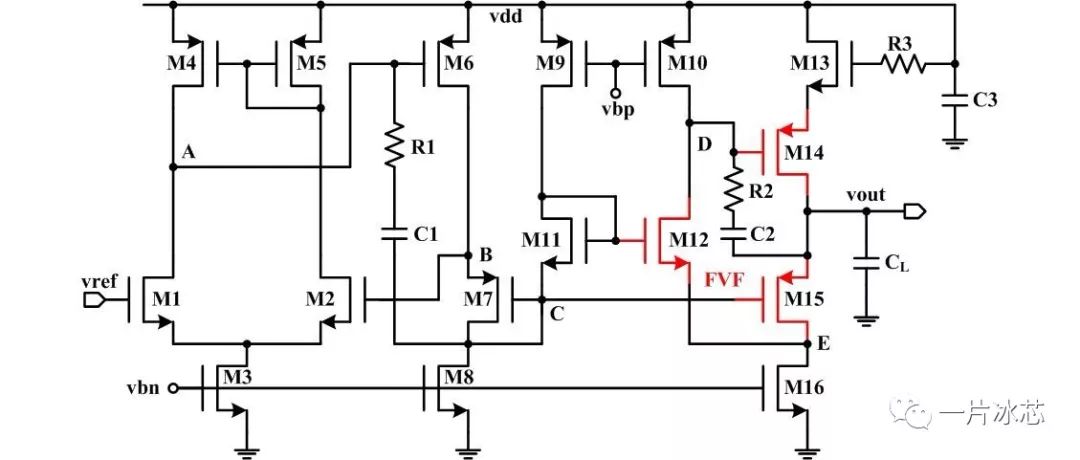

圖1所示簡單FVF結(jié)構(gòu)無法提供較大的環(huán)路增益,這會導(dǎo)致較差的DC 特性,為了提高低頻增益可以采用參考文獻[3]的共源共柵FVF結(jié)構(gòu),圖2是我在項目中設(shè)計的共源共柵FVF LDO。M12為FVF環(huán)路(M14、M15、M12)提供共源共柵級,提高了環(huán)路增益,代價是FVF環(huán)路包含了三個極點(圖2中vout、D、E),因此需要采用密勒補償來保證環(huán)路穩(wěn)定性。

Fig2. 共源共柵FVF LDO

此外,圖2中M13的引入是為了提高PSRR,M1和M2管的length取大可以減小輸出級的噪聲(一般噪聲貢獻較大的管子為運放的輸入對管和電流偏置管),保證穩(wěn)定的前提下CL盡量取大,因為大的CL在環(huán)路帶寬不夠時可以保證輸出級有較好的負載瞬態(tài)跳變調(diào)節(jié)能力,同時可以提高高頻PSRR。

1.2 高PSRR LDO

這邊多說幾句,芯片內(nèi)部電源往往通過外部DC-DC提供,DC-DC內(nèi)部通常會有幾百kHz到幾十MHz的時鐘,并且可能會產(chǎn)生幾mV到幾十mV的電源紋波。在sub-6G FR1 5G通信中Channel Bandwidth高達100MHz,mm-Wave FR2 5G通信中Channel Bandwidth達到400MHz,因此從系統(tǒng)應(yīng)用上講MHz的PSRR也十分重要。

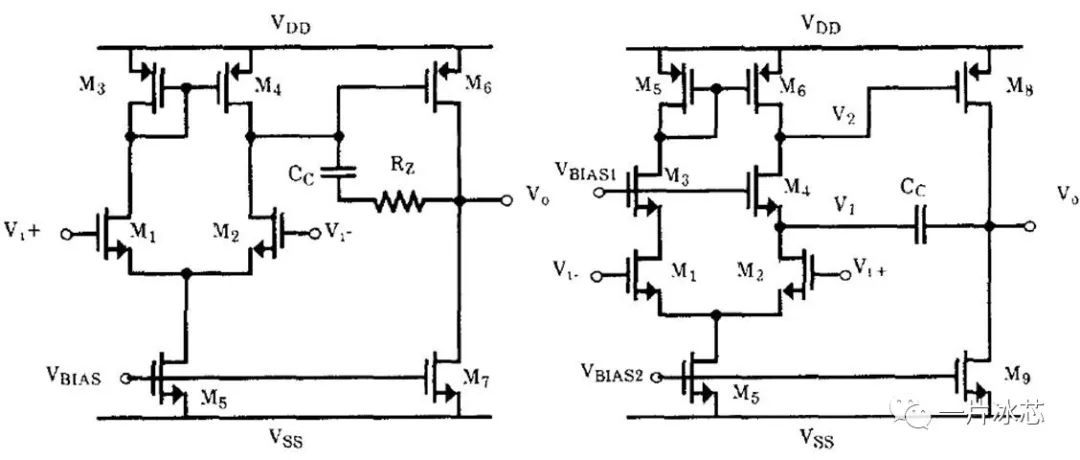

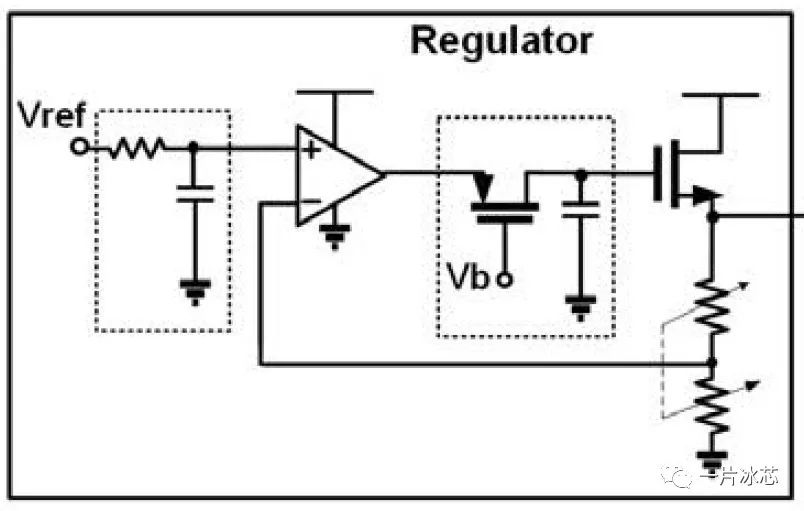

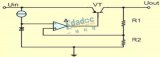

圖3給出了傳統(tǒng)LDO和高PSRR LDO原理圖 ^[4]^ 。將密勒補償電容接在M4管的源極以提高M8管高頻PSRR(低頻PSRR比較容易,通常會卡在高頻處)。

(a)傳統(tǒng)LDO (b)高PSRR LDO

Fig3. 傳統(tǒng)LDO和高PSRR LDO

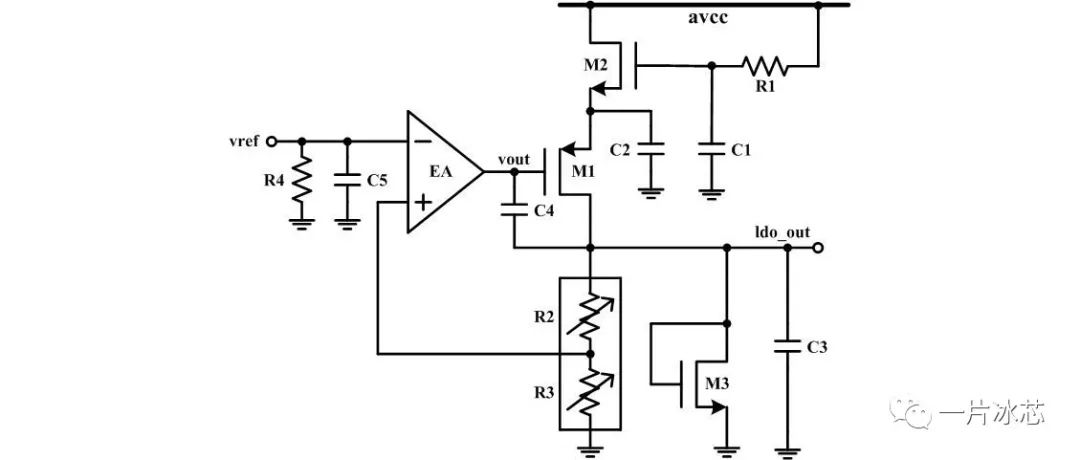

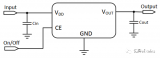

圖4 LDO結(jié)構(gòu)在之前的layout講議中提到過,大電容C2的引入保證在GHz頻率處仍有-20dB的PSRR,高頻PSRR要優(yōu)于圖2的共源共柵FVF結(jié)構(gòu)。

Fig4. 高PSRR LDO

電源到LDO輸出端內(nèi)阻越小,LDO越接近一個理想電壓源,輸出電壓越穩(wěn)定,將功率管由PMOS換成NMOS可將功率管輸出阻抗由ro變?yōu)?/g m ,進一步提高PSRR^[5-6]^,如圖5所示。此外,為了減小N管的Drop電壓,功率管可采用Native管。

Fig5. 高PSRR的N管LDO

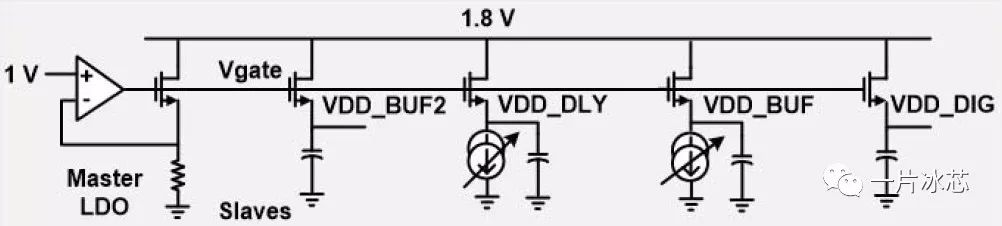

1.3 Replica LDO

基于NMOS LDO特性,Replica LDO更適用于數(shù)字負載,Replica LDO結(jié)構(gòu)如圖6所示。Replica LDO分為Master和Slave級,通常由一個Master產(chǎn)生Vgate電壓,然后接到多個Slave級,通過合理設(shè)置電流比例及負載可以粗略復(fù)制Master的參考電壓,如果負載能接受電壓變化,這種結(jié)構(gòu)問題不大。此外,這種結(jié)構(gòu)輸出級工作在開環(huán)狀態(tài)且采用NMOS做功率管,負載突變時具有較小的undershoot和overshoot。

Fig6. Replica LDO

1.4 耐壓結(jié)構(gòu)LDO

之前項目需要一個3.3V轉(zhuǎn)0.8V的LDO,但用的是22nm先進工藝,里面高壓管最高只能耐1.98V的電壓,拿到這個需求時,真是一萬個頭大,腦海里一堆問題,1.8V的device怎么抗3.3V的電壓啊?基準電壓、mux、buffer、LDO主體電路、triming電路通通需要耐壓結(jié)構(gòu),沒這方面的設(shè)計經(jīng)驗啊。

芯片面積有10mm*10mm,外部單3.3V電源,經(jīng)LDO產(chǎn)生0.8V的電壓做為內(nèi)部的core電源而且是Capless結(jié)構(gòu)。我們還聯(lián)系過法國Dolphin公司(海豚集成)幫我們做,他們是可以做,但沒有Capless結(jié)構(gòu)的IP,讓他們做需要20W美金(真黑)。價格沒談就只能硬著頭皮自己做嘍,期間查了很多資料,方案也修改了多次,萬幸流片測試一把成了,因工作需要這里就不給大家透露具體細節(jié)了,基本思想就是疊管子耐高壓,有這方面需求的可以私信我。

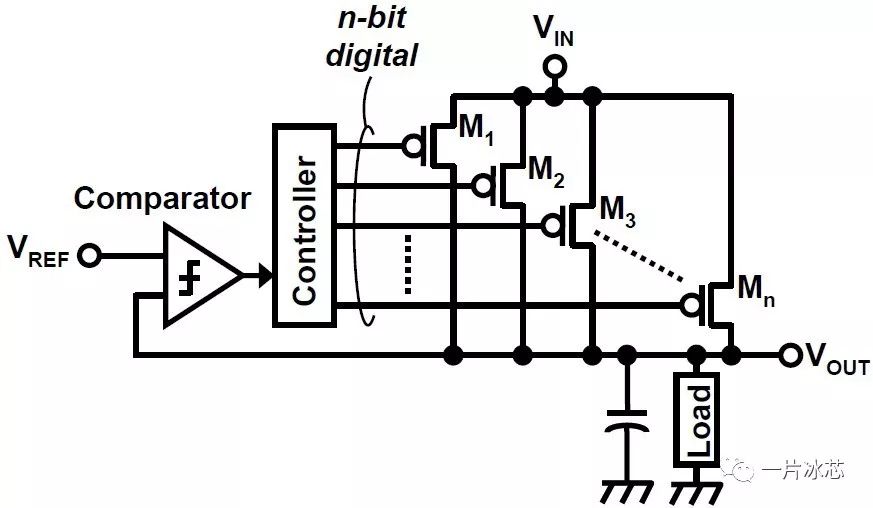

2. 數(shù)字LDO

數(shù)字LDO原理很簡單,把模擬LDO功率管分割成許多功率開關(guān),這些開關(guān)由移位寄存器控制,比較器每個時鐘周期比較Vout和Vref電壓并指示移位寄存器打開或關(guān)斷一個功率開關(guān),結(jié)構(gòu)框圖如圖7所示。

Fig7. 數(shù)字LDO

數(shù)字LDO可以工作在比較低的電壓下,而且方便工藝移植。由于有限的輸出精度,在穩(wěn)定時數(shù)字控制碼會振蕩,這就是所謂的有限周期振蕩(Limit-Cycle Oscillation, LCO)。數(shù)字LDO環(huán)路包含了z域和s域,分析起來較復(fù)雜。

**3. **總結(jié)

①LDO的設(shè)計指標要看你的應(yīng)用,如果是給數(shù)字電源供電,PSRR、noise、電源精度這些都不是特別重要,如果是給VCO供電,那就要小心了,建議PSRR在0100MHz小于-20dB@ 1MHz,noise在1MHz小于20nV/√Hz,LDO基準電壓PSRR在0100MHz小于-30dB@ 1MHz,noise在1MHz小于10nV/√Hz。

②LDO參考電壓一般需要加大的RC濾波,-3dB帶寬要小于你的環(huán)路帶寬。

③采用N管做為功率輸出級可以提高PSRR并減小undershoot和overshoot。

④Replica LDO也挺常用的我就在pll中用過,而且PSRR、undershoot和overshoot確實好,輸出電壓變化也不是那么大。

-

跟隨器

+關(guān)注

關(guān)注

1文章

86瀏覽量

29740 -

輸出電壓

+關(guān)注

關(guān)注

2文章

1122瀏覽量

38295 -

PSRR

+關(guān)注

關(guān)注

0文章

153瀏覽量

39398 -

電源紋波

+關(guān)注

關(guān)注

5文章

209瀏覽量

16409 -

LDO電路

+關(guān)注

關(guān)注

0文章

26瀏覽量

2478

發(fā)布評論請先 登錄

相關(guān)推薦

使用LDO進行設(shè)計的一些鮮為人知的方面

關(guān)于MCU,給研發(fā)提供一些思考吧!

談?wù)?/b>電容的一些基本應(yīng)用及注意事項

介紹一些常用的LDO相關(guān)術(shù)語

談?wù)?/b>對替換電容的一些看法

講述LDO和DC-DC的一些差異

講述LDO和DC-DC的一些差異

談?wù)?/b>void指針的一些妙用

設(shè)計開關(guān)電源的一些關(guān)鍵問題

談?wù)?/b>學(xué)習(xí)單片機究竟該學(xué)習(xí)一些什么

PCB板設(shè)計時如何進行一些權(quán)衡讓PCB的電源分配網(wǎng)絡(luò)合理

有關(guān)Redis的一些思考和理解

談?wù)?/b>開關(guān)電源和LDO電源的一些原理

談?wù)凩DO設(shè)計時的一些思考

談?wù)凩DO設(shè)計時的一些思考

評論