1、SD NAND的布局

SD NAND芯片最好是要靠近host,這樣可以讓走線盡可能的短,減少干擾。

在布局的時候需要盡量避免離host過遠,距離太遠會導致走線過長,容易受到干擾。

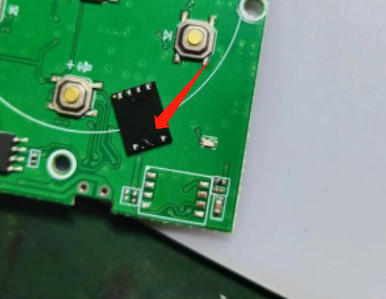

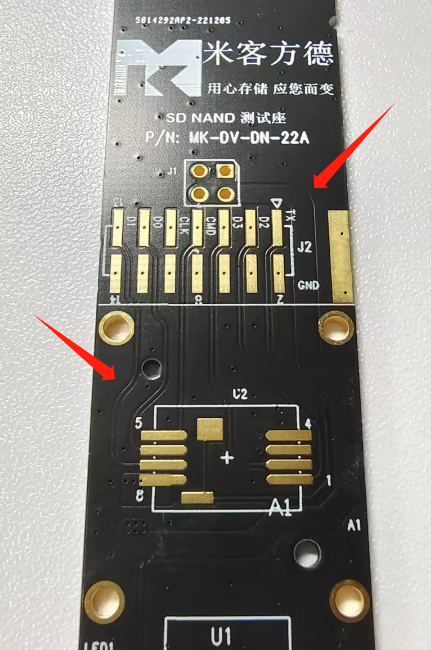

另外,在布局的時候,SD NAND芯片不能放在PCB邊緣,這樣容易導致焊盤脫落,如下圖:

上圖就是芯片放在PCB邊緣,分板和拆板的時候,芯片受到外力導致的焊盤脫落。

2、SD NAND在PCB上的走線要求

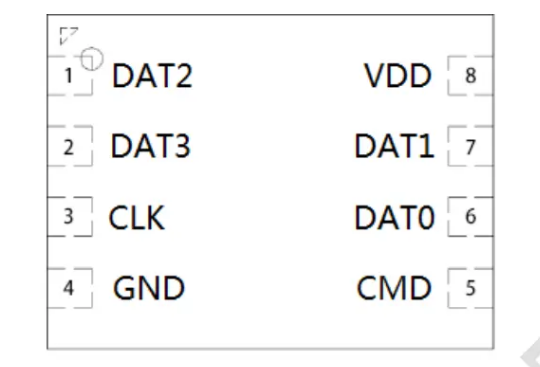

SD NAND一般有8個引腳,

1、VDD和GND的電源走線要求回路盡可能的短,走線需要遠離電感,以防止電磁干擾,另外,SD NAND的電源走線寬度需要能過至少300mA的電流。

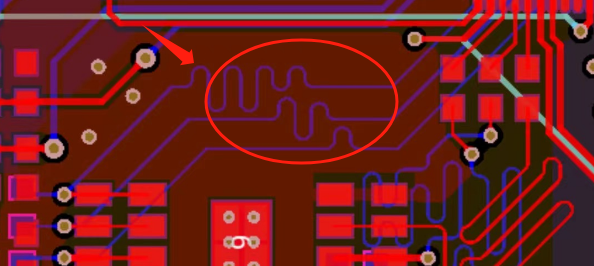

2、DAT0 ~ DAT3四個數據引腳,如果是emmc,則要求長度不能超過7mm,并且要等長走線。而在SD NAND里面,走線長度在15 ~ 18mm左右,當然這個走線是越短也好,在一些要求比較高的情況下,四根DATD數據線可以等長走線,如下圖:

3、CMD和CLK的走線是要求越短越好,并不要求走等長線,像下圖中的這種為了強行等長走線而使CLK走線過長是不支持的,這樣容易會增加CLK受干擾概率。

3、弧度走線

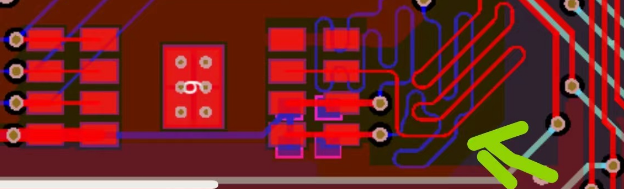

在做一些SD NAND轉接板的時候,走線比較長,是要求弧度走線的,如下圖:

這個是MK-米客方德做的一款SD NAND轉接板,方便測試芯片,板子的走線全部采用的是弧度走線,

實際上存儲行業信號線都要拉弧度處理。

-

pcb

+關注

關注

4326文章

23160瀏覽量

399942 -

NAND

+關注

關注

16文章

1690瀏覽量

136460 -

SD NAND

+關注

關注

0文章

84瀏覽量

1293

發布評論請先 登錄

相關推薦

SD NAND、SPI NAND 和 Raw NAND 的定義與比較

SD NAND、SPI NAND 和 Raw NAND 的定義與比較

SD NAND 概述

這樣設計SD/TF卡的PCB更高效、更可靠!

探索電路板pcb螺旋走線的特點

SD NAND和SPI NAND的區別

PCB板布局與走線設計的核心準則

SD NAND在PCB上的布局和走線要求

SD NAND在PCB上的布局和走線要求

評論