在之前的文章里面介紹了Canny算法的原理和基于Python的參考模型,之后呢在FPGA上完成了Canny算法的實現,可是遇到了時序不收斂的問題,記錄一下。

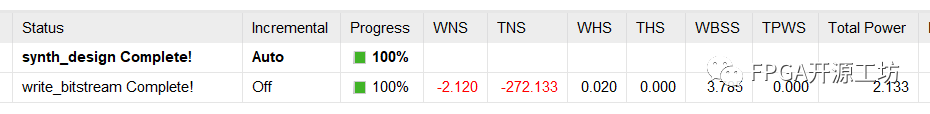

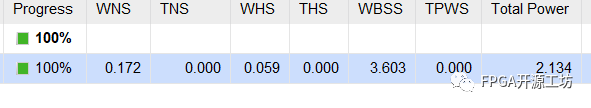

可以看到時序的建立時間不滿足。

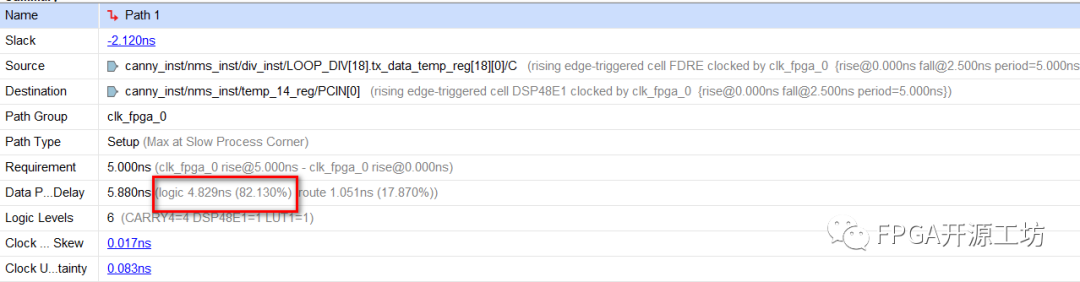

我們在約束的主時鐘頻率是200MHz,也就是5ns,但是建立時間是-2.12ns,也就是說這個工程只能跑到7.12ns也就是140.45MHz,遠遠不能滿足我們預先的設計。

在之前文章里面介紹過怎么在SpinalHDL里面估計一個模塊可以跑到的最大頻率,可以參見:SpinalHDL--快速評估代碼性能

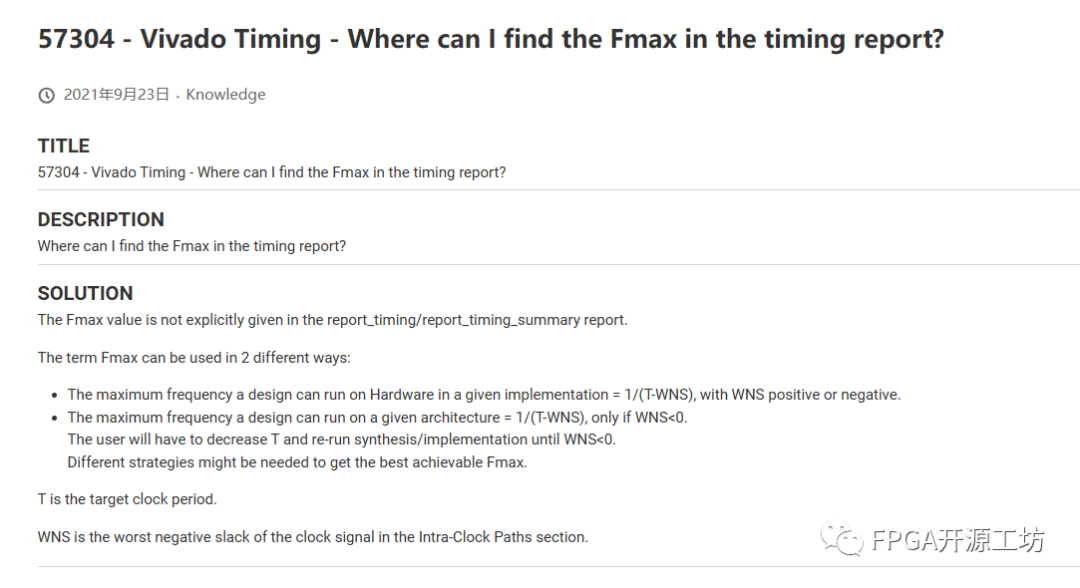

怎么根據時序約束和建立保持時間裕量來分析工程能跑到的最大頻率可以參考下面:

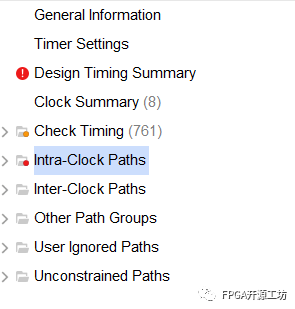

首先來看一下PR之后是哪條路徑不收斂,究竟是同一時鐘域下的還是跨時鐘域的路徑,兩者的處理方式不一樣。

可以看到是Intra-clock paths爆紅了,也就是同一時鐘域下的路徑時序不收斂。

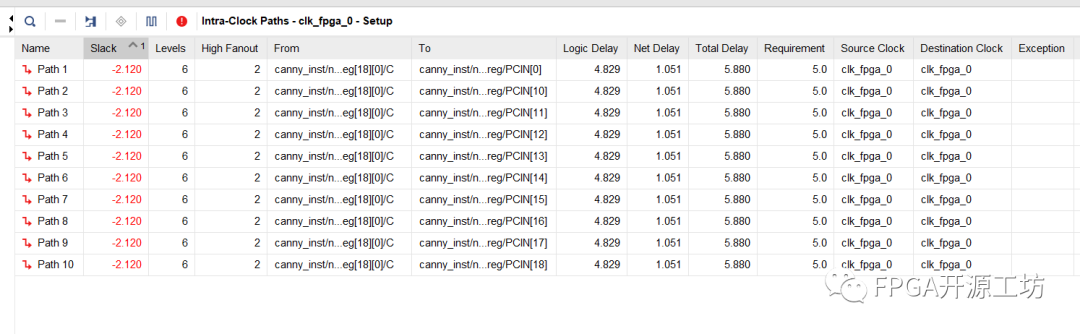

接下來看具體的時序路徑:

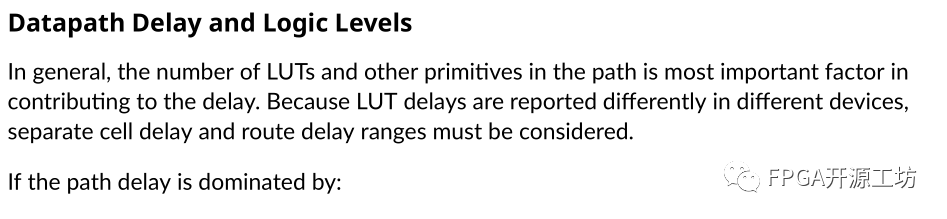

可以看到logic delay遠遠比net delay大,那么我們就需要去降低logic delay,也就是要把我們的組合邏輯搞簡單一點。如果是net delay比較大就要考慮是不是布線擁塞的問題了,兩者的處理方式不太一樣。

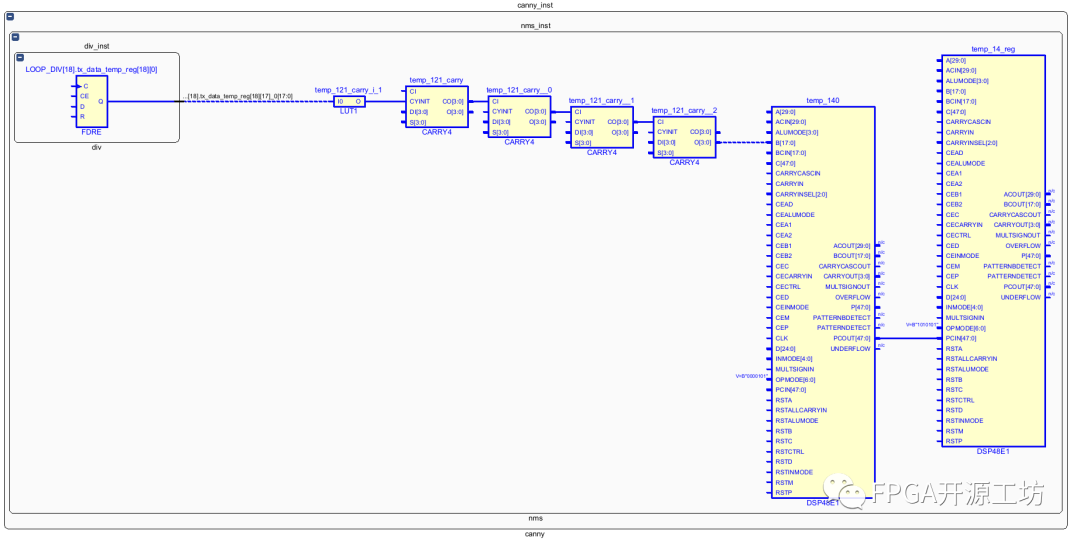

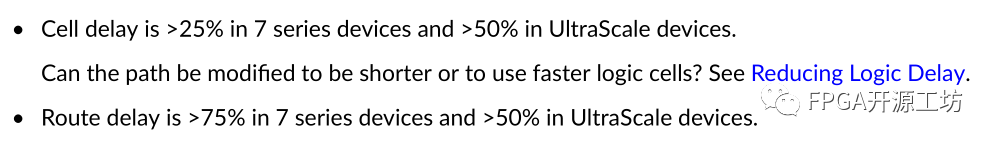

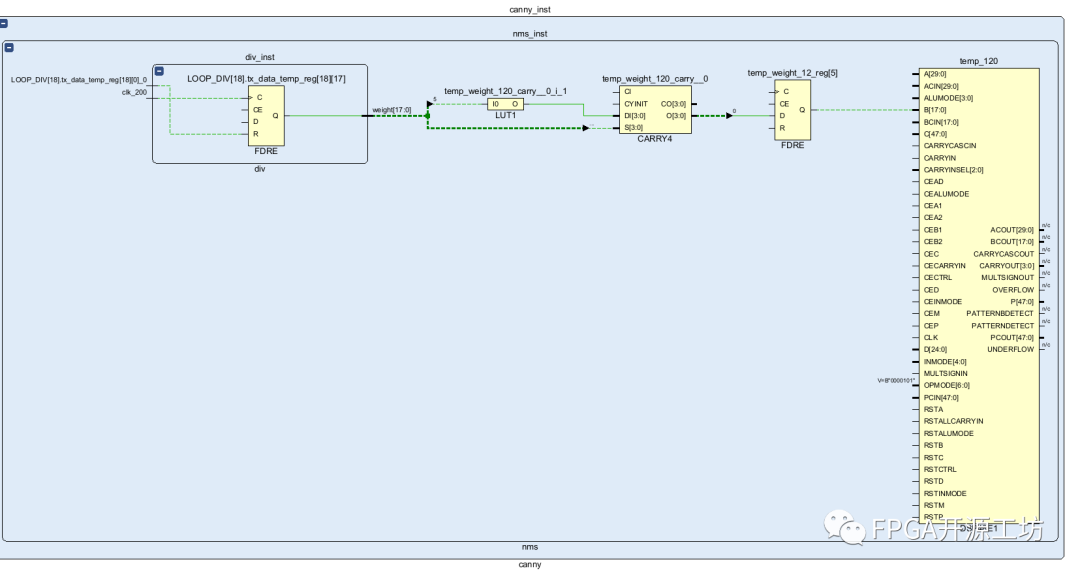

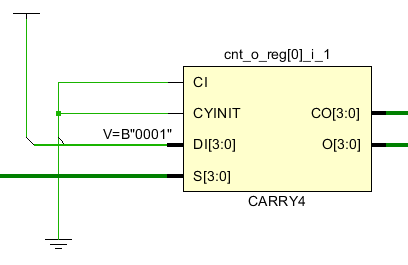

再來看一下它的電路圖,可以看到在左邊的寄存器輸出之后經過LUT,Carry等組合邏輯之后,給到DSP的輸入端。一般來說DSP的幾級pipline最好的都用上,這樣DSP可以跑到更高的頻率。

再來看一下具體的路徑報告:

可以看到logic的延時占到了82%,因此如果要解決這個時序為例,就必須要把logic delay給降低。

兩者的比例可以參考,七系列的FPGA和UltraScale系列的FPGA不太一樣:

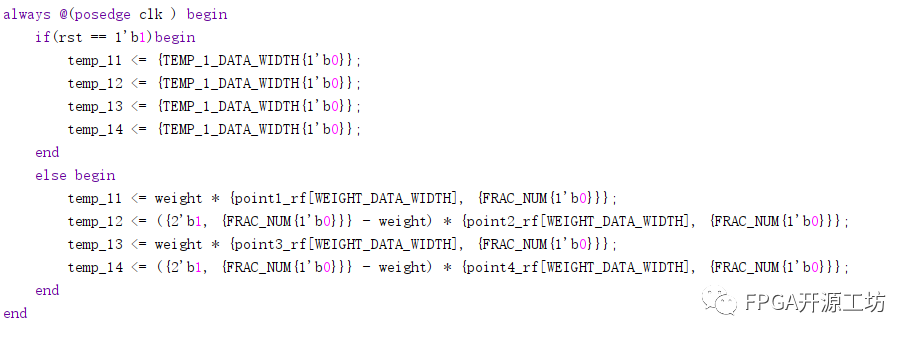

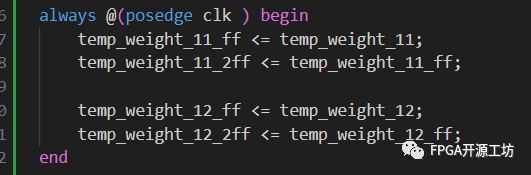

來看一下這一個時序為例對應的代碼:

可以看到其實挺復雜的,有減法,有乘法。其中減法是被vivado用LUT+Carry搭了起來,乘法用的DSP。

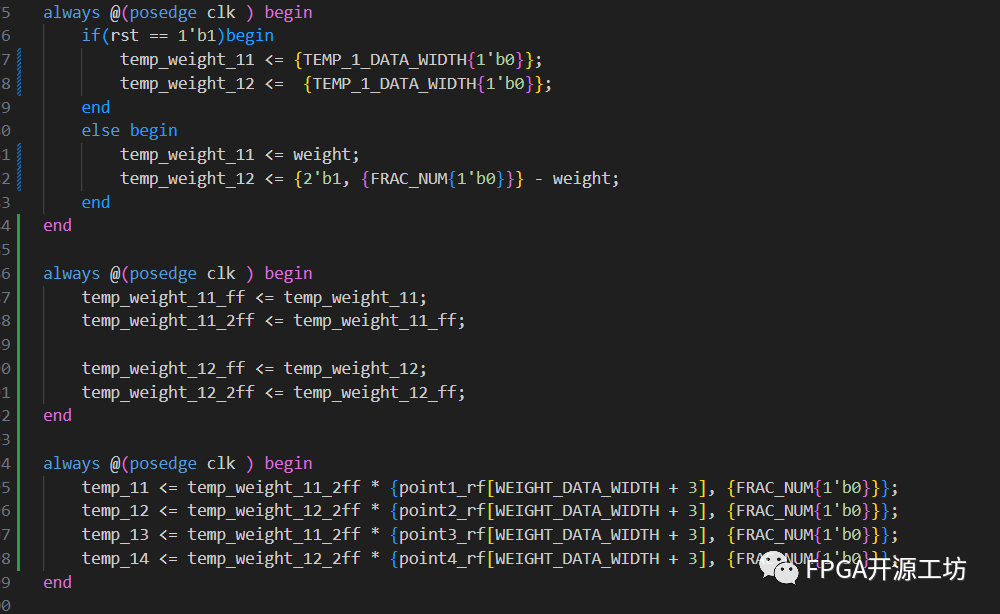

要解決這個問題,就是把這一大段代碼進行流水拆開嘛,把減法拆一級流水,乘法器拆為三級流水。

將代碼修改為以下的樣子,再來綜合一下

可以看到時序就收斂了。

再來看一下生成電路結構:

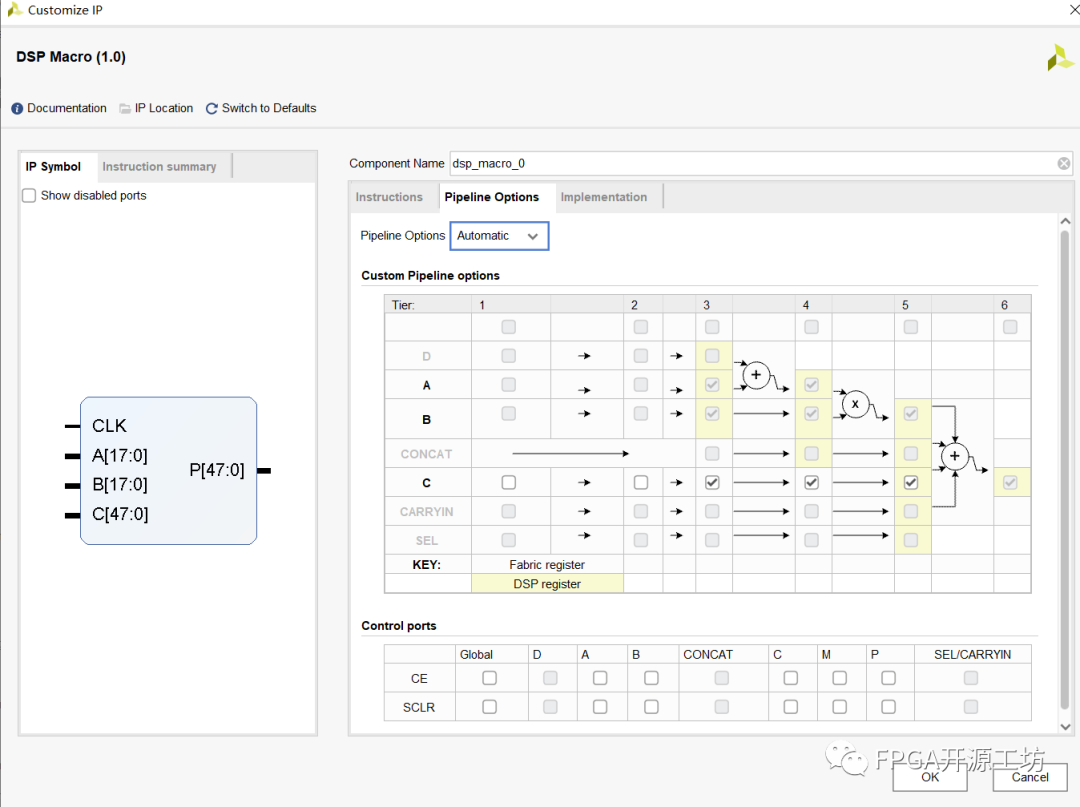

可以看到FDCE之后仍然是LUT+Carry的形式,用于做減法運算,然后再接入DSP的輸入,在源碼里面做完減法之后還有這兩級寄存器,但是在電路圖里面看不到他們了,這是因為這兩級寄存器被DSP給吸收掉了,用于提高DSP的時鐘頻率,這兩級寄存器會利用DSP單元內部的寄存器來實現,并不會增加我們的資源占用,DSP核里面的資源不用也是浪費。

上圖為DSP單元里面的寄存器排布,可以看到有六級。

本篇介紹了一次時序調優的過程,就是重新計算流水線,看看哪里是時序瓶頸。這種重新計算流水線的方式代價還是比較大的,需要重新修改代碼,所以在設計初期就應該考慮到這個問題,比如DSP的流水線寄存器,BRAM的輸出寄存器這些在設計初期就考慮使用到它們,來獲取更好的時序。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606019 -

寄存器

+關注

關注

31文章

5363瀏覽量

121172 -

時鐘

+關注

關注

11文章

1747瀏覽量

131803 -

時序收斂

+關注

關注

0文章

14瀏覽量

7625 -

python

+關注

關注

56文章

4807瀏覽量

85039

原文標題:記錄一次時序收斂的過程

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA時序收斂學習報告

FPGA時序約束的幾種方法

FPGA時序約束的幾種方法

基于MCMM技術IC時序收斂的快速實現

核電廠一次屏蔽深穿透計算

嘮一嘮解決FPGA約束中時序不收斂的問題

記錄一次使用easypoi時與源碼博弈的過程

記錄一次時序收斂的過程

記錄一次時序收斂的過程

評論