晶振下方不能走信號(hào)線的主要原因是為了防止信號(hào)的干擾和保證晶振的穩(wěn)定性。晶振是一種基于晶體振蕩的元件,它的性能對(duì)于整個(gè)系統(tǒng)的穩(wěn)定性和時(shí)序非常關(guān)鍵。以下是一些防止在晶振下方走信號(hào)線的主要原因:

電磁干擾(EMI): 晶振產(chǎn)生的振蕩信號(hào)很弱,容易受到外部電磁干擾的影響。如果在晶振下方走信號(hào)線,信號(hào)線可能會(huì)作為天線,引入額外的電磁噪聲,影響晶振的性能。

信號(hào)完整性: 晶振信號(hào)是一個(gè)非常精確的時(shí)鐘信號(hào),對(duì)于整個(gè)系統(tǒng)的時(shí)序要求非常高。如果在晶振下方走信號(hào)線,可能會(huì)導(dǎo)致信號(hào)的失真、時(shí)鐘抖動(dòng)等問題,從而影響系統(tǒng)的穩(wěn)定性和性能。

互電容和互感: 在信號(hào)線之間存在互電容和互感,如果在晶振下方走信號(hào)線,可能會(huì)引入不同信號(hào)線之間的電容和電感效應(yīng),從而影響信號(hào)的傳輸和時(shí)序。

電氣性能: 晶振通常要求非常穩(wěn)定的電氣環(huán)境,以確保其振蕩頻率的準(zhǔn)確性。信號(hào)線的存在可能引入不穩(wěn)定性,從而影響晶振的性能。

為了最大程度地確保晶振的性能和系統(tǒng)的穩(wěn)定性,通常建議將晶振周圍的區(qū)域保持清晰,不要設(shè)計(jì)信號(hào)線穿越晶振的底部。這可以通過合理的布局規(guī)劃和地線設(shè)計(jì)來實(shí)現(xiàn),確保晶振周圍的電磁環(huán)境盡可能干凈,有助于提高系統(tǒng)的可靠性和性能。

由于晶振為干擾源,本體下方所有層原則上不準(zhǔn)許走線,特別是關(guān)鍵信號(hào)線,要保證晶振周圍的沒有其他元件,防止器件之間的互相干擾,影響時(shí)鐘和其他信號(hào)的質(zhì)量。若濾波器器件放在晶振下方,且濾波電容與匹配電阻未按照信號(hào)流向排布,會(huì)使濾波器的濾波效果變差。

-

晶振

+關(guān)注

關(guān)注

34文章

2899瀏覽量

68316 -

晶體振蕩器

+關(guān)注

關(guān)注

9文章

631瀏覽量

29253 -

信號(hào)線

+關(guān)注

關(guān)注

2文章

176瀏覽量

21579 -

晶體振蕩

+關(guān)注

關(guān)注

1文章

13瀏覽量

10099

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速信號(hào)線走線規(guī)則有哪些

差分信號(hào)線的選擇與處理

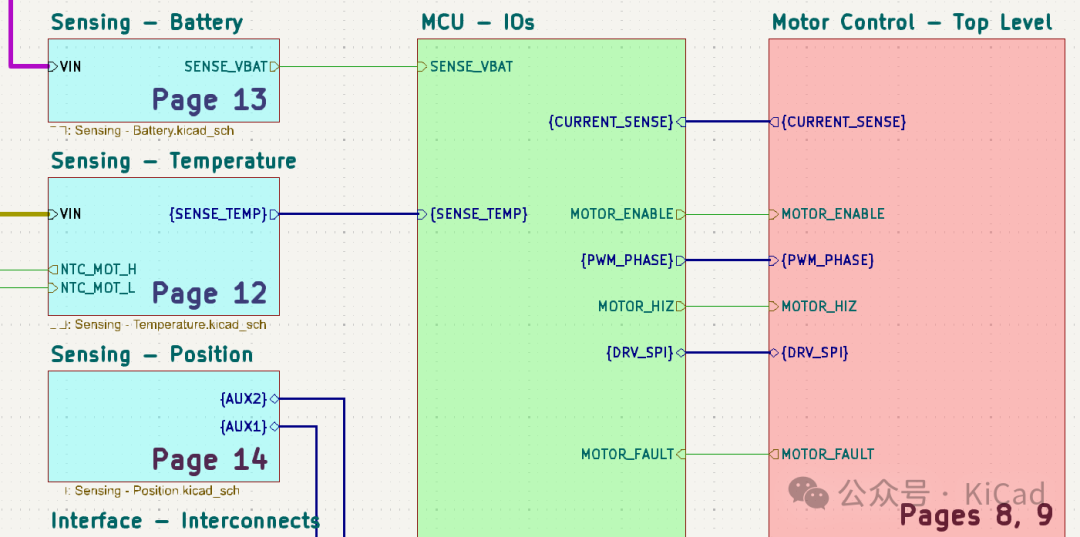

使用總線別名(Bus Alias)實(shí)現(xiàn)信號(hào)線束的功能

信號(hào)線是什么線

深入解析晶振時(shí)鐘信號(hào)干擾源:寄生電容、雜散電容與分布電容

晶振在pcb布局中注意事項(xiàng)

晶振的總頻差解析:調(diào)整頻差與溫度頻差的綜合影響

拉繩開關(guān)的信號(hào)線有哪些作用

4-20ma信號(hào)線一定要用屏蔽線嗎

高速差分信號(hào)走線要點(diǎn)分析

流量計(jì)的信號(hào)線怎么接

差分信號(hào)線與單端信號(hào)線的區(qū)別

信號(hào)線和屏蔽線的區(qū)別 屏蔽線可以當(dāng)信號(hào)線用嗎?

LED透明屏走線方式圖解

為什么晶振下方不能走信號(hào)線?

為什么晶振下方不能走信號(hào)線?

評(píng)論