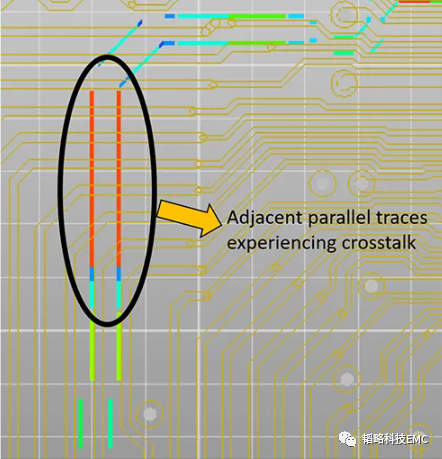

隨著科技發展和人們消費需求,現今電子設備小型化的趨勢越來越突出,印制電路板(PCB)越做越小。這導致PCB板內信號走線之間容易產生無意間耦合,這種耦合現象被稱為串擾(如圖1)。

圖1.平行走線相互串擾

以下列舉一些減少串擾的PCB布線規則。

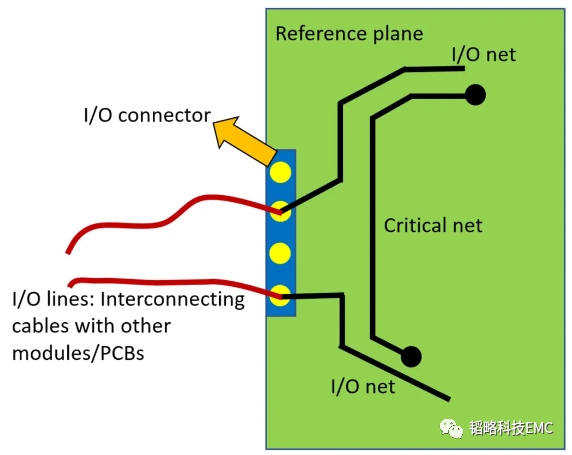

規則 1:關鍵信號遠離I/O信號

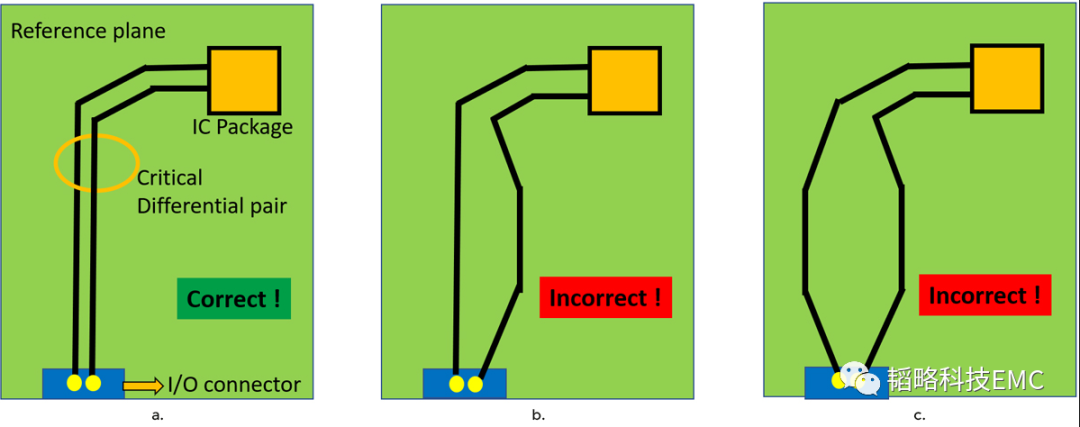

需要重點關注I/O連接口附近的關鍵布線,因為噪聲很容易通過這些 I/O 口以輻射或者傳導的形式離開或進入電路板。如I/O口直連的信號線與關鍵信號線靠太近,會產生耦合效應(見圖 2)。

圖2.關鍵信號與I/O口走線圖示

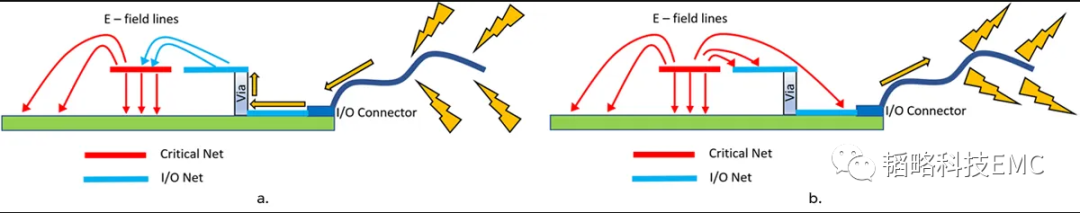

噪聲會通過I/O連接線進入,并通過PCB內部I/O連接線耦合到關鍵信號上(時鐘或敏感信號),模型如圖3a。同樣的,關鍵信號(時鐘或高速信號)會將噪聲耦合到PCB內部的I/O信號走線,并通過I/O連接線往外輻射,模型如圖3b示:

圖3.關鍵信號與I/O信號靠太近會引起潛在的EMC問題

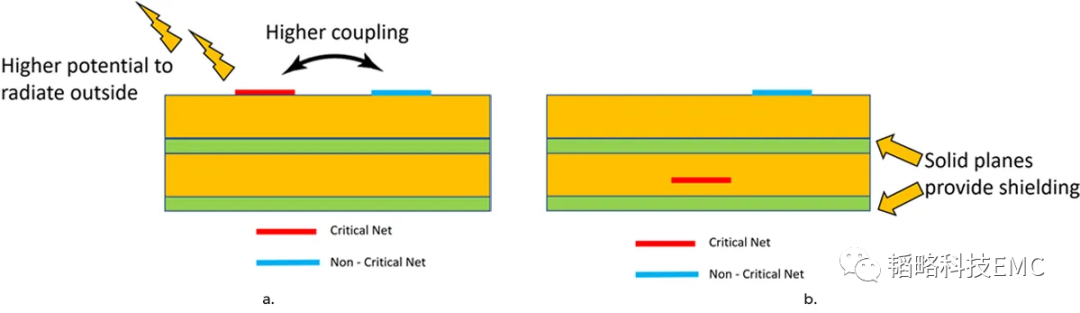

規則2:高速信號走線盡量短

在高速PCB(> 100MHz)上,高頻信號波長較短,輻射效率高,以至高速信號本身走線形成天線效應,特別是當走線放在頂層或底層時。這種不必要的輻射可以耦合到相鄰的走線甚至是附近接口連接線。我們建議將高速信號走線畫在PCB中間層,如圖4b所示。這有助于控制來高速信號產生的電磁場,避免出現串擾或電磁干擾形式的非預期耦合。如果高速走線走在表層,則應使走線盡量短,當走線小于電小尺寸(1/10波長)時,天線效應會大大減少。如圖4所示:

圖4. a.信號走表層 b.信號走中間層

規則3:差分網絡匹配

理論上,差分對傳輸的信號大小相等,極性相反,因此差分對產生的EMI會相互抵消或者忽略。但是,只有在差分對走線長度相等并且盡可能對稱地靠近彼此時才有效。圖5展示了幾種不同情況的差分對走線。

圖5.差分走線優劣對比圖

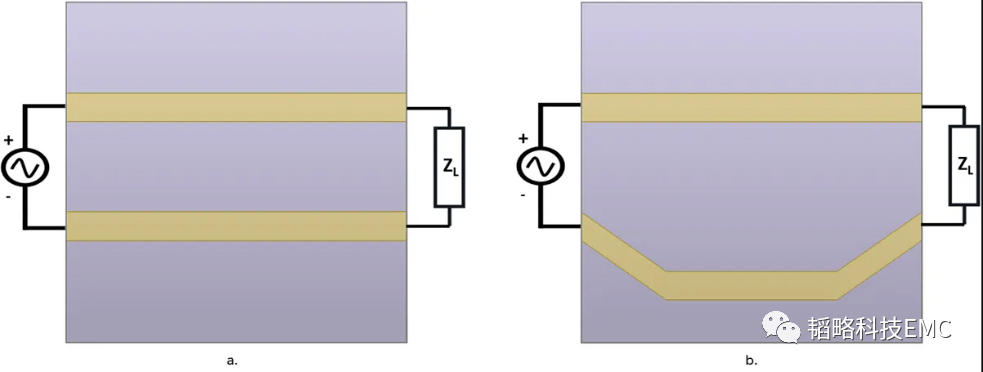

為了對比差分信號走線好壞的輻射情況,作如下電路仿真,圖6a和圖6b分別是兩組對稱和非對稱走線,走線左端輸入高頻差分信號,右端端接負載。

圖6. a.對稱走線 b.非對稱走線

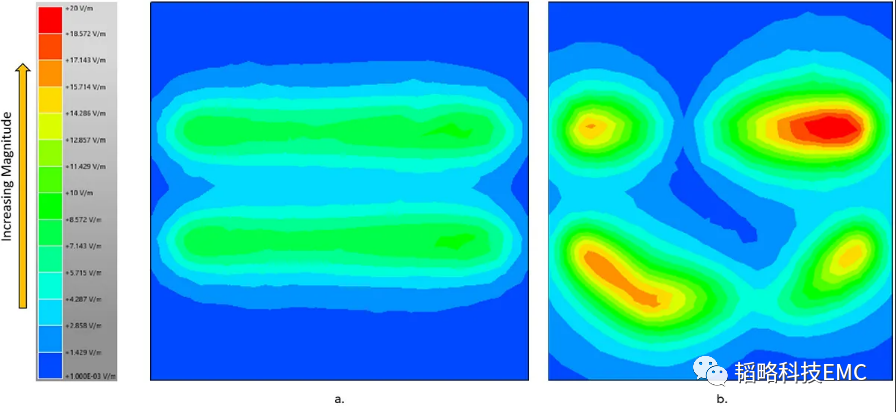

我們對以上兩種情況做近場分析,噪聲仿真如圖7:

圖7.a對稱差分走線仿真圖 b非對稱差分走線仿真圖

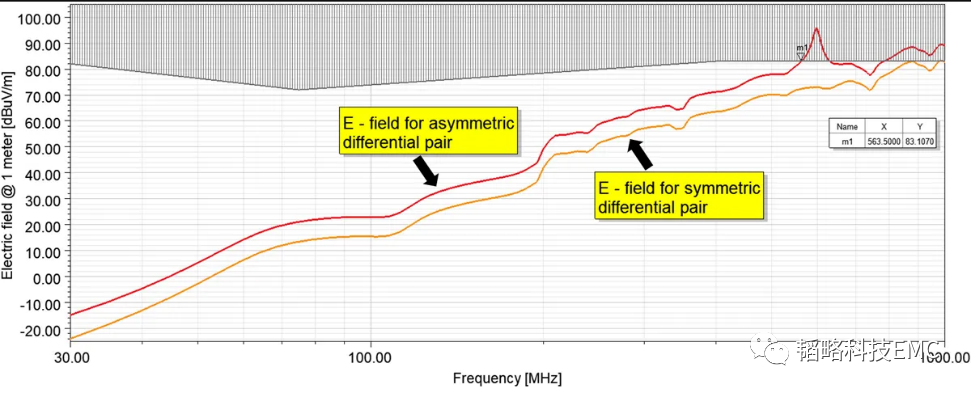

在1m距離情況下,對比測試輻射發射情況。30MHz-1GHz的頻段下,對稱走線比非對稱走線噪聲值小8-10db,如圖8所示。

圖8. 1m距離輻射對比數據

總的來說,在電子設備的設計中,電路前期設計的重要性不容忽視。良好的EMC設計可以確保設備的正常運行,避免電磁干擾對其他設備的影響,并提高產品自身的可靠性。

審核編輯 黃宇

-

PCB板

+關注

關注

27文章

1449瀏覽量

51953 -

信號

+關注

關注

11文章

2804瀏覽量

77100 -

串擾

+關注

關注

4文章

189瀏覽量

26993

發布評論請先 登錄

相關推薦

ADC電路的串擾怎么解決?

DAC61416通道間出現串擾的原因?怎么解決?

博眼球還是真本事?參考平面不完整信號串擾反而好

高頻電路設計中的串擾問題

信號的串擾介紹

多通道數據采集串擾問題怎么解決

放大器的串擾問題

嵌入式開發中引起串擾的原因是什么?

PCB設計中的串擾是什么意思?如何減少PCB設計中的串擾呢?

如何減少PCB板內的串擾

如何減少PCB板內的串擾

評論