對于一直在設法提高效率和功率密度并同時維持系統簡單性的功率設計師而言,碳化硅(SiC)MOSFET的高開關速度、高額定電壓和小RDS(on)使得它們具有十分高的吸引力。然而,由于高開關速度會導致高漏源電壓(VDS)峰值和長振鈴期,它們會產生電磁干擾,尤其是在電流大時。本文提供了一個較好的解決方案來優化電磁干擾和效率之間的平衡。這種方法已經采用1200V 40mOhm器件進行了雙脈沖測試驗證。

了解VDS峰值和振鈴

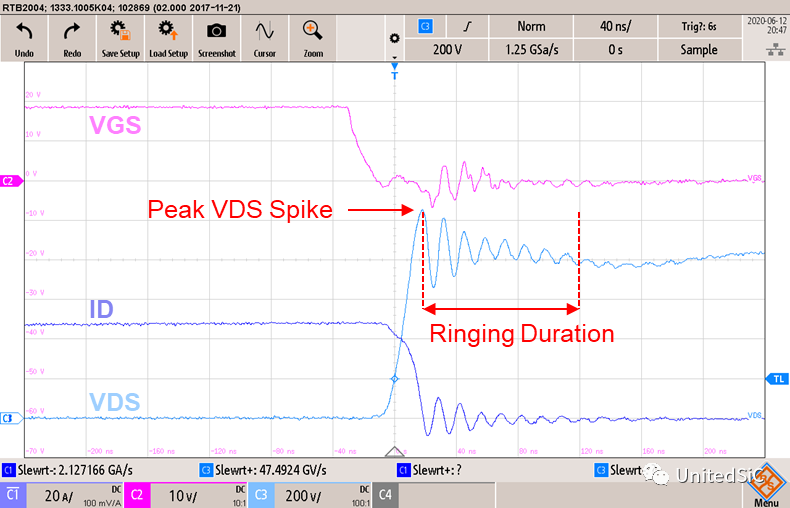

寄生電感是SiC MOSFET的VDS峰值和振鈴的主要成因。從關閉波形(圖1)中看,柵源電壓(VGS)從18V至0V。關閉時的漏極電流(ID)為50A,VDS為800V。SiC MOSFET的高開關速度會導致高VDS峰值和長振鈴期。該峰值降低了器件的設計余量以應對照明條件或負載突變,而長振鈴期則帶來的電磁干擾。在大電流下,這種情況更加明顯。

圖1.使用SiC MOSFET時在關閉情況下的VDS峰值和振鈴(1200V,40mOhm)

常見電磁干擾抑制技術

傳統的電磁干擾抑制方法是使用大柵極電阻(RG)降低電流流經器件的速度(dI/dt)。但是大RG會顯著增加開關損耗,要在效率和電磁干擾之間進行權衡取舍。

另一種抑制電磁干擾的方法是降低功率回路雜散電感。要實現這一目的,需要更改電路板的布局,還需要使用體積較小、電感較低的封裝。然而,盡量降低功率回路的效果是有限的,而且還需要遵守最小空隙和間隔方面的安全規定。使用較小的封裝也會影響熱性能。

可以使用過濾器來幫助達到電磁干擾要求,簡化系統權衡。頻率抖動等控制技術也能降低供電導致的電磁干擾噪音。

使用RC緩沖電路

采用簡單的RC緩沖電路是一種更為有效和高效的方法。它能控制VDS峰值并縮短振鈴期,同時實現更高的效率和可以忽略的關閉延遲。由于更快的dv/dt和額外的電容器,緩沖電路會有更高的位移電流,而這會降低關閉過渡期間的ID和VDS交疊。

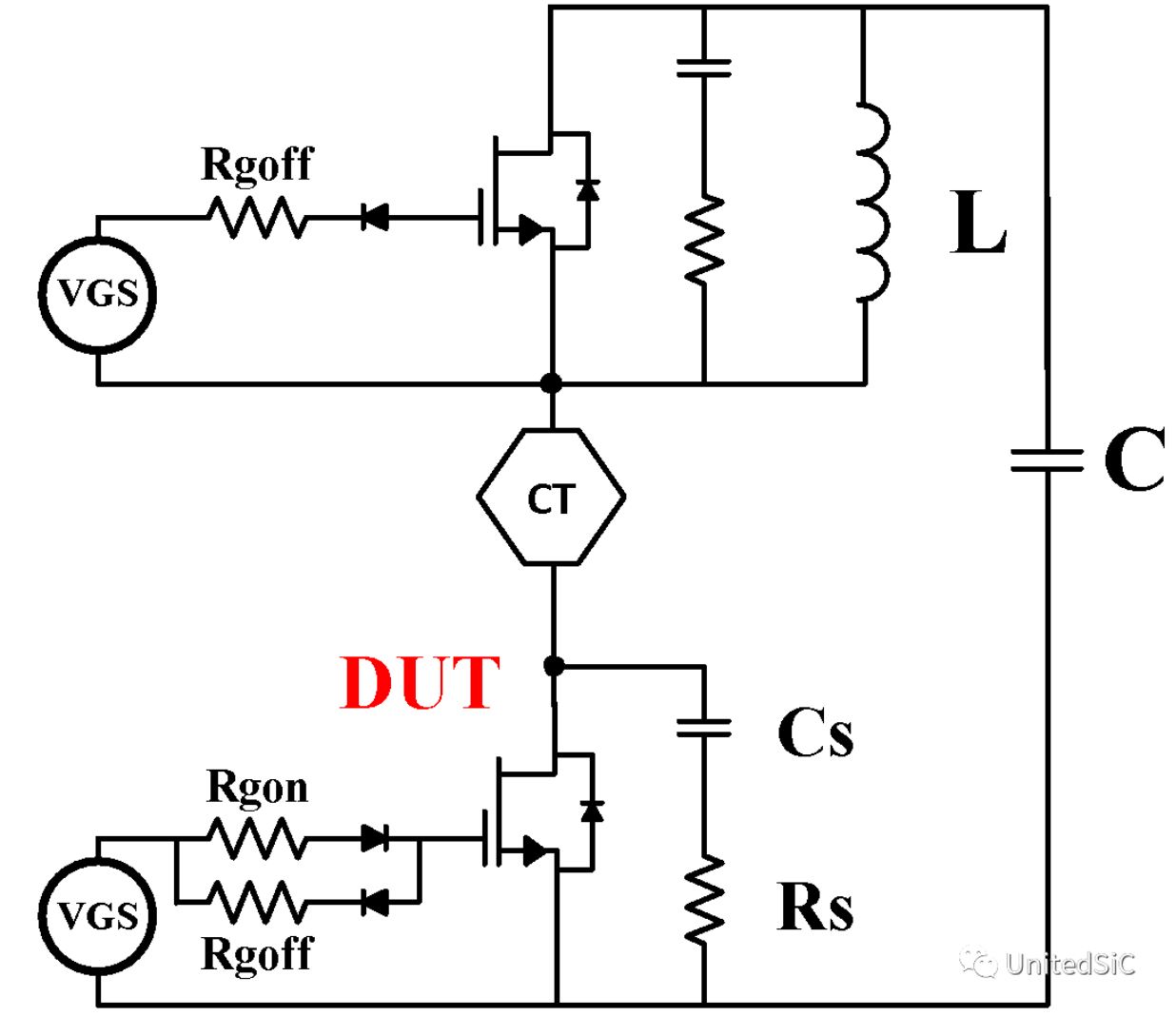

雙脈沖測試(DPT)證實了RC緩沖電路的效果。它采用有電感負載的半橋配置。橋的高側和低側采用相同的器件,在低側測量VGS、VDS和ID(圖2)。電流變換器(CT)測量器件和緩沖電路電流。因此,測量的總開關損耗包含器件損耗和緩沖電路損耗。

圖2.半橋配置(頂部和底部器件相同)

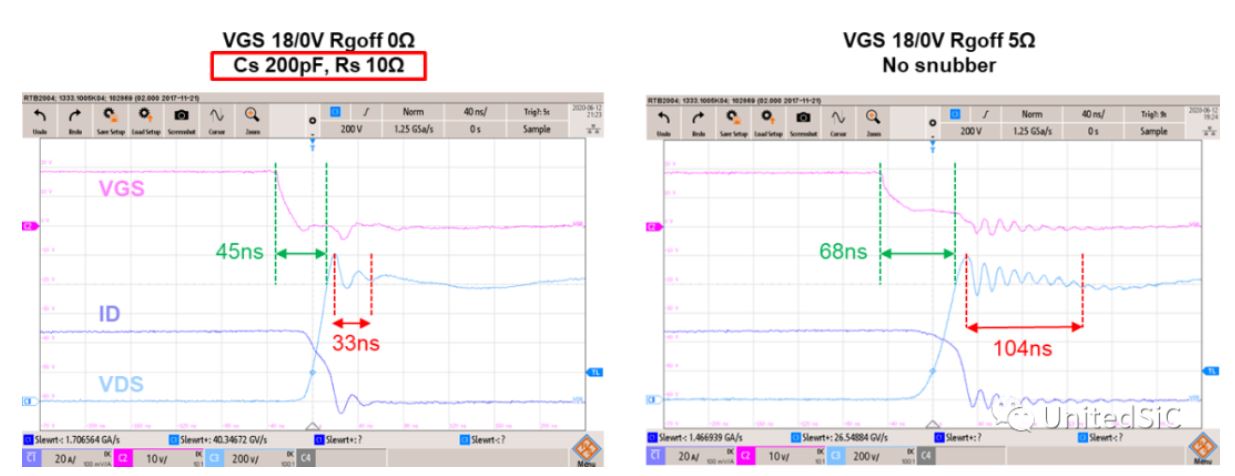

RC緩沖電路由一個簡單的200pF電容器和10Ω電阻串聯而成,跨SiC MOSFET的漏極和源極連接。

圖3. RC緩沖電路(左)能比大RG(右)更有效地控制電磁干擾

圖3比較了圖1中的同一個器件的關閉情況。左側波形采用含小RG(off)的緩沖電路,而右側波形采用大RG(off)且無緩沖電路。兩種方法都限制了關閉峰值漏源電壓VDS。然而,由于將振鈴期降低至僅33ns,緩沖電路更加高效,延遲時間也更短。

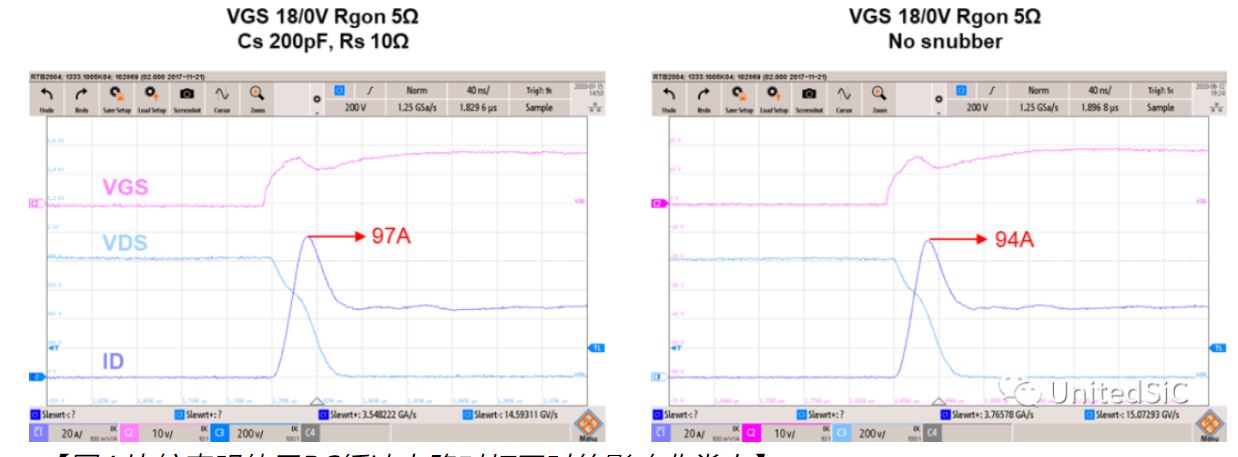

圖4.比較表明使用RC緩沖電路對打開時的影響非常小

圖4比較了在采用5Ω的RG(on)時,有RC緩沖電路(左)和沒有緩沖電路時的波形。采用RC緩沖電路時的打開波形有一個峰值略高的反向恢復電流(Irr),但是沒有其他顯著區別。

RC緩沖電路能比大RG(off)更有效地控制VDS的峰值和振鈴期,但是它會影響效率嗎?

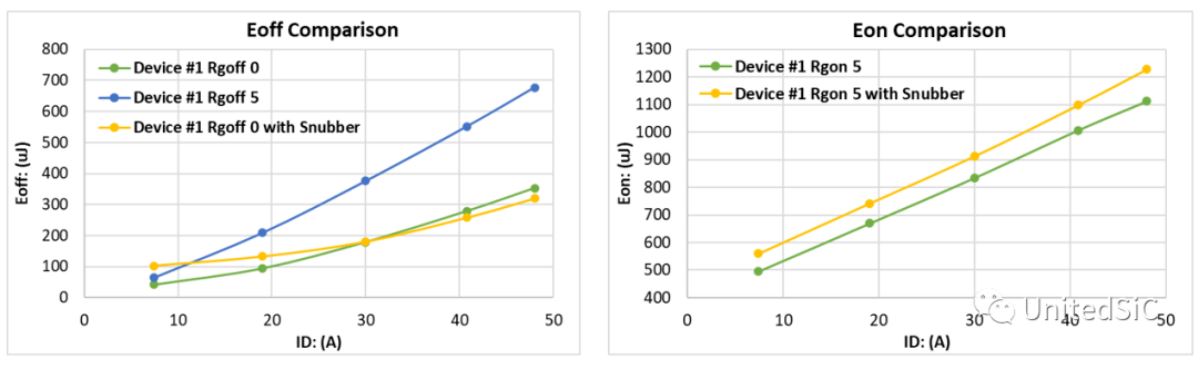

圖5.緩沖電路和大RG(off)的開關損耗(Eoff、Eon)的比較

在48A電流下,大RG(off)的關閉損耗是含小RG(off)的緩沖電路的兩倍以上,幾乎與不采用緩沖電路時相當。因此,可以得出結論,緩沖電路更加高效,它允許更快地開關,并能更有效地控制VDS峰值和振鈴。從打開損耗中可以看出,緩沖電路的Eon僅有微小的提高。

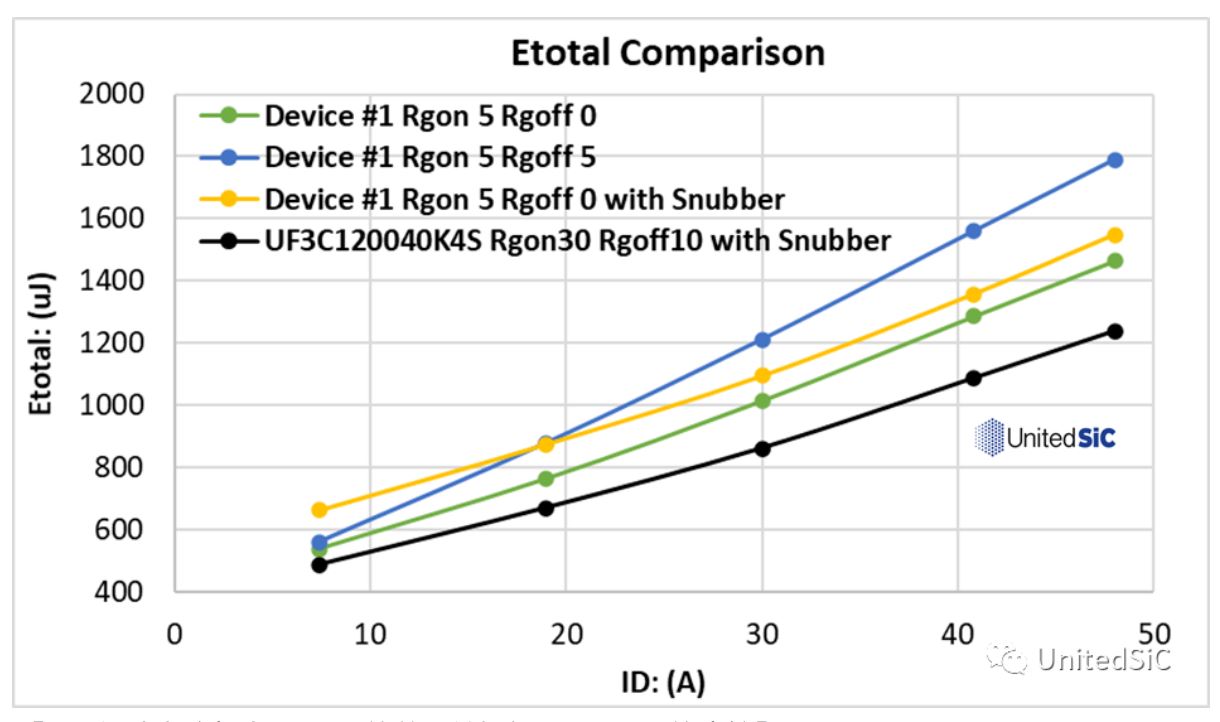

圖6.緩沖電路與大RG(off)的總開關損耗(Etotal)的比較

為了更好地了解整體效率,我們將Eoff與Eon加在一起得到Etotal(圖6)。在全速開關的情況下,電流超過18A時,緩沖電路更高效。對于在40A/40kHz下開關的40mΩ器件而言,采用大RG(off)與采用含小RG(off)的緩沖電路時的損耗之差為11W。總之,與使用大RG(off)相比,緩沖電路能更為簡單、有效和高效地盡量降低電磁干擾和開關損耗。

-

MOSFET

+關注

關注

147文章

7240瀏覽量

214268 -

電磁干擾

+關注

關注

36文章

2331瀏覽量

105645 -

SiC

+關注

關注

29文章

2887瀏覽量

62941 -

碳化硅

+關注

關注

25文章

2824瀏覽量

49274

發布評論請先 登錄

相關推薦

PFC MOSFET的開關損耗測試方案

功率MOSFET的開關損耗:開通損耗

為何使用 SiC MOSFET

全SiC功率模塊的開關損耗

開關損耗更低,頻率更高,應用設備體積更小的全SiC功率模塊

SiC-SBD大幅降低開關損耗

【干貨】MOSFET開關損耗分析與計算

內置SiC SBD的Hybrid IGBT 在FRD+IGBT的車載充電器案例中 開關損耗降低67%

MOSFET開關損耗分析

使用LTspice估算SiC MOSFET的開關損耗

全SiC功率模塊的開關損耗

使用SiC MOSFET時如何盡量降低電磁干擾和開關損耗

使用SiC MOSFET時如何盡量降低電磁干擾和開關損耗

評論