最近項目中,FPGA通過多個RGMII接口與其他設(shè)備通信,在通信的過程中,有一個RGMII接口對端設(shè)備始終無法驅(qū)動,最后通過共享一個PHY,時分復(fù)用的形式來“解決”該問題

案例背景

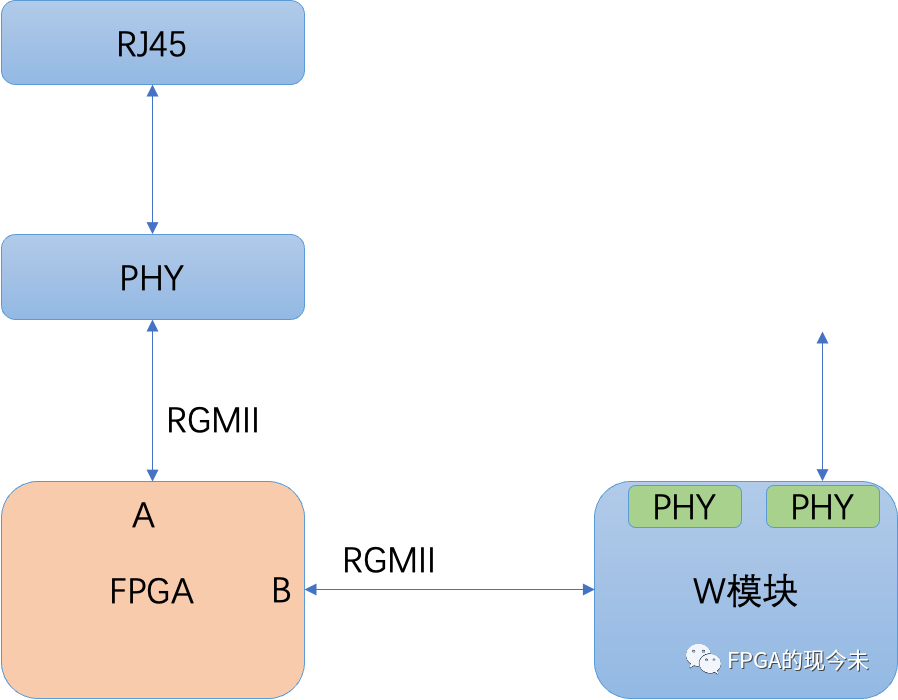

FPGA一共有2個RGMII接口,其中A接口外接一個PHY后通過RJ45連接網(wǎng)線,B接口通過RGMII接口以MAC對MAC的形式直接和W模塊相連,如下圖所示:

正常的業(yè)務(wù)場景下,F(xiàn)PGA有可能通過A接口用網(wǎng)線和外部連接的設(shè)備通信,也可能直接和W模塊通信。

問題

由于W模塊的問題,始終無法驅(qū)動RGMII接口,后來和供應(yīng)商,以及W模塊上芯片的原廠交流,都無法知道如何驅(qū)動該RGMII接口(***任道重遠(yuǎn)啊),F(xiàn)PGA和W模塊的通路徹底斷開。

分析及解決措施

(1)由于FPGA和W模塊之間的性能需要500Mbps+,所以無法通過飛線產(chǎn)生一個通用IO口來解決該問題;

(2)W模塊供應(yīng)商其實也沒有對RGMII接口做過充分測試,推薦我們使用的是該模塊內(nèi)置的PHY接口和外界通信;

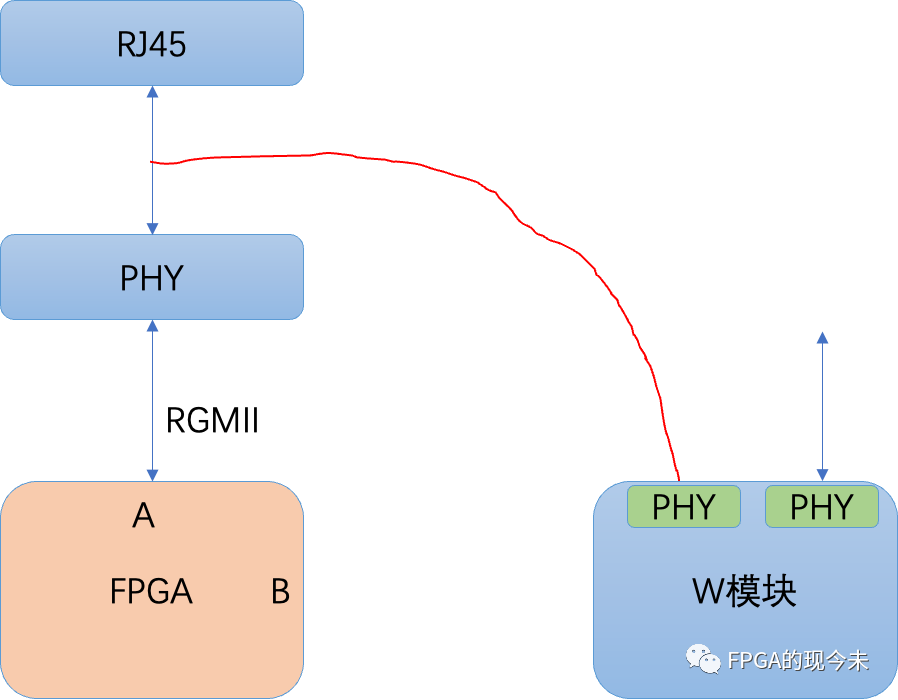

(3)FPGA的AB接口的業(yè)務(wù)本來可以不同時存在,那是否可以時分復(fù)用FPGA外接的PHY了,即FPGA通過PHY和RJ45通信,也可以和W模塊通信呢?于是構(gòu)想了如下的方案:

利用W模塊內(nèi)置的PHY,通過飛線的方式,連在PHY和RJ45之間,如圖中紅色線條所示。當(dāng)RJ45插上網(wǎng)線時,F(xiàn)PGA和RJ45通信,否則FPGA就和W模塊通信。但是這個方案有一個問題,當(dāng)插上網(wǎng)線的時候,外部設(shè)備和W模塊都通過FPGA的同一個PHY和FPGA通信,這必要會有沖突,那現(xiàn)在的問題就是這2種模式如何最小代價的切換。

(4)由FPGA控制W模塊的上電來切換,當(dāng)FPGA和RJ45通信的時候,通過配置FPGA寄存器的方式,將W模塊下電,當(dāng)FPGA要和W模塊通信的時候,拔掉網(wǎng)線,同時通過配置FPGA寄存器的方式將W模塊上電。

測試結(jié)果

這種方案行不行,上板測試是最好的檢驗方法。

(1)將W模塊下電,插上網(wǎng)線,外部設(shè)備通過網(wǎng)線給FPGA發(fā)包,F(xiàn)PGA在內(nèi)部MAC做環(huán)回,通過測試;

(2)將W模塊上電,拔掉網(wǎng)線,通過W模塊發(fā)包,F(xiàn)PGA在內(nèi)部MAC做環(huán)回,通過測試;

(3)將W模塊上電,且插上網(wǎng)線,我們通過W模塊和外部設(shè)備發(fā)現(xiàn),和FPGA的鏈路不穩(wěn)定,一會能link up,一會又link down,即有沖突,和我們前期預(yù)想的一致。當(dāng)拔掉網(wǎng)線,或者W模塊下電后,對端都能和FPGA正常通信。

總結(jié)

當(dāng)一個PHY同時和2個PHY對接的時候,只要我們做好2個PHY的切換,是可以實現(xiàn)“時分復(fù)用”的,但是不到萬不得已,還是別這么干吧。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605999 -

接口

+關(guān)注

關(guān)注

33文章

8691瀏覽量

151915 -

通信

+關(guān)注

關(guān)注

18文章

6070瀏覽量

136424 -

PHY

+關(guān)注

關(guān)注

2文章

305瀏覽量

51862 -

RGMII

+關(guān)注

關(guān)注

0文章

28瀏覽量

12216

發(fā)布評論請先 登錄

相關(guān)推薦

RGMII接口及其時序規(guī)范

請問DP83822IRHB該PHY要配成RGMII時,到底還需要哪些配置?

如何加裝第二個路由器

如何橋接第二個無線路由器

實現(xiàn)具有電壓轉(zhuǎn)換功能的工業(yè)和汽車以太網(wǎng)RGMII接口

SPI、UART、RGMII、JTAG接口的低電壓轉(zhuǎn)換

聚焦MIPI 系列之四:一文盤點D-PHY/C-PHY/M-PHY之架構(gòu)與測試解決方案

RTOS版本的sdk,為什么無法讀取第二個512Mflash的內(nèi)容?

2024年第二季度PC出貨量實現(xiàn)連續(xù)第二個季度增長

具有SGMII和RGMII的DP83TG720S-Q1 1000base-T1汽車以太網(wǎng)PHY數(shù)據(jù)表

自定義設(shè)備的端點是由USB PHY芯片決定的,那每一個端點的特性也是芯片決定好的嗎?

關(guān)于飛騰的E20000Q芯片的USXGMII萬兆網(wǎng)接口使用

DDR phy內(nèi)存控制器的作用是什么?

一文詳解以太網(wǎng)MAC芯片與PHY芯片

RGMII接口案例:二個設(shè)備共享一個PHY

RGMII接口案例:二個設(shè)備共享一個PHY

評論