引言

隨著中美貿易戰、中美科技戰打響以來,集成電路成了一個熱門話題。我國也在加強集成電路的發展[1],那么一個小小的芯片上到底隱藏著什么奧秘,中國為什么會因此而受到國外的限制呢?

所謂的集成電路就是將我們所熟識的普通電路通過一種平面工藝的方式集成到一塊芯片上,這種方法不僅簡化了制作流程,而且大大縮小了電路面積,真正做到了輕量化、小型化。而芯片上的電路主要是由晶體管、金屬導線、電阻、電感和電容組成的,其中起關鍵作用的就是晶體管,下面主要向大家介紹一下晶體管。

晶體管

晶體管被譽為“20世紀最偉大的發明”,它的出現為集成電路、微處理器以及計算機內存的產生奠定了基礎。1947年12月23日,第一個基于鍺半導體的具有放大功能的點接觸式晶體管面世,標志著現代半導體產業的誕生和信息時代正式開啟。它的發明人肖克利、巴丁和布拉頓也因此獲得了諾貝爾物理學獎[2]。

20世紀五六十年代,肖克利在推動晶體管商業化的同時,造就了如今加州電子工業密布的硅谷地區。現如今,從播放音樂、合成語音、存儲數據、數碼攝影、GPS定位到傳輸和處理互聯網上的海量數據,我們的日常生活中芯片已經成為不可或缺的產品[3]。

晶體管與半導體

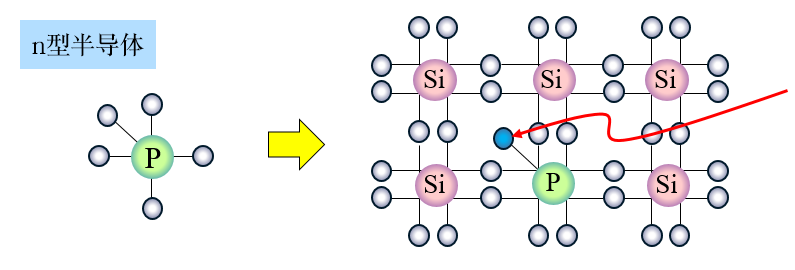

大家一定好奇我們身邊無處不在的晶體管是如何工作的呢?晶體管是由諸如硅和鍺之類的半導體組成。所謂的半導體就是導電率介于導體與半導體之間的材料。硅作為目前主流的半導體材料,其原子最外層有四個電子,在沒有任何摻雜的情況下,是不具備導電能力的。然而當硅中摻雜磷后,被稱為N型半導體,由于磷原子最外層有5個電子,當一個磷原子替換了硅原子會多出一個自由電子,因此N型硅中的多數載流子是電子;當硅中摻雜硼后,被稱為P型半導體,由于硼原子最外層有3個電子,當一個硼原子替換了硅原子會提供一個電子空位,也就是常說的空穴,是帶正電的,因此P型硅中的多數載流子是空穴。空穴和電子是兩種相對的載流子,當其中一種數量較多時,另一種就會相應的減少。

圖2 n型半導體和p型半導體原子結構示意圖

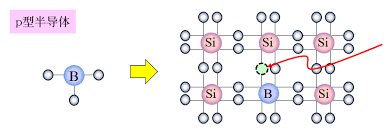

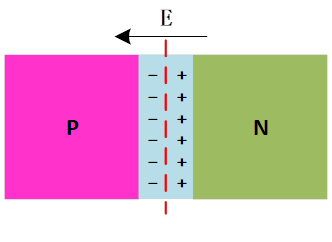

晶體管的分類

晶體管,目前主流的還是基于硅襯底制作的。根據工作原理不同分類,分為二極管、雙極晶體管和單極晶體管三種類型。

圖3 晶體管分類

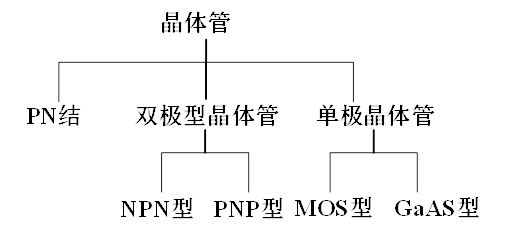

二極管

二極管是一個P型硅和一個N型硅形成的PN結,如下圖所示。當P型硅和N型硅接觸后,P區中的空穴濃度大于N區,N區中的電子濃度大于P區,所以P區中的空穴在濃度梯度的驅使下向N區流動,同樣的,N區中的電子也向P區流動,這樣就造成了PN界面處,靠近P區區域由于空穴的流走而形成了帶負電的B-離子,靠近N區區域由于電子的流走而形成了帶正電的P+離子,這個區域被稱作耗盡區。耗盡區由于只剩下固定電荷,會形成由N區指向P區的內建電場,在這個內建電場的作用下,空穴會從N區流向P區,電子會從P區流向N區,當電場作用和擴散作用達到了一個動態平衡,這就形成了一個PN結。PN結的正向導電性也正因如此,當P加正電壓,N區加負電壓時,內建電場在外加電壓的作用下減小了,從而多子的擴散的運動增強了,就會有P區到N區的電流的形成;當加上相反的電壓,內建電場增強了,而P區不能夠提供足夠的電子,N區也不能夠提供足夠的空穴,所以不能夠形成足夠大的N區到P區的電流。

(a) (b)

圖4 (a)二極管結構示意圖(b)二極管實物圖

雙極晶體管(Bipolar Junction Transistor, BJT)

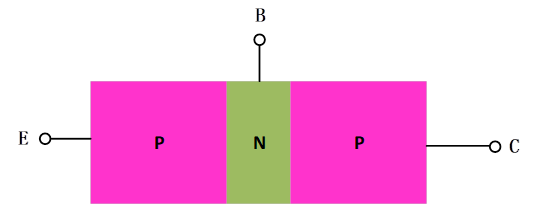

雙是指Bi(2個)、極是指Polar(極性),按照其結構分類可分成NPN型和PNP型。雙極晶體管,即流經構成晶體管的半導體的電流由空穴(正極性)和電子(負極性)產生,它主要用于信號的放大[4]。它是由兩個相反的PN結構成的,下圖是基本結構示意圖,共有三個電極,分別是左邊的發射極(E)、中間的基極(B)、右邊的集電極(C)。當BJT開啟時,發射結需要正偏,集電結需要反偏,即發射極(E)接正電壓,基極(B)接負電壓,集電極接更負的電壓,此時發射極會向基極注入空穴,基區空穴中的一小部分會與基區的電子復合掉,基極會有一個很小的復合電流,另一大部分的空穴會因集電極的反偏而被反偏電場掃入集電區后從集電極流走了。當基區的寬度足夠小時,集電極電流會遠遠大于基極電流,因此可以看成將基極電流放大了。

(a) (b)

圖5 (a)BJT結構示意圖(b)BJT實物圖

金屬-氧化物-半導體場效應晶體管(MOSFET)

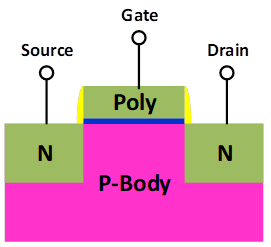

FET是Field Effect Transistor的簡稱,翻譯成中文就是場效應晶體管。有接合型FET、MOS型FET以及GaAs型FET,其中最為應用最廣泛的是MOSFET。MOSFET是Metal Oxide Semiconductor FET的簡稱,因其構造分別是金屬 (Metal)、氧化物 (Oxide)、半導體 (Semiconductor),故稱MOS。是目前大規模集成電路的基本單元,該結構由于它非常好的集成性而被廣泛應用。下圖展示了N型的MOSFET的基本結構示意圖[5]。首先在一個P型硅上注入了兩個N型區作為源區(Source)和漏區(Drain),在源區和漏區之間的P型區被稱為溝道區,溝道上方會有一層薄薄的氧化層,再在氧化層上面用多晶硅(Poly)做柵極,形成一個MOS電容結構,可以通過柵極電壓來控制溝道狀態。

(a) (b)

圖6 (a)MOSFET結構示意圖(b)MOSFET實物圖

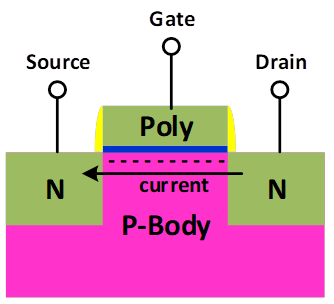

若柵極不加電壓,MOS的溝道區沒有形成電子積累層,無法形成源區到漏區的電子電流通道,此時器件處于關斷狀態。若柵極為正電壓,源極(Source)和體區(Body)一般都接零電位,漏極接正電壓,此時會在溝道表面感應出電子,形成導電路徑,由于源漏區的多數載流子都是電子,所以在漏電壓作用下會形成電子電流,該狀態下器件開啟,如下圖所示。

圖7 開啟狀態下的MOSFET工作模式

像我們的神經元細胞組成大腦一樣,就是這樣的數以萬計或者億計的晶體管組成了我們的電子器件,晶體管的誕生和發展,從根本上影響了電力電子學。在晶體管的基礎上,我們搭配不同的管子實現多種多樣的功能,這也就組成了各種各樣的不同功能的芯片。

晶體管與芯片

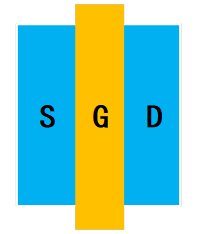

在如今的大規模集成電路領域,主要使用MOSFET作為基本原件進行集成,因為MOSFET的都在表面引出,可以通過上層金屬連接形成電路。如下圖所示是一個MOSFET的版圖,即MOSFET晶體管在芯片上的俯視圖。圖中分別顯示了MOSFET的三個電極,源電極(S)、柵電極(G)、漏電極(D),它們都是從表面引出的電極。

圖8 MOSFET版圖的電極俯視圖

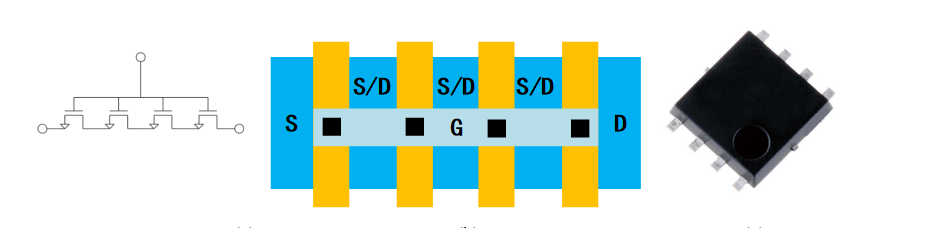

下面介紹一下集成電路是如何將一個個晶體管連接成電路的,這里舉一個例子。如下左圖所示是將四個MOSFET晶體管組成的簡單的電路示意圖,這四個晶體管的源極和漏極串聯起來,它們的柵極并聯起來作為一個共同電極。這樣的簡單電路圖在芯片上的連接方式如下右圖所示,中間的源和漏的連接,由于它們制作的材料相同,可以使用公共區域來制作。柵極的連接由于無法采用公共區域的連接方式,這時候就需要采用外加一層金屬將它們連接起來,為了防止金屬與金屬下方覆蓋的源漏區域發生誤短路,會在金屬與源漏區域之間用絕緣介質SiO2將它們隔開,這樣就實現了一個簡單電路的連接。

(a) (b) (c)

圖9 (a)MOSFET等效電路圖(b)MOSFET器件俯視圖(c)器件實物圖

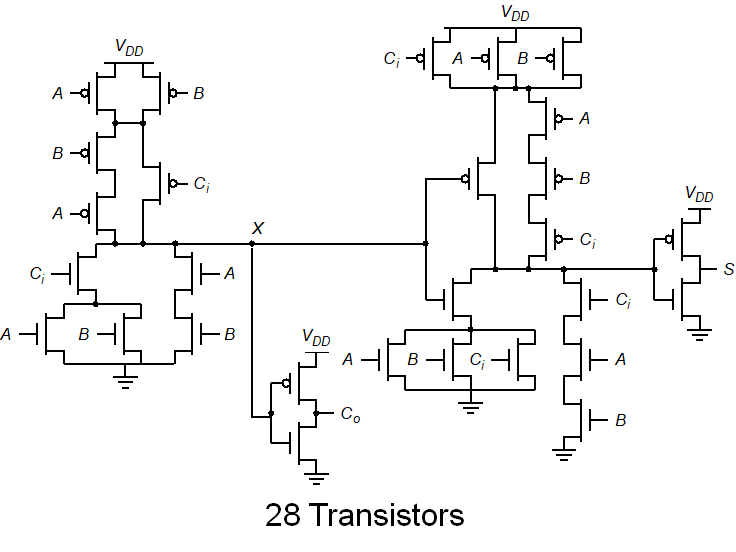

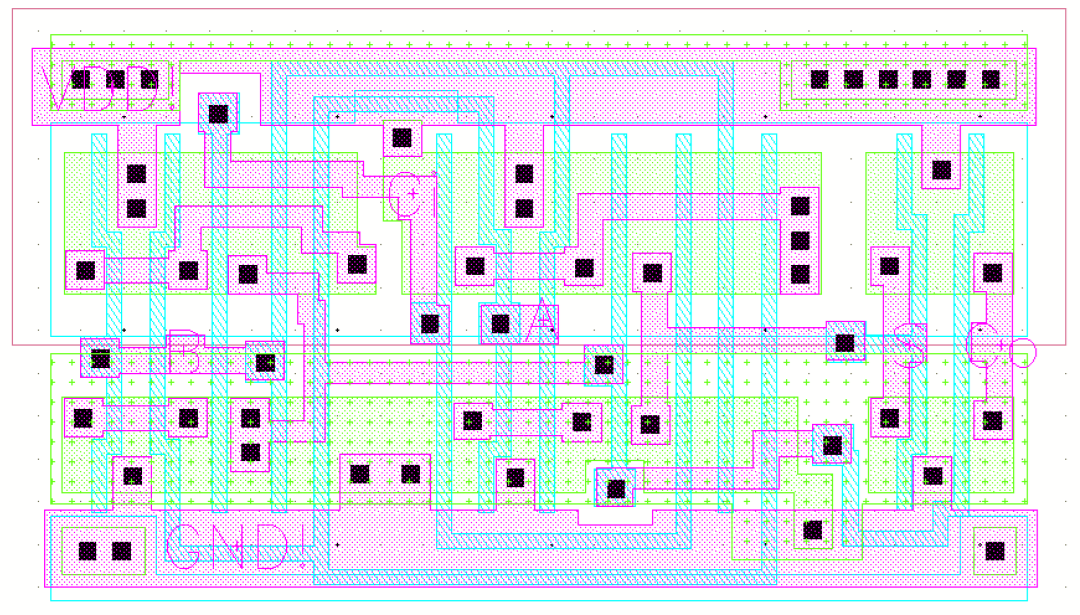

在了解了電路在芯片上簡單的連接方式后,可以想象,對于大規模的集成電路,只是會使用更多層的金屬覆蓋完成更多晶體管連接的。在實際制作芯片時,先使將底層的晶體管制作完成,即在純凈的硅片上使用離子注入(注入磷原子或硼原子)的方式形成襯底區域,然后再將柵極制作完成,最后再一次注入形成源區和漏區,采用多晶硅材料的制作的柵區(Gate)有阻擋離子注入的作用,因此第二次注入源區和漏區時不會影響柵下面的溝道區域。在底層晶體管制作完成后,就進行一層一層金屬的覆蓋將晶體管連接成電路,不同層金屬之間采用絕緣介質SiO2將它們隔開,只在需要連接的點處采用通孔將不同層金屬連接在一起,這樣就完成了一個芯片基本要素的設計,后期的芯片防護設計與封裝這里就不作詳細闡述了。如下左圖是一個全加器的電路示意圖,右圖是其對應的版圖,金屬與源極、漏極、柵極采用通孔連接。

(a) (b)圖10 全加器(a)電路示意圖(b)版圖

為什么會被制裁——工藝上的落后

熟悉了芯片的大致制作流程后,那么為什么我們國家會在芯片領域被國外制裁呢?回答這個問題之前,還想介紹一個概念——最小工藝線寬。所謂的最小工藝線寬就是指一個工藝所能光刻的最小尺寸,一般等于溝道的最小寬度,即晶體管的柵的寬度,最小線寬越小,晶體管的功耗越小,工作頻率也越高,這樣芯片的性能也大大提升了。目前為止最先進的工藝是臺積電的5nm工藝線,主要用于制造手機等電子設備的中的高端芯片,一般的普通芯片是用不到這樣先進的工藝的。

***是芯片制作中的關鍵設備,***的精度決定了工藝的最小線寬的大小,我國主要是由于***的限制阻礙了高端芯片的發展,而最先進的***是由荷蘭的ASML公司制造的,并且ASML的EUV***也是整合了各個領域的最尖端技術,比如光學領域最強-德國蔡司的光學組件,美國的掩罩技術龍頭Silicon Valley Group,紫外光源龍頭Cymer等,下圖是一個***的外觀圖

除了光刻技術,離子注入等技術也和國外有一定的差距,我國正通過獨立自主的研究方式來突破國外的技術封鎖,實現芯片的自主化設計。

關于芯片的知識介紹就到這里了,希望這篇文章能讓你對芯片的基本元件、芯片的大致制作流程有了簡單的了解,對芯片領域的發展瓶頸有了清楚的認識。最后希望這篇文章能真正幫助到您!

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51192瀏覽量

427311 -

集成電路

+關注

關注

5392文章

11624瀏覽量

363199 -

半導體

+關注

關注

334文章

27719瀏覽量

222684 -

晶體管

+關注

關注

77文章

9746瀏覽量

138914

原文標題:晶體管分類原理以及芯片應用限制

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶體管的分類與特征

晶體管的分類與特征

關于晶體管的分析,它的分類以及特性分析

Si晶體管的分類與特征

晶體管的分類介紹

晶體管的分類介紹

評論