數字前端設計人員的目標是使用最小的PA達成要求的PF

時間也是一種消耗(PA)

1.PPA到PA和PF

PPA是數字IC設計逃不開的概念,分別是P(Performance)、P(Power)和A(Area),分別代表芯片的性能、功耗和面積。從產品的角度看來,就是用戶基于這塊芯片能獲得什么(Performance),購買成本是多少(Area),使用成本是多少(Power)。我更傾向于將其拆分為兩類,即PF和PA,分別代表功能和消耗:

*PF:即性能(Performance)和功能(Function),這里將原始的Performance拆分為兩個部分。功能(Function)是定性的,即這塊芯片支持什么功能,性能(Performance)是定量的,表示這塊芯片這個功能支持的怎么樣,這兩個指標用來衡量芯片的能力。

*PA:即功耗(Power)和面積(Area),這里使用的就是原始的P和A概念,這兩個指標用來衡量芯片的消耗。

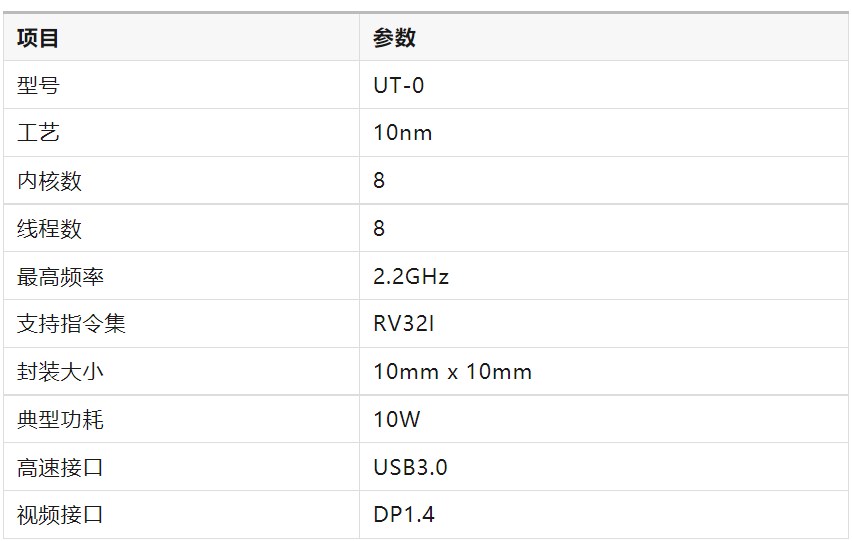

我們簡單的來看一下一塊虛構CPU的簡介,如下表所示:

其中,型號、工藝屬于基本信息,而內核數、線程數、頻率屬于Performance信息,即定量的用于描述性能的信息,以頻率為例,在同架構下和核心、線程數下,一般頻率高的性能高,最高頻率2.2GHz的性能一般高于1.1GHz,但是不影響支持相同的功能,可能僅是運行時間更長。而支持指令集、高速接口、視頻接口屬于Function信息,以指令集為例,這里就不支持RV32E的指令,RV32E指令在這里無法正常運行。而封裝大小屬于Area、典型功耗屬于Power,這些描述了芯片的消耗,一般來說和售價、散熱成本、使用成本掛鉤。

2.PA和PF的取舍

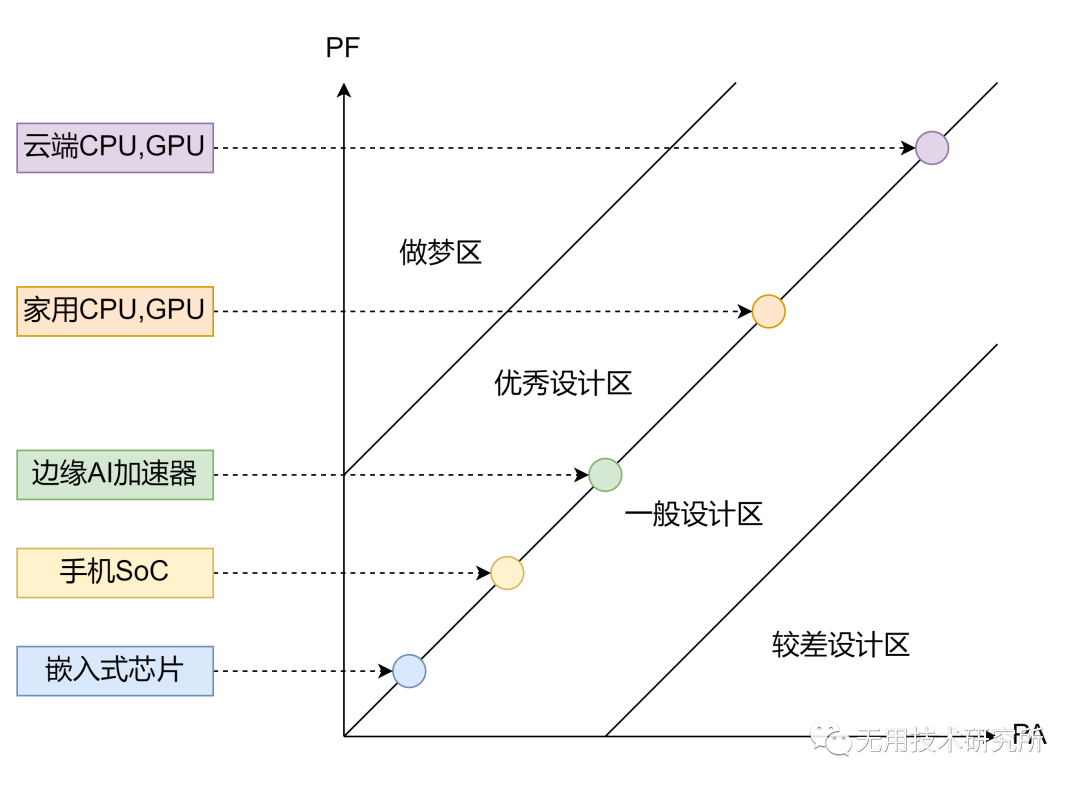

對于PA和PF,不同類型的芯片有不同的取舍,如下圖所示:

真正的高性能低功耗芯片是不存在的,性能的提升必定伴隨消耗的增加,在前摩爾時代,這些消耗可能被工藝的迭代抵消,但后摩爾時代隨著工藝迭代放緩,PA和PF的關系越來越成正相關,甚至線性。因此要求芯片規劃人員給出更為精確的需求,確定芯片的使用場景,把功耗花在最需要的功能上。

低PA-低PF的常見場景為嵌入式設備,以樂鑫ESP32-C3為例,該芯片定義為“極低功耗SoC”,提供WIFI和藍牙解決方案,在Active狀態的功耗約為1W,有單核RSIC-V核心,頻率160MHz,WIFI支持2.4G。而高PA-高PF的典型場景為云端設備,以英特爾至強W-3365為例,其TDP達到了270W,封裝面積為77.5mmx56.5mm,建議售價來到3851美元,而換來的是32核64線程,可支持4TB內存、64條PCIe通道的性能。

3.設計人員眼中的PPA(PAPF)

對于數字前端設計人員,一般會固定PA或PF中的一個進行設計:

*固定PA:給定消耗(例如硅片面積)要求達到最高的性能(例如算力),這種設計模式一般出現在國內科研性質的項目中,尤其常見于MPW模式下的科研性質芯片。在這種模式下每個芯片分到的硅片面積是固定的,一般芯片設計的主導者(一般為教授或研究員)會要求設計人員(一般是學生)在固定的面積下創新架構或微架構,以達到更高的性能。

*固定PF:給定性能(例如支持能力)要求達到最少的消耗(例如功耗),這種設計模式是常規的商業化項目使用的模式。芯片規劃者和設計者處于不同的角色,芯片規劃者基于當前的市場等多種因素規劃芯片的應用場景,再反推出芯片的規格,給設計人員提供需要支持的功能、性能限制和消耗限制。設計人員需要基于芯片需求進行設計,以最小的代價達成需求規劃人員給出的各項需求

固定PF的方式我認為是更加合理的方案,所以對于設計人員而言,核心競爭力是使用更少的PA實現規定的PF;對于超出需求的PF,則不是硬需求,超出的PF一般也會帶來額外的PA,是否應用也需要由芯片規劃人員進行決策。

4.PA的組成和時間消耗

一個芯片的PA由以下幾個部分組成:

1.由需求規定的PF引入的PA:這部分是固定需要引入的,優秀的架構、微架構設計和實現方法可以降低固定PF下的PA消耗

2.由于更高PF引入的PA:這部分是否引入需要芯片規劃人員進行決策,更高的PF帶來的競爭優勢可能被PA的增加沖抵

3.物理性PA消耗:由時鐘樹、復位樹、供電部分引入的PA消耗

4.質量性PA消耗:用于提高設計質量的PA,例如DFT、MBIST等標準化測試電路,自定義測試接口,Debug信號,保護電路等用于提升質量帶來的PA消耗

5.時間性PA消耗:由于使用IP、代碼復用引入的PA消耗,后文會詳細描述

6.物理設計PA消耗:由后端人員引入的PA消耗,一般為前端不可見內容,例如由于繞線資源不足產生的額外面積等

對于前端設計人員來說,主要的工作是權衡1、2、4、5四個點。需要注意的是設計時間在廣義上也是一種成本,隨著摩爾定律放緩,一代架構一代工藝的升級道路已經越來越艱難,對設計的迭代速度也提升了要求,現在流行的先進封裝、chiplet、IP、硬件敏捷開發都從不同的角度提升了設計的迭代速度。

以IP為例,對于類似的功能,使用IP和定制代碼實現相同的PF,IP消耗的PA一定大于等于定制代碼,但是對于一個IP能覆蓋的多個類似的功能,如果都使用定制代碼開發,會引入額外的時間消耗(包括設計實現消耗和驗證時間消耗),因此很多情況下會使用IP以一定的PA為代價,降低硬件的開發時間。

-

IC設計

+關注

關注

38文章

1302瀏覽量

104285 -

MPW

+關注

關注

0文章

11瀏覽量

10870 -

PPA

+關注

關注

0文章

21瀏覽量

7513 -

ESP32

+關注

關注

18文章

978瀏覽量

17525 -

RSIC-V

+關注

關注

4文章

14瀏覽量

6557

發布評論請先 登錄

相關推薦

棄子爭先”與“田忌賽馬”:中國數字前端EDA如何加速發展

數字前端生存指南—PPA

數字前端生存指南—PPA

評論