什么是D觸發(fā)器?

D觸發(fā)器(D Flip-Flop)是一種數(shù)字電子電路,用于延遲其輸出信號(hào)(Q)的狀態(tài)變化,直到時(shí)鐘輸入信號(hào)的下一個(gè)上升沿出現(xiàn)。

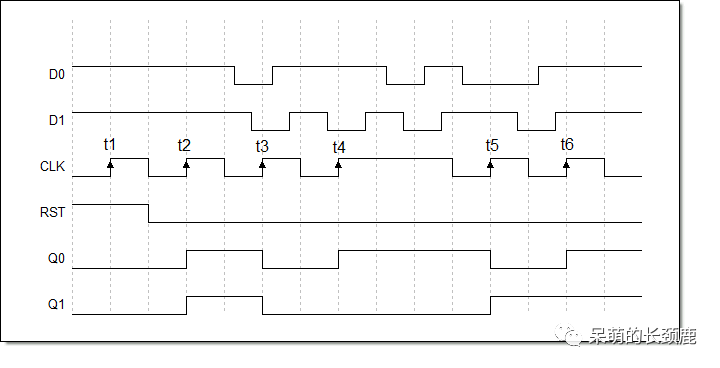

輸出Q在輸入CLK的每個(gè)上升沿時(shí)保存輸入D的數(shù)值,等到輸入CLK的下一個(gè)上升沿出現(xiàn)才會(huì)重新讀取輸入D的數(shù)值,輸入RST為1時(shí)輸出Q輸出值為0且保持不變。

時(shí)間圖如下:

特征表如下:

其中:RST:重置, CLK:時(shí)鐘, D0、D1:輸入 Q0、Q1:輸出

*假設(shè)最初 RST 是高電平 ( RST = 1),無(wú)論D0 和 D1是否高電平,輸出 Q0 和 Q1 是低電平 (Q = 0);

*當(dāng)輸入RST為低電平(RST = 0),在CLK脈沖的上升沿處,Q0=D0,Q1=D1,并保持?jǐn)?shù)值到下一個(gè)CLK脈沖。

源代碼如下:

FUNCTION_BLOCK "FF2E"

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

D0 : Bool;

D1 : Bool;

CLK : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q0 : Bool;

Q1 : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST THEN

#Q0 := FALSE;

#Q1 := FALSE;

ELSIF #CLK AND NOT #edge THEN

#Q0 := #D0;

#Q1 := #D1;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

-

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

48020 -

RST

+關(guān)注

關(guān)注

0文章

31瀏覽量

7425 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

453瀏覽量

28664 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17236

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

D觸發(fā)器/J-K觸發(fā)器的功能測(cè)試及其應(yīng)用

JK觸發(fā)器 D觸發(fā)器 RS觸發(fā)器 T觸發(fā)器 真值表

D觸發(fā)器工作原理是什么?

D觸發(fā)器組成T和J-K觸發(fā)器電路圖

J-K觸發(fā)器組成D觸發(fā)器電路圖

D觸發(fā)器開(kāi)關(guān)電路圖 - 副本

什么是D觸發(fā)器,D觸發(fā)器如何工作的?

D觸發(fā)器,請(qǐng)查收!

D觸發(fā)器,請(qǐng)查收!

評(píng)論