什么是JKE觸發(fā)器?

FF_JKE是一個(gè)具有異步設(shè)置(SET)和重置(RST)輸入的邊緣觸發(fā)的JK觸發(fā)器(JK Flip-Flop), 僅SET=1時(shí),輸出Q=1;只要RST=1,輸出Q=0。RST=SET=0時(shí),在CLK上升沿到來時(shí),則:

- 當(dāng)J=K=0 ,輸出Q保持不變;

- 當(dāng)J=1 且 K=0 ,輸出Q=1;

- 當(dāng)J=0 且 K=1 ,輸出Q=0;

- 當(dāng)J= K=1 ,輸出Q取反;

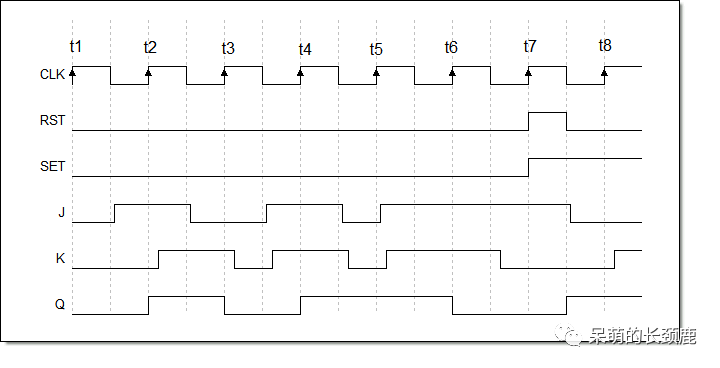

時(shí)間圖如下:

特征表如下:

其中: CLK:時(shí)鐘, RST:重置, SET: 設(shè)置 , J、K:輸入 , Q:輸出

- 假設(shè)最初 輸入都為0,輸出 Q = 0;

- 在t1處,J=K=0 ,輸出Q保持不變;

- 在t2處,J=1 且 K=0 ,輸出Q=1;

- 在t3處,J=0 且 K=1 ,輸出Q=0;

- 在t4處,J= K=1,輸出Q取反,輸出Q=1;

- 在t5處,J=K=0 ,輸出Q保持不變,輸出Q=1;

- 在t6處,J= K=1,輸出Q取反,輸出Q=0;

- 在t7處,RST=1,輸出Q=0;

- 在t8處,SET=1且RST=0,輸出Q=1;

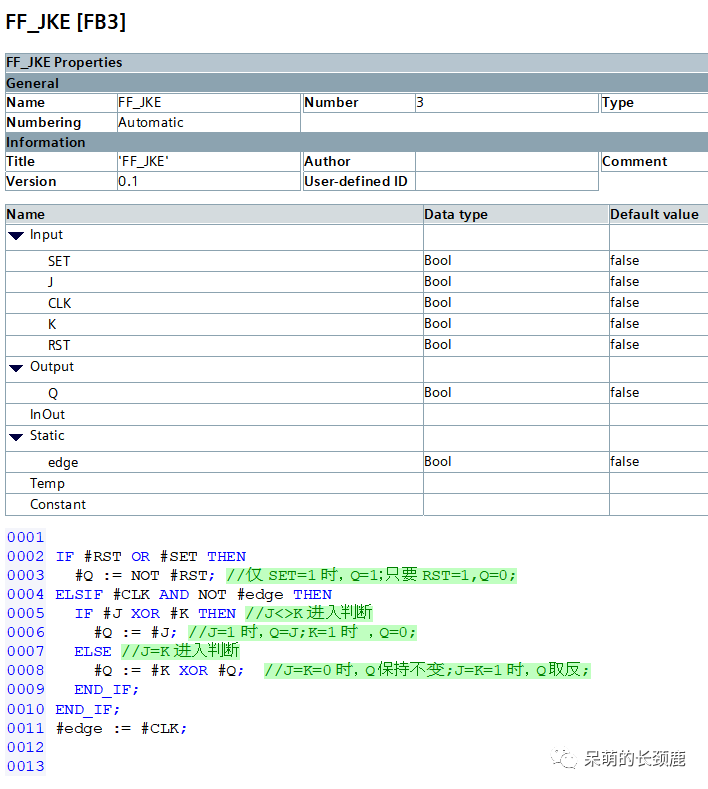

源代碼如下:

FUNCTION_BLOCK "FF_JKE"

TITLE = 'FF_JKE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

SET : Bool;

J : Bool;

CLK : Bool;

K : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST OR #SET THEN

#Q := NOT #RST; //僅SET=1時(shí),Q=1;只要RST=1,Q=0;

ELSIF #CLK AND NOT #edge THEN

IF #J XOR #K THEN //J< >K進(jìn)入判斷

#Q := #J; //J=1時(shí),Q=J;K=1時(shí) ,Q=0;

ELSE //J=K進(jìn)入判斷

#Q := #K XOR #Q; //J=K=0時(shí),Q保持不變;J=K=1時(shí),Q取反;

END_IF;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

JK觸發(fā)器

+關(guān)注

關(guān)注

1文章

43瀏覽量

15981 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2003瀏覽量

61347 -

RST

+關(guān)注

關(guān)注

0文章

31瀏覽量

7425 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17236

發(fā)布評論請先 登錄

相關(guān)推薦

JK觸發(fā)器,JK觸發(fā)器是什么意思

JK觸發(fā)器,JK觸發(fā)器是什么意思

1.主從JK觸發(fā)器主從結(jié)構(gòu)觸發(fā)器也可以徹底解決直接控制,防止空翻。這里以性能優(yōu)良、廣泛使用的主從JK觸發(fā)器

發(fā)表于 03-08 13:36

?6901次閱讀

D觸發(fā)器,D觸發(fā)器是什么意思

D觸發(fā)器,D觸發(fā)器是什么意思

邊沿D 觸發(fā)器: 電平觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高

發(fā)表于 03-08 13:53

?4996次閱讀

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

主從RS觸發(fā)器

發(fā)表于 03-08 14:00

?3.1w次閱讀

施密特觸發(fā)器,施密特觸發(fā)器是什么意思

施密特觸發(fā)器,施密特觸發(fā)器是什么意思

施密特觸發(fā)器也有兩個(gè)穩(wěn)定狀態(tài),但與一般觸發(fā)器不同的是,施密特觸發(fā)器采用電位

發(fā)表于 03-08 14:14

?1981次閱讀

觸發(fā)器的分類, 觸發(fā)器的電路

觸發(fā)器的分類, 觸發(fā)器的電路

雙穩(wěn)態(tài)器件有兩類:一類是觸發(fā)器,一類是鎖存器。鎖存器是觸發(fā)器的原

發(fā)表于 03-09 09:59

?1698次閱讀

什么是邊沿觸發(fā)器_邊沿D觸發(fā)器介紹

邊沿觸發(fā)器,指的是接收時(shí)鐘脈沖CP 的某一約定跳變(正跳變或負(fù)跳變)來到時(shí)的輸入數(shù)據(jù)。在CP=l 及CP=0 期間以及CP非約定跳變到來時(shí),觸發(fā)器不接收數(shù)據(jù)的觸發(fā)器。具有下列特點(diǎn)的觸發(fā)器

發(fā)表于 01-31 09:02

?7.2w次閱讀

觸發(fā)器的作用_觸發(fā)器的特點(diǎn)介紹

本文開始介紹了觸發(fā)器的定義和觸發(fā)器的特點(diǎn),其次闡述了觸發(fā)器的分類和觸發(fā)器的作用,最后介紹了觸發(fā)器的工作原理。

發(fā)表于 03-27 17:35

?2.2w次閱讀

電平觸發(fā)器,脈沖觸發(fā)器和邊沿觸發(fā)器的觸發(fā)因素是什么

脈沖觸發(fā)器由兩個(gè)相同的電平觸發(fā)的SR觸發(fā)器組成,其中左SR觸發(fā)器成為主觸發(fā)器,右手側(cè)稱為從觸發(fā)器

觸發(fā)器的觸發(fā)順序是什么

不同類型的觸發(fā)器可能有不同的執(zhí)行順序。例如,對于同一個(gè)表上的多個(gè)觸發(fā)器,插入觸發(fā)器(INSERT trigger)可能先于更新觸發(fā)器(UPDATE trigger)執(zhí)行。

t觸發(fā)器和jk觸發(fā)器的區(qū)別和聯(lián)系

觸發(fā)器是數(shù)字電路中常用的組合邏輯電路,在現(xiàn)代電子系統(tǒng)中有著廣泛的應(yīng)用。其中,最常用的兩種觸發(fā)器是T觸發(fā)器和JK觸發(fā)器。本文將詳細(xì)介紹T觸發(fā)器

如何用jk觸發(fā)器構(gòu)成t觸發(fā)器?t觸發(fā)器邏輯功能有哪些

如何用JK觸發(fā)器構(gòu)成T觸發(fā)器 JK觸發(fā)器是一種基本的觸發(fā)器電路,由兩個(gè)輸入端J和K控制,以及兩個(gè)輸出端Q和Q'組成。JK觸發(fā)器的輸出可以持續(xù)

t觸發(fā)器與d觸發(fā)器的區(qū)別和聯(lián)系

在數(shù)字電路設(shè)計(jì)中,觸發(fā)器是一種非常重要的存儲(chǔ)元件,用于存儲(chǔ)一位二進(jìn)制信息。觸發(fā)器的種類很多,其中最為常見的是T觸發(fā)器(Toggle Flip-Flop)和D觸發(fā)器(Data Flip-

t觸發(fā)器變?yōu)閐觸發(fā)器的條件

在數(shù)字電路設(shè)計(jì)中,觸發(fā)器是一種非常重要的存儲(chǔ)元件,用于存儲(chǔ)一位二進(jìn)制信息。觸發(fā)器的種類很多,其中最為常見的有JK觸發(fā)器、D觸發(fā)器和T觸發(fā)器等

d觸發(fā)器和jk觸發(fā)器的區(qū)別是什么

引言 數(shù)字電路是現(xiàn)代電子技術(shù)的基礎(chǔ),廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。觸發(fā)器是數(shù)字電路中的一種基本邏輯元件,具有存儲(chǔ)和傳遞信息的功能。 觸發(fā)器的基本概念 觸發(fā)器是一種具有記憶功能的數(shù)字電路元件

怎么用jk觸發(fā)器變成t觸發(fā)器

將JK觸發(fā)器變成T觸發(fā)器,主要涉及到對JK觸發(fā)器的輸入端口進(jìn)行適當(dāng)?shù)倪B接和配置,以實(shí)現(xiàn)T觸發(fā)器的邏輯功能。以下是將JK觸發(fā)器轉(zhuǎn)換為T

什么是JKE觸發(fā)器?

什么是JKE觸發(fā)器?

評論