接著上一篇“AMD Versal系列CIPS IP核介紹”文章來進一步講解如何來建立CIPS IP核示例工程。

利用CIPS IP核的板卡自動化以及預置功能,生成VCK180 DDRMC基于GUI界面的調試工程。當然該工程亦可以根據AMD官網例程TCL文件來完成。

本文是基于Vivado 2022.1版本進行演示,其他版本界面可能會有細小差異。

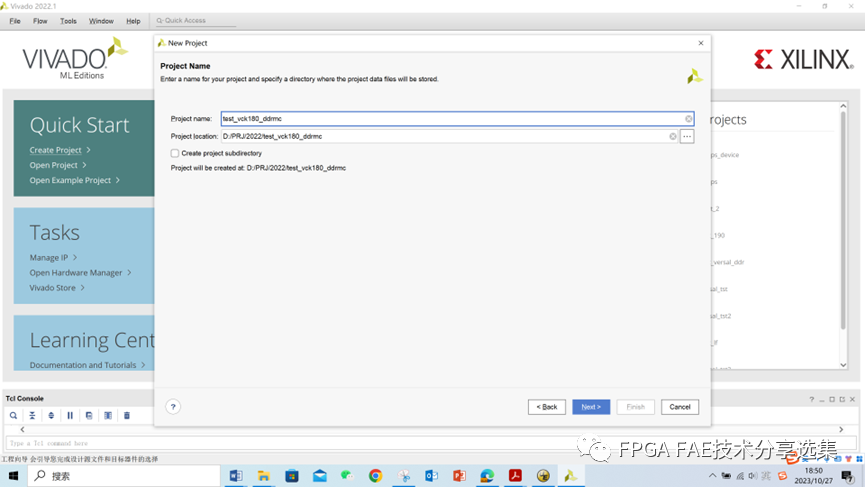

Step1 新建工程

工程名字和路徑需要字符形式出現,同時路徑不能太長。

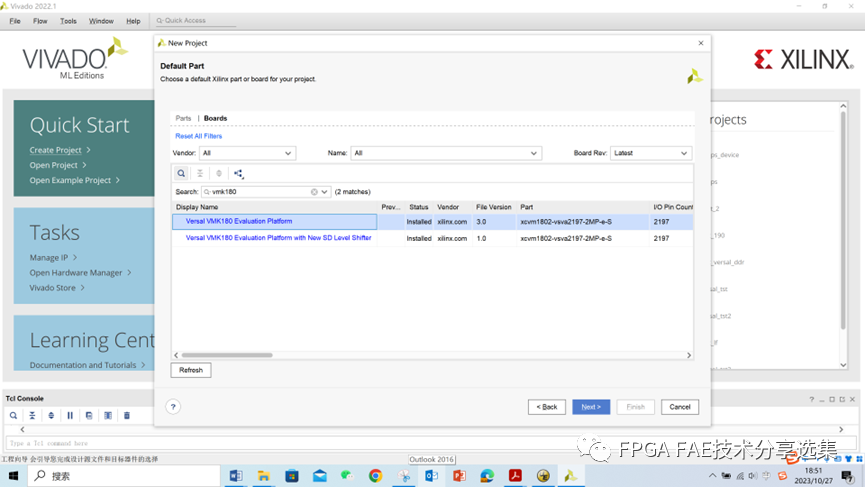

Step2 選定工程板卡

由于我們是做DEMO目的,所以板卡選擇Versal Prime系列的VMK180;當然也可以選擇其他Versal系列的開發板,或者客戶自定義。

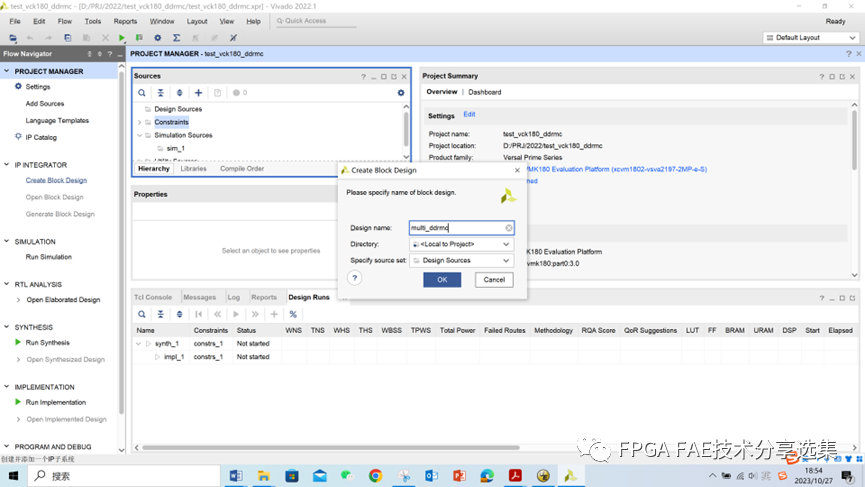

Step3 創建Block Design工程

使用Block Design流程可以很方面的增減IP,給設計帶來很高的靈活性并節約寫代碼時間。

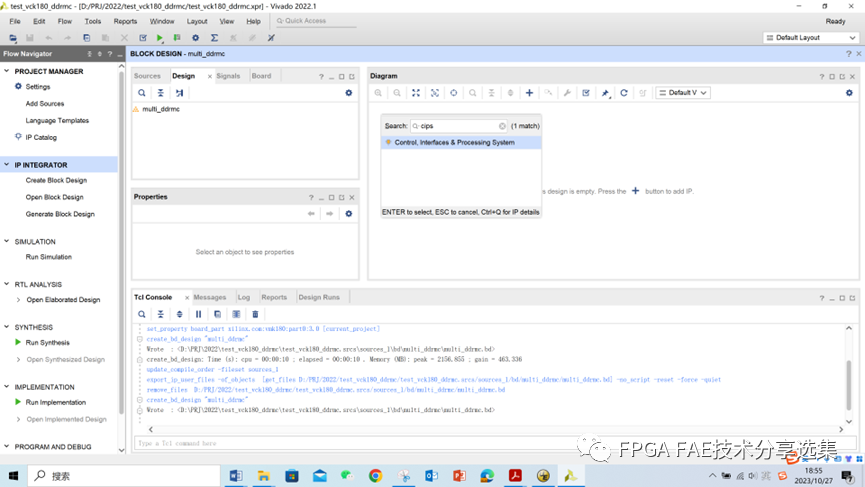

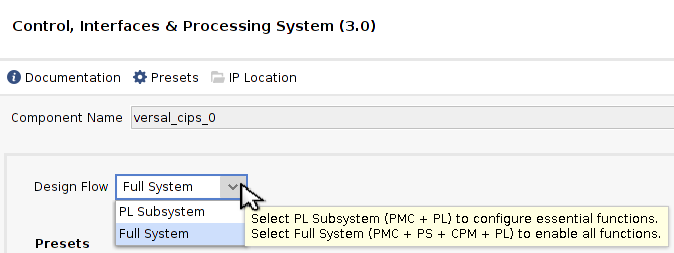

Step4 加入CIPS IP核

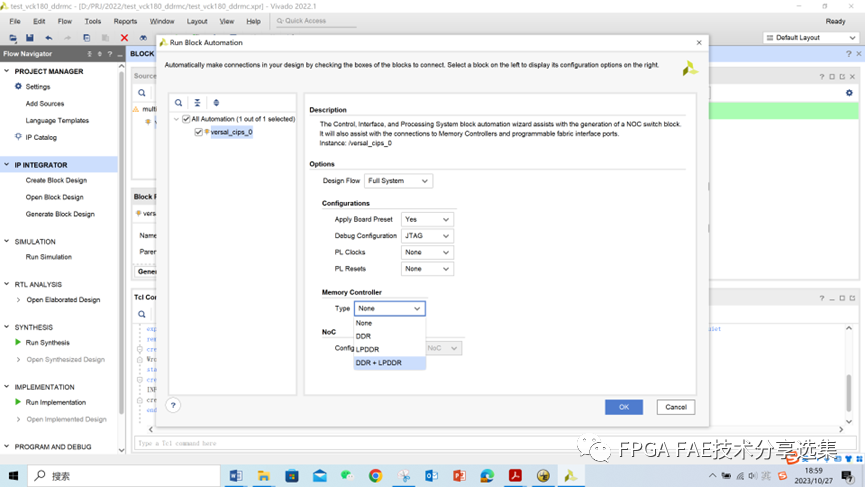

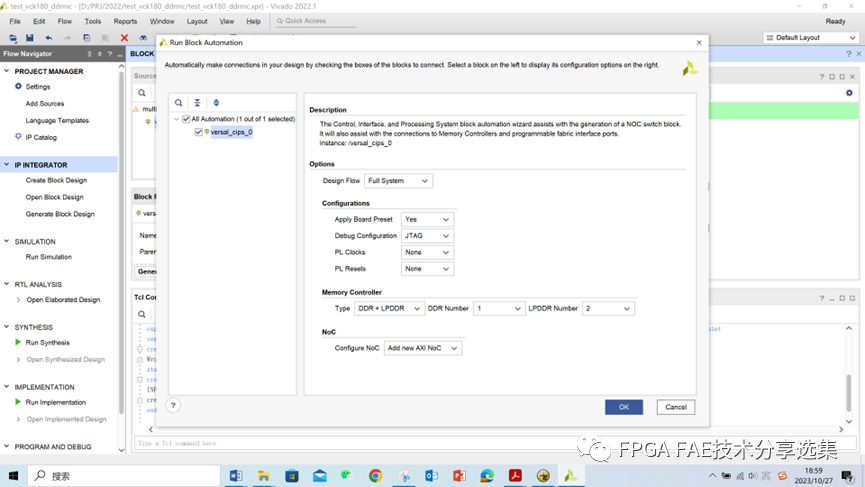

Step5 運行Automation與預置功能

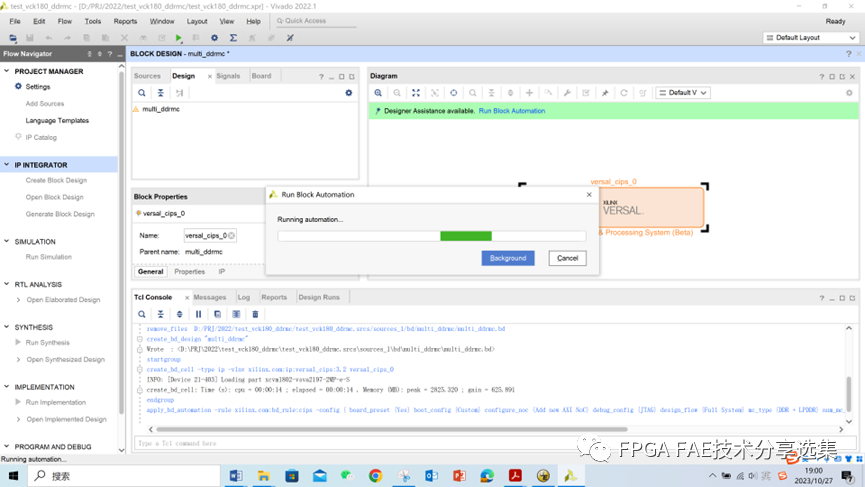

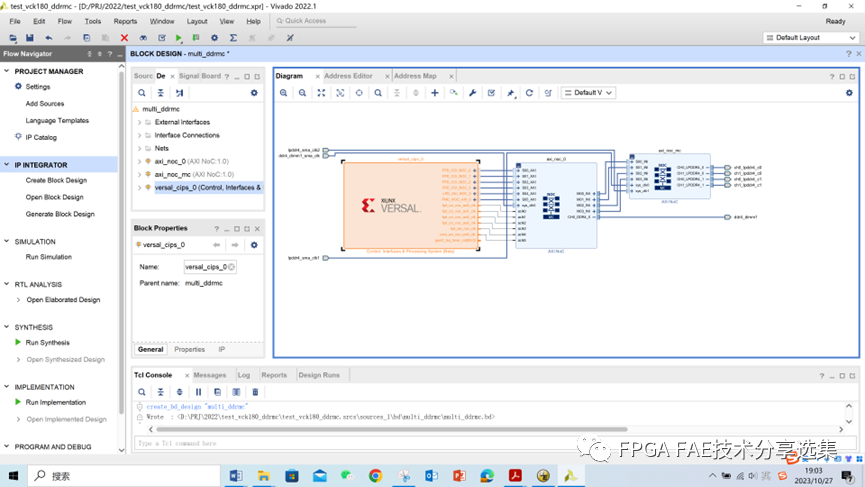

Step6 生成工程Diagram

Runing Automation可以自動生成CIPS的已定義的接口,同時可以跟其他IP進行互連,避免人工操作。

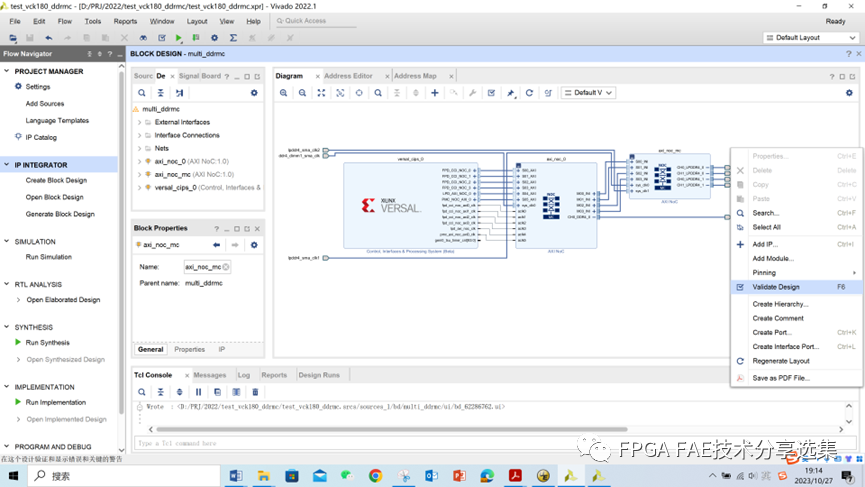

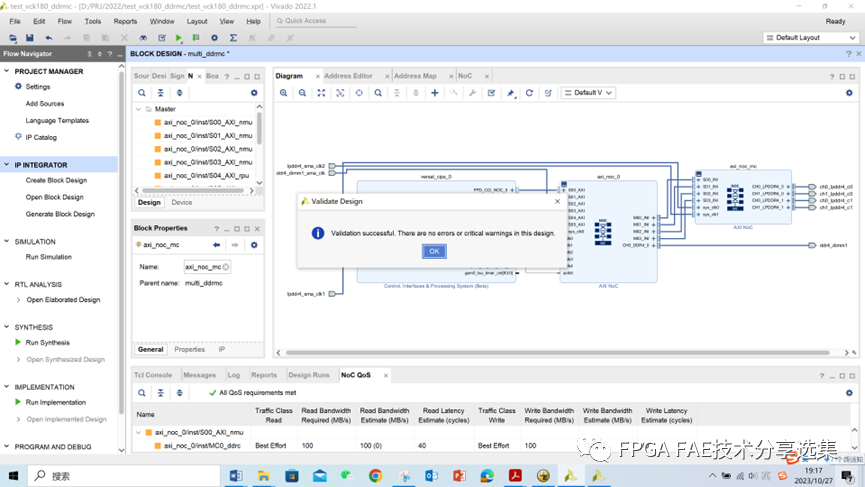

Step7 設計驗證

運行Vaildate Design功能可以檢查Block Design設計是否有誤;需要把錯誤全部消除掉才可以進入下面流程。

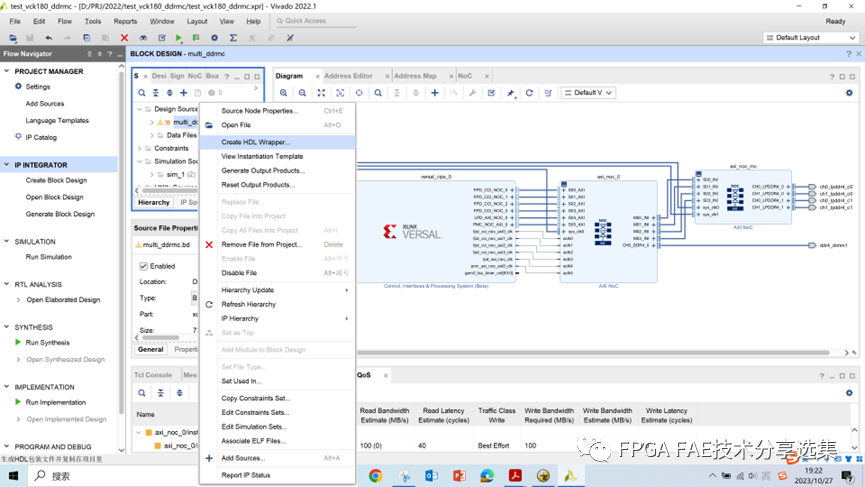

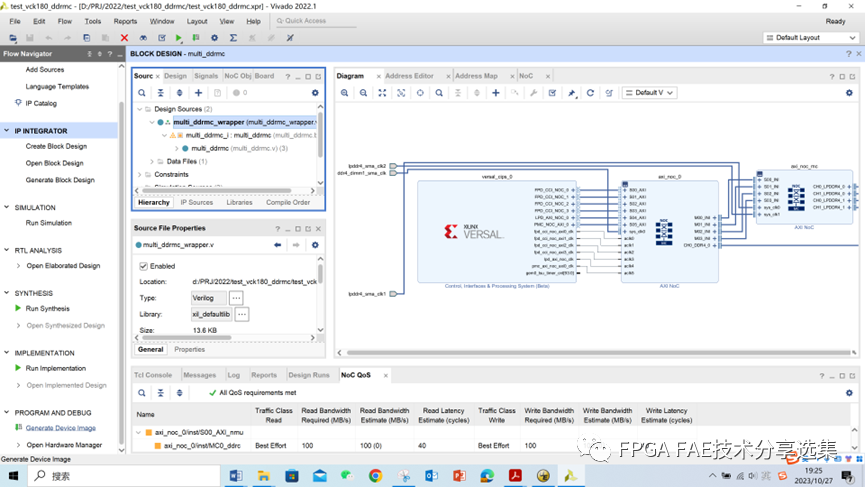

Step8 生成HDL Wrapper

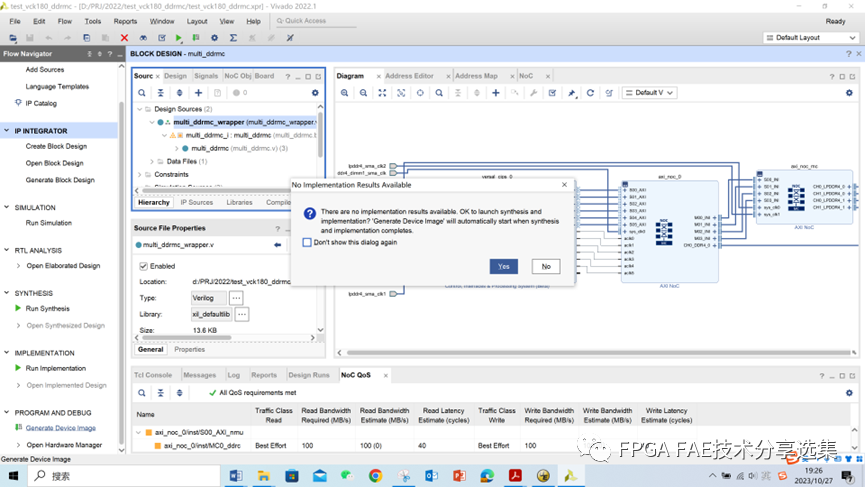

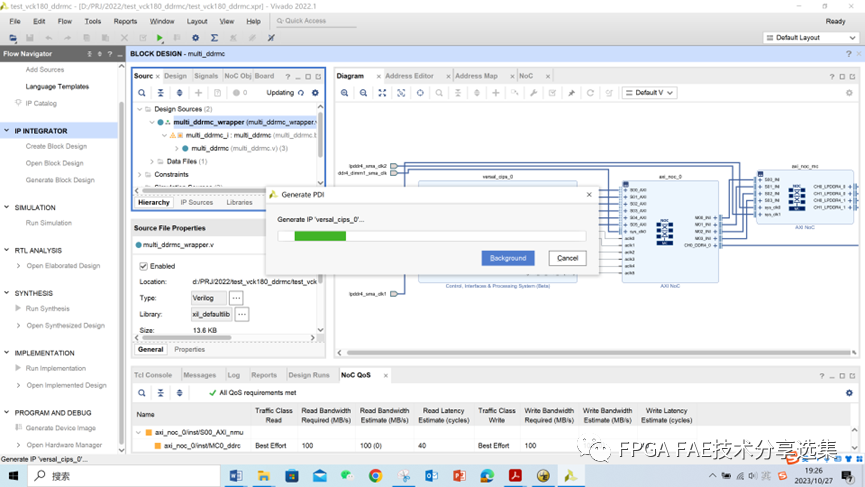

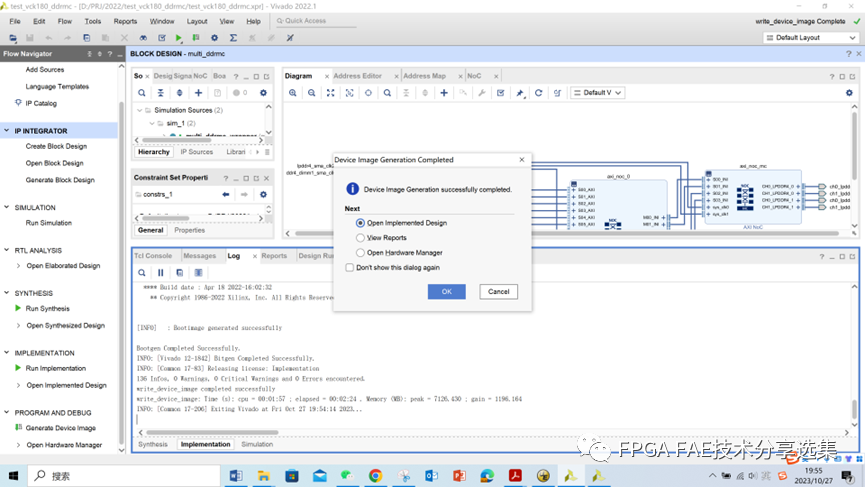

Step9 生成Device Image

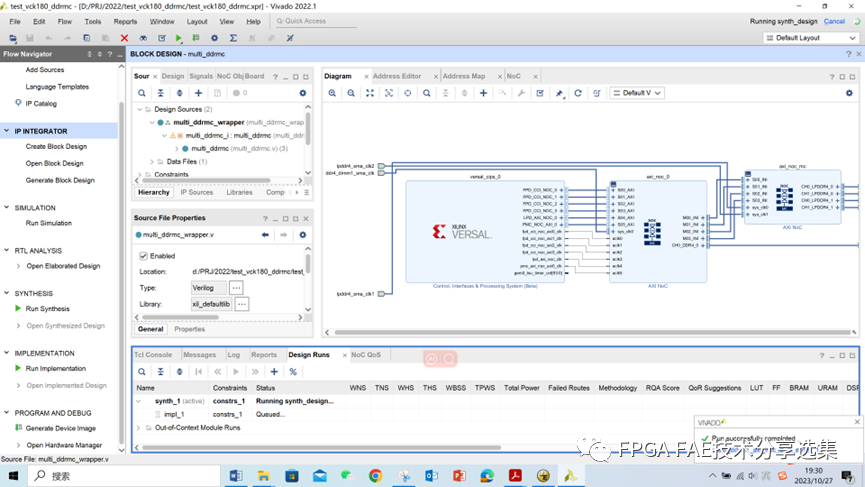

Step10 成功生成Device Image

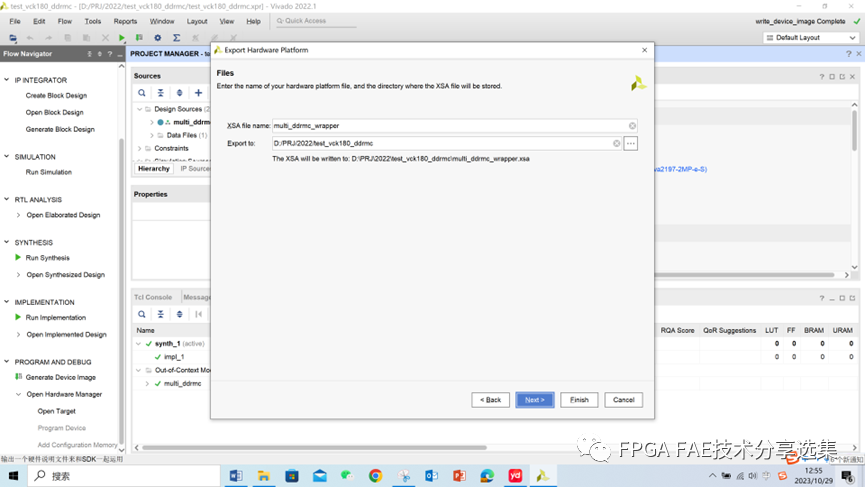

Step11 導出硬件平臺

成功生成xsa文件后,軟件工程師就可以使用xsa進行后續軟件開發工作。

審核編輯:湯梓紅

-

amd

+關注

關注

25文章

5495瀏覽量

134628 -

調試

+關注

關注

7文章

589瀏覽量

34060 -

IP核

+關注

關注

4文章

331瀏覽量

49634 -

Versal

+關注

關注

1文章

163瀏覽量

7710

原文標題:AMD Versal系列CIPS IP核建立示例工程

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

利用設計網關的 IP 內核在 Xilinx VCK190 評估套件上加速人工智能應用

CIPS 3.0變更日志和移植信息解決方案

Versal CPM AXI Bridge模式的地址轉換

設置AMD以太網IP核的Pause幀處理

AMD Versal? Adaptive SoC CPM PCIE PIO EP設計CED示例

AMD推出第二代Versal Premium系列

AMD Vivado Design Suite 2024.2全新推出

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD Versal系列CIPS IP核建立示例工程

AMD Versal系列CIPS IP核建立示例工程

評論