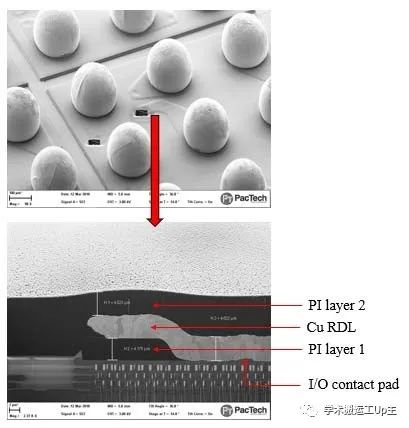

Redistribution layer (再分布層,RDL),是添加到集成電路或微芯片中以重新分配電氣連接的金屬層。這種RDL技術(shù)是一種用于集成電路(IC)的先進(jìn)封裝解決方案,允許將多個(gè)芯片集成到單個(gè)封裝中。它是在介電層頂部創(chuàng)建圖案化金屬層的過程,該金屬層將 IC 的輸入/輸出 (I/O) 重新分配到新位置。新位置通常位于芯片的邊緣,這允許使用標(biāo)準(zhǔn)表面貼裝技術(shù) (SMT) 將 IC 連接到印刷電路板 (PCB)。RDL 技術(shù)使設(shè)計(jì)人員能夠以緊湊、高效的方式放置芯片,從而減少器件的整體尺寸。

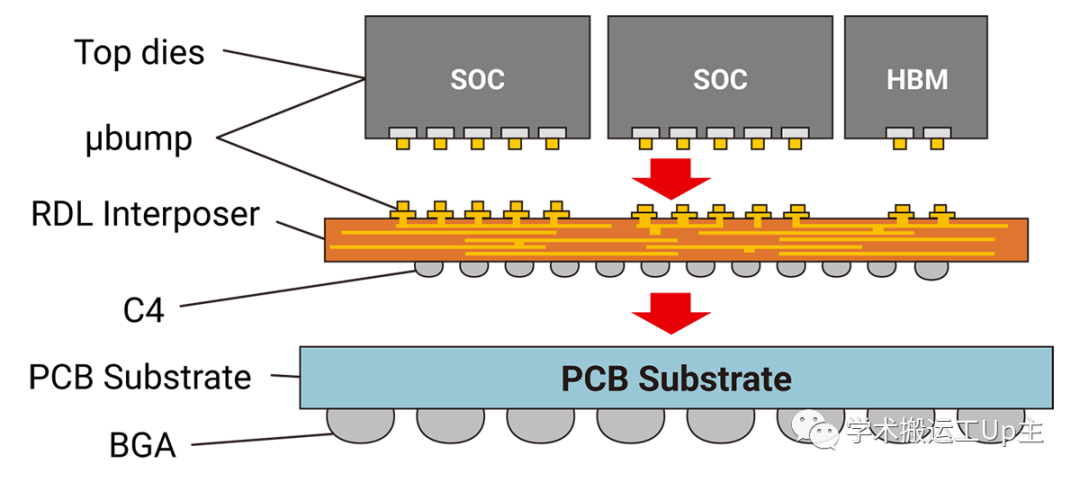

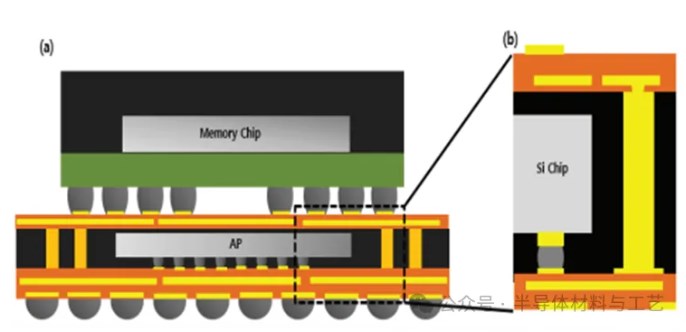

在芯片設(shè)計(jì)和制造中,再分布層 (RDL) 在擴(kuò)展和互連 XY 平面方面發(fā)揮著關(guān)鍵作用。如下圖是CoWoS-R的圖示,這是臺(tái)積電開發(fā)的一種3D集成技術(shù),可在單個(gè)封裝中堆疊多個(gè)芯片。(來源:臺(tái)積電)

RDL 技術(shù)帶來以下優(yōu)勢(shì):

(1). 重新分配 I/O 連接: I/O(輸入/輸出)焊盤是芯片引腳處理模塊,通常分布在芯片的邊緣或外圍。它們可以處理芯片引腳的信號(hào),并在處理后將芯片的信號(hào)輸出到引腳。RDL 有助于將 I/O 連接從芯片重新分配到封裝。RDL 將芯片上的焊盤連接到封裝引線或焊球,從而簡(jiǎn)化組裝和提高 IC 的性能。

這對(duì)于鍵合線工藝來說自然是方便的,但對(duì)于倒裝芯片來說卻有些挑戰(zhàn)。因此,RDL成為這一時(shí)刻的關(guān)鍵。它在芯片表面沉積金屬層和相應(yīng)的介電層,形成金屬線,并將IO端口重新設(shè)計(jì)到一個(gè)新的、更寬敞的區(qū)域,形成表面陣列布局。

(2). 路由信號(hào)和電源: 此外,RDL還提供了一種在IC內(nèi)路由信號(hào)和電源的方法。隨著IC變得越來越復(fù)雜,需要更多的I/O連接,RDL的使用變得越來越重要。它們用于廣泛的應(yīng)用,例如微處理器、存儲(chǔ)芯片和傳感器。

(3). 減少占用面積: RDL 技術(shù)允許將多個(gè)芯片集成到單個(gè)封裝中,從而減小器件的整體尺寸。這使設(shè)計(jì)人員能夠創(chuàng)建更小、更緊湊的電子設(shè)備,這對(duì)于智能手機(jī)、可穿戴設(shè)備和物聯(lián)網(wǎng)設(shè)備等應(yīng)用至關(guān)重要。

(4). 提高電氣性能: RDL 技術(shù)使設(shè)計(jì)人員能夠以緊湊而高效的方式放置芯片,從而縮短互連的長(zhǎng)度。這反過來又減少了信號(hào)延遲并提高了器件的電氣性能。RDL技術(shù)還降低了寄生電容和電感,從而提高了器件的信號(hào)完整性。

(5). 降低成本: RDL技術(shù)消除了引線鍵合和倒裝芯片鍵合的需要,這些工藝既昂貴又耗時(shí)。RDL技術(shù)還減少了器件所需的元件數(shù)量,從而進(jìn)一步降低了器件的成本。RDL 技術(shù)是一種經(jīng)濟(jì)高效的解決方案,用于創(chuàng)建需要小尺寸的高性能 IC。

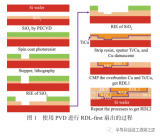

RDL 技術(shù)是一個(gè)復(fù)雜的過程,涉及許多步驟,例如介電沉積、金屬沉積、圖案化和蝕刻。再分布層技術(shù)基于工藝來說,一般有兩種類型的再分布層 (RDL) 技術(shù):扇入和扇出。扇入式 RDL 技術(shù)用于封裝單個(gè)芯片,而扇出式 RDL 技術(shù)用于封裝多個(gè)芯片。

(1). 扇入式 RDL 技術(shù):扇入式 RDL 技術(shù)用于封裝單個(gè)芯片。扇入式 RDL 技術(shù)也稱為晶圓級(jí)封裝 (WLP),它是直接在晶圓上建立封裝的過程。扇入式 RDL 技術(shù)是一種經(jīng)濟(jì)高效的解決方案,用于創(chuàng)建小型和薄型封裝。

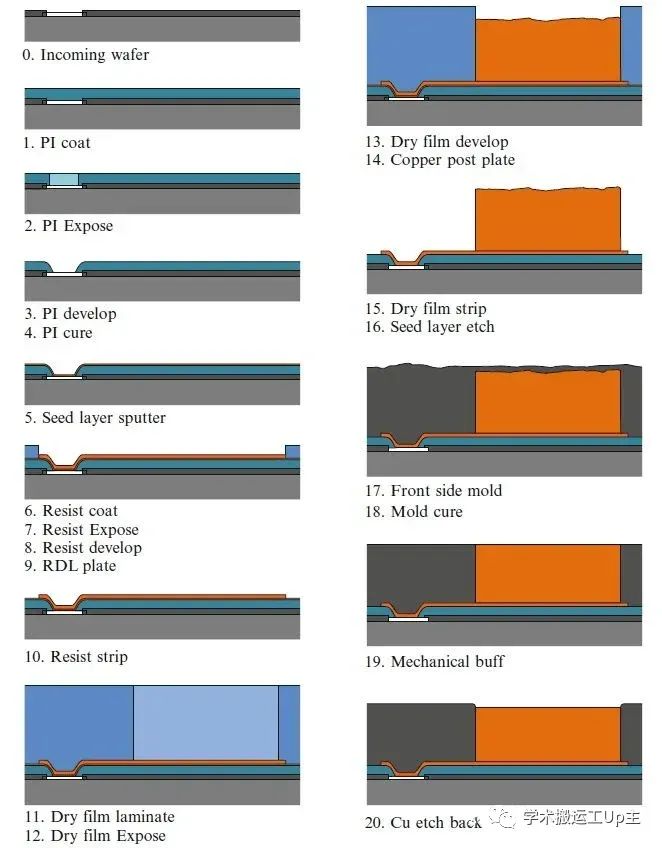

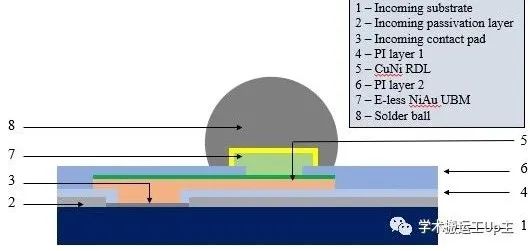

扇入式 RDL 工藝用于生產(chǎn)先進(jìn)的封裝解決方案,例如晶圓級(jí)芯片級(jí)封裝 (WLCSP) 和系統(tǒng)級(jí)封裝 (SiP) 設(shè)計(jì)。它允許更高的集成度、更小的外形尺寸和更高的半導(dǎo)體器件性能。該過程涉及以下多個(gè)步驟:

該過程從進(jìn)料晶圓開始,然后在步驟 1 中涂覆 PI(光刻膠絕緣體)。接下來是第 2 步的 PI 曝光、第 3 步的 PI 顯影以及第 4 步的 PI 固化。

在步驟5中,將種子層濺射到晶圓上,然后在步驟6中涂上抗蝕劑。然后在步驟7中暴露光刻膠,在步驟8中顯影,并在步驟9中鍍上RDL。

之后,在步驟10中剝離光刻膠,并在步驟11中將干膜層壓到晶圓上。然后在步驟12中暴露干膜,并在步驟13中顯影。接下來,在步驟14中將銅柱鍍?cè)诰A上,并在步驟15中剝離干膜。

在步驟16中,對(duì)種子層進(jìn)行蝕刻,在步驟17中,創(chuàng)建正面模具。然后在步驟18中固化模具,并在步驟19中對(duì)晶圓進(jìn)行機(jī)械拋光。最后,在步驟20中,多余的銅被蝕刻回去,完成扇入式RDL工藝流程。

扇入式 RDL 技術(shù)適用于傳感器、MEMS 器件、射頻器件、微處理器和存儲(chǔ)器件等應(yīng)用。

(2). 扇出 RDL 技術(shù):扇出 RDL 技術(shù)用于封裝多個(gè)芯片。扇出 RDL 技術(shù)也稱為晶圓級(jí)扇出 (WLFO),它是在重組晶圓上創(chuàng)建封裝的過程。扇出式 RDL 技術(shù)是一種經(jīng)濟(jì)高效的解決方案,用于創(chuàng)建具有小尺寸的高性能封裝。

與扇入式 RDL 工藝類似,扇出式 RDL 工藝也是一種創(chuàng)建具有更多連接的更小、性能更高的芯片封裝的方法。以下是制造步驟:

- 晶圓探針:這是對(duì)晶圓的初步測(cè)試,以確保其符合所需的規(guī)格,然后再進(jìn)行后續(xù)的加工步驟。

- 晶圓背磨:將晶圓的背面研磨到規(guī)定的厚度,以減小封裝的厚度。

- 晶圓切割:將晶圓切割成單獨(dú)的芯片。

- KGD(已知合格芯片)拾取和放置:將合格的芯片拾取并轉(zhuǎn)移到帶有粘合劑的載體晶圓上。

5a. 晶圓模具:將芯片附著在載體晶圓上的晶圓用介電材料模制而成,形成扇出結(jié)構(gòu)。

5b. 載體和臨時(shí)膠粘劑去除:將載體晶圓從扇出晶圓上取下,并去除過程中使用的任何臨時(shí)膠粘劑。

5c. 扇出晶圓清潔:扇出晶圓經(jīng)過清潔以去除任何殘留的顆粒或雜質(zhì)。

- 聚合物1涂層:在扇出晶圓的表面涂上聚合物層,作為介電層。

- 聚合物1 成像/顯影/固化:使用光刻技術(shù)對(duì)聚合物層進(jìn)行圖案化,以創(chuàng)建所需的 RDL 結(jié)構(gòu)形狀和尺寸。

- RDL種子層濺射:使用濺射在聚合物層的頂部沉積一層薄薄的銅或其他導(dǎo)電材料。

- 光刻膠涂層:在種子層上涂上一層光刻膠材料。

- 光刻膠成像/顯影:使用光刻技術(shù)對(duì)光刻膠層進(jìn)行圖案化,以創(chuàng)建所需的 RDL 結(jié)構(gòu)形狀和尺寸。

- RDL銅圖案板:使用電鍍將銅沉積在種子層的暴露區(qū)域的頂部,從而形成所需的RDL圖案。

- 光刻膠去除:去除剩余的光刻膠材料,只留下銅RDL圖案。

- 種子層蝕刻:使用蝕刻去除種子層中不需要的部分。

- 聚合物2涂層:在RDL結(jié)構(gòu)的頂部施加另一層聚合物層,作為介電層。

- 聚合物2 成像/顯影/固化:使用光刻技術(shù)對(duì)聚合物層進(jìn)行圖案化,以創(chuàng)建所需的形狀和尺寸的 UBM 結(jié)構(gòu)。

- UBM晶種層濺射:使用濺射在聚合物層的頂部沉積一層薄薄的銅或其他導(dǎo)電材料。

- 光刻膠涂層:在種子層上涂上一層光刻膠材料。

- 光刻膠成像/顯影:光刻技術(shù)對(duì)光刻技術(shù)對(duì)光刻膠層進(jìn)行圖案化,以創(chuàng)建所需的 UBM 結(jié)構(gòu)形狀和尺寸。

- UBM圖案板:使用電鍍將銅沉積在種子層的暴露區(qū)域的頂部,從而形成所需的UBM圖案。

- 光刻膠去除:去除剩余的光刻膠材料,只留下銅UBM圖案。

- 種子層蝕刻:使用蝕刻去除種子層中不需要的部分。

- 助焊劑貼印:將助焊劑材料應(yīng)用于UBM焊盤。

- 錫球掉落:將錫球放在 UBM 焊盤上。

- 回流焊:將焊球加熱熔化,并在 UBM 焊盤和外部引線或凸塊之間形成連接。

- 扇出晶圓探針:對(duì)封裝的IC進(jìn)行測(cè)試,以確保其符合所需的規(guī)格。

- 激光標(biāo)記:使用激光將唯一標(biāo)識(shí)符或條形碼蝕刻在IC表面。

- 晶圓切割:將扇出的晶圓切割成單獨(dú)的封裝。

- 編帶包裝:?jiǎn)蝹€(gè)封裝的 IC 安裝在卷軸上,便于處理和運(yùn)輸。

扇出 RDL 技術(shù)適用于圖形處理器、片上系統(tǒng) (SoC)、存儲(chǔ)設(shè)備、功率器件和 LED 器件等應(yīng)用。

-

集成電路

+關(guān)注

關(guān)注

5392文章

11624瀏覽量

363195 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27719瀏覽量

222676 -

晶圓

+關(guān)注

關(guān)注

52文章

4977瀏覽量

128318 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1028瀏覽量

55009 -

系統(tǒng)級(jí)封裝

+關(guān)注

關(guān)注

0文章

36瀏覽量

9120

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶圓級(jí)封裝中的窄間距RDL技術(shù)

先進(jìn)封裝RDL-first工藝研究進(jìn)展

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

世界級(jí)專家為你解讀:晶圓級(jí)三維系統(tǒng)集成技術(shù)

新型WLCSP電路修正技術(shù)

芯片技術(shù)中就有了“層”的概念是什么?

集微連線:板級(jí)封裝潛力無窮 RDL工藝勇挑大梁

華為一種芯片堆疊工藝解讀

高通量芯片流體分布層結(jié)構(gòu)

淺析扇出封裝和SiP的RDL改進(jìn)與工藝流程

芯片先進(jìn)封裝里的RDL

Manz亞智科技RDL制程打造CoPoS板級(jí)封裝路線, 滿足FOPLP/TGV應(yīng)用于下一代AI需求

Manz亞智科技RDL制程打造CoPoS板級(jí)封裝路線,滿足FOPLP/TGV應(yīng)用于下一代AI需求

先進(jìn)封裝中RDL工藝介紹

芯片設(shè)計(jì)中再分布層(RDL)技術(shù)的優(yōu)勢(shì)

芯片設(shè)計(jì)中再分布層(RDL)技術(shù)的優(yōu)勢(shì)

評(píng)論