buffer和cache的區別

緩沖區(Buffer)和緩存(Cache)是計算機系統中用于提高數據讀寫效率的兩個關鍵概念,它們雖然功能有所重疊,但在實際應用中存在一些差異。在下文中,將詳盡、詳實、細致地介紹緩沖區和緩存的區別。

一、定義和功能:

1. 緩沖區(Buffer):

緩沖區是計算機內存中的一塊區域,用于臨時存儲數據。它在數據傳輸過程中起到緩沖的作用,可以暫時保存一部分數據,等待處理或傳輸。緩沖區通常與I/O操作、數據傳輸或進程間通信等密切相關。它能夠優化數據讀寫效率,減少等待時間,提高整體系統性能。

2. 緩存(Cache):

緩存是計算機系統中的一種高速存儲器,用于臨時存儲經常訪問的數據以提升數據讀取速度。緩存常位于CPU和主存之間,通過存儲部分數據塊的副本,加快對數據的訪問。緩存利用了局部性原理,即數據訪問往往呈現出時間和空間上的局部集中性。通過緩存,可以減少CPU等待主存的時間,從而提高系統的整體性能。

二、位置和結構:

1. 緩沖區(Buffer):

緩沖區位于計算機內存中,通常由操作系統分配,用于臨時存儲數據。緩沖區可以是單個字節、數組或隊列等數據結構,其大小取決于應用程序需求和系統資源。

2. 緩存(Cache):

緩存分為多級,通常包括L1、L2和L3等層級。L1緩存位于CPU內部,速度最快,容量最小;L2緩存通常位于CPU和主存之間,速度較快,容量較大;L3緩存位于CPU和主存之間,速度較慢,容量最大。緩存的結構通常為按組劃分的矩陣結構,其大小和組織方式由處理器架構和芯片設計決定。

三、數據存儲:

1. 緩沖區(Buffer):

緩沖區存儲的數據通常是臨時的、即時的,一旦使用完畢就會被釋放或移出內存。緩沖區中的數據不會被重復讀取或存儲,其主要目的是提供臨時存儲空間,保證數據的連續流動。

2. 緩存(Cache):

緩存存儲的數據是根據局部性原理選取的熱數據,這些數據經常被訪問且可能被反復讀取。緩存的目的是將這些經常使用的數據保存在更接近處理器的位置,以加快數據訪問速度。緩存具有自動更新機制,當新數據被讀取時,會自動更新緩存中的內容。

四、數據一致性:

1. 緩沖區(Buffer):

緩沖區不關心數據的一致性,只提供了臨時的存儲空間。緩沖區不會自動更新數據,需要程序明確指定何時寫入或讀取數據。

2. 緩存(Cache):

緩存需要考慮數據的一致性,即緩存中的數據應與主存中的數據保持一致。為了維護數據的一致性,緩存采用了一系列的技術,如寫回(Write Back)和寫直達(Write Through)策略,保證數據的正確性和一致性。

五、應用場景:

1. 緩沖區(Buffer):

緩沖區廣泛應用于各種數據傳輸、讀寫操作,如文件讀寫、網絡通信、圖像/音頻/視頻處理等。緩沖區的主要作用是減少等待時間,提高數據處理速度,使得數據在不同環節之間流暢傳輸。

2. 緩存(Cache):

緩存主要應用于計算機體系結構中,用于加速指令和數據的讀取。緩存被廣泛應用于處理器、操作系統、數據庫系統等各個層面的計算機系統中,通過存儲常用數據的副本,降低了訪問主存的頻率和時間。緩存的作用是提高計算機系統的整體性能,減少對慢速存儲介質的訪問。

綜上所述,緩沖區(Buffer)和緩存(Cache)在定義、功能、位置、數據存儲、數據一致性和應用場景等方面存在一定的差異。雖然二者的功能有所重疊,但緩沖區更側重于臨時存儲,提高數據讀寫效率;而緩存更側重于提升數據訪問速度,遵循局部性原理。在實際應用中,根據具體需求和系統特點,我們可以靈活地使用緩沖區和緩存,以實現最佳的性能優化效果。

-

存儲器

+關注

關注

38文章

7528瀏覽量

164345 -

Cache

+關注

關注

0文章

129瀏覽量

28433

發布評論請先 登錄

相關推薦

什么是緩存(Cache)及其作用

請問PurePath里面帶ROM和不帶ROM的元件有什么區別呢?

Cache和內存有什么區別

寄存器和高速緩存有什么區別

高速緩沖存儲器與內存的區別

MSPM0 UART通信中DMA和Ring Buffer環形緩沖的應用

解析Arm Neoverse N2 PMU事件L2D_CACHE_WR

請教論壇大神Labview調用BlueSuite TestEngine.dll問題

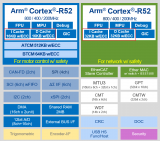

Cortex R52內核Cache的具體操作(2)

Cortex R52內核Cache的相關概念(1)

CortexR52內核Cache的具體操作

buffer和cache的區別

buffer和cache的區別

評論