近日,備受關注的 Arm TechSymposia 技術大會在上海圓滿閉幕。在這次盛會中,作為國內首家數字 EDA 供應商的思爾芯成為焦點,其在臺北、東京、深圳、北京和上海的巡回展出吸引了業界的廣泛關注,為 Arm 外置支持方案提供了更高效的解決方案。

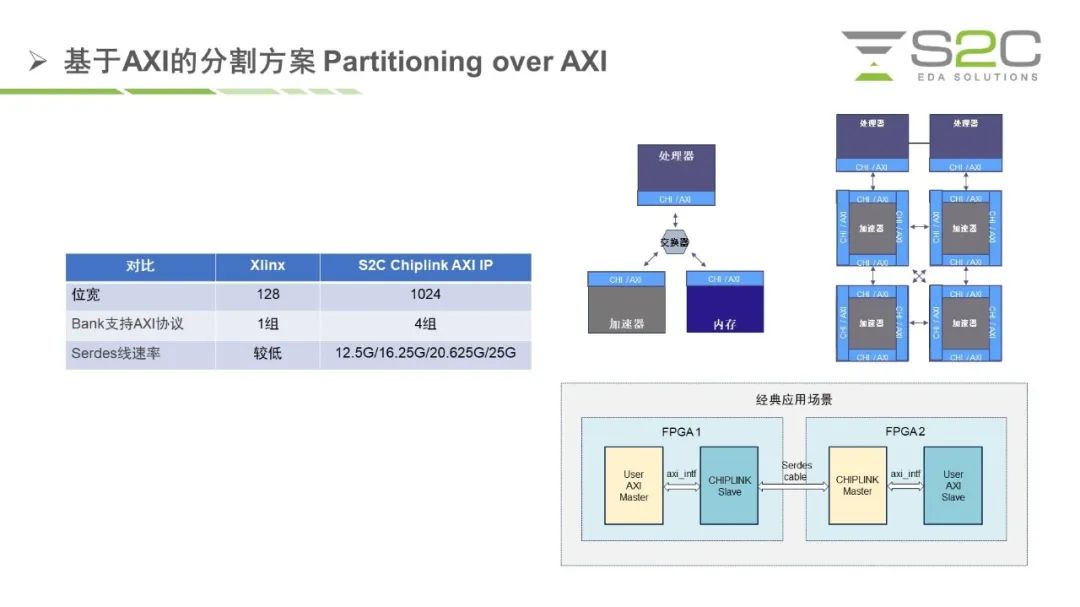

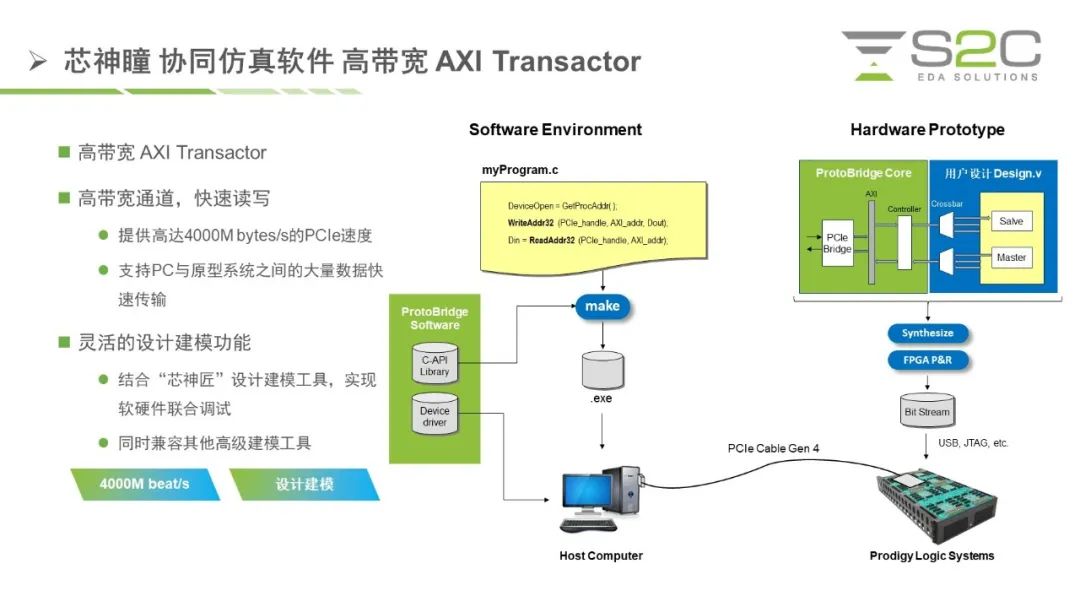

在 Arm 的外置支持方案中,通過 Thunder-bus IP 實現 Zynq UltraScale+ MPSoC 與原型驗證系統之間的 AXI 接口通信。然而,思爾芯的 Chiplink AXI IP 方案在這方面取得了更顯著的突破。在多核 Arm 驗證方案中,思爾芯采用了低延遲的 AXI Chip to Chip IP,實現了基于 AXI 接口的多核 Arm 間高效通信。其 Chiplink AXI IP 方案支持高達 1024 位寬的 AXI DATA 位寬,并能夠在每個 Bank 支持最多 4 組 AXI 協議,同時提供多種可配置的 Serdes 線速率(12.5G、16.25G、20.625G、25G),使得多核 Arm 之間的通信速度能夠達到 100MHz。有參觀者表示:“這個 Chiplink AXI IP 方案真是令人印象深刻,對于我們未來的項目將非常關鍵。” 此外,思爾芯還展示了芯神瞳協同仿真軟件 ProtoBridge,它提供了一個高帶寬的 AXI Transactor。提供高達 4000M bytes/s 的 PCIe 速度,實現快速讀寫。這個 Transactor 利用了業界廣泛采用的 AXI-4 總線協議和獨有的專利技術*(* 專利號:ZL201911239764.5),實現了 PC 軟件到原型驗證環境的無縫連接。它創建了一個高吞吐量的數據通道,允許在 FPGA 和 PC 主機之間進行大量的事務級數據交互。它還可以兼容其他高級建模工具例如思爾芯的“芯神匠”架構設計軟件,實現軟硬件聯合調試。

此外,思爾芯還展示了芯神瞳協同仿真軟件 ProtoBridge,它提供了一個高帶寬的 AXI Transactor。提供高達 4000M bytes/s 的 PCIe 速度,實現快速讀寫。這個 Transactor 利用了業界廣泛采用的 AXI-4 總線協議和獨有的專利技術*(* 專利號:ZL201911239764.5),實現了 PC 軟件到原型驗證環境的無縫連接。它創建了一個高吞吐量的數據通道,允許在 FPGA 和 PC 主機之間進行大量的事務級數據交互。它還可以兼容其他高級建模工具例如思爾芯的“芯神匠”架構設計軟件,實現軟硬件聯合調試。 在下午的技術分論壇上,思爾芯作為 Arm 生態伙伴之一,受邀發布一場重要的技術演講。思爾芯產品經理秦英明就公司自主研發的芯神鼎硬件仿真系統進行了深入講解。該系統已在基于 Arm 架構的芯片系統級驗證中取得廣泛應用。其提供的多種加速仿真模式,如電路內仿真(In-CircuitEmulator)、事務級仿真(Transaction Based Acceleration)和混合仿真(Hybrid Emulation)等,展示了思爾芯在 EDA 技術領域的深厚實力。特別是混合仿真模式,通過 Qemu 平臺實現真實的 Arm 內核系統模擬,結合 TLM 模型和 SCEMI 協議,構建了一個完整的 Arm 內核+外設混合仿真環境。

在下午的技術分論壇上,思爾芯作為 Arm 生態伙伴之一,受邀發布一場重要的技術演講。思爾芯產品經理秦英明就公司自主研發的芯神鼎硬件仿真系統進行了深入講解。該系統已在基于 Arm 架構的芯片系統級驗證中取得廣泛應用。其提供的多種加速仿真模式,如電路內仿真(In-CircuitEmulator)、事務級仿真(Transaction Based Acceleration)和混合仿真(Hybrid Emulation)等,展示了思爾芯在 EDA 技術領域的深厚實力。特別是混合仿真模式,通過 Qemu 平臺實現真實的 Arm 內核系統模擬,結合 TLM 模型和 SCEMI 協議,構建了一個完整的 Arm 內核+外設混合仿真環境。

在大會中,Arm 的高級副總裁 Mohamed Awad 強調了公司致力于打造完整且全面的解決方案,旨在加快合作伙伴產品上市的速度。這一戰略使合作伙伴能夠更專注于創新解決方案的開發,推出更多新產品和服務,以實現市場差異化。

作為 Arm 生態的合作伙伴,思爾芯在此次技術大會上的表現是這一戰略的完美體現。公司展示的創新技術和解決方案,不僅展現了其對市場需求和未來趨勢的深刻理解,也彰顯了其在推動行業發展和技術創新方面的重要作用。思爾芯的貢獻不僅加強了與 Arm 的合作關系,也為整個技術生態系統帶來了新的活力和可能性。

-

ARM

+關注

關注

134文章

9167瀏覽量

369212 -

eda

+關注

關注

71文章

2788瀏覽量

173866 -

思爾芯

+關注

關注

0文章

123瀏覽量

1317

發布評論請先 登錄

相關推薦

LoRaWAN網絡在智慧水務中的創新解決方案

“2025 IC風云榜”揭曉,思爾芯獲“年度最佳解決方案獎”

銳成芯微亮相Arm Tech Symposia年度技術大會

2024 Arm Tech Symposia圓滿落幕,思爾芯創新方案備受矚目

Arm為用戶帶來卓越的 AI 體驗

Arm成功將Arm KleidiAI軟件庫集成到騰訊自研的Angel 機器學習框架

面向未來的智能視覺參考設計與汽車架構,思爾芯提供基于Arm技術的創新方案

思爾芯亮相IIC Shenzhen,創新解決方案賦能RISC-V芯片設計

Arm邀您相約2024全球CEO峰會

Arm Tech Symposia年度技術大會即將來襲

思爾芯亮相芯和半導體大會,以數字前端EDA解決方案應對設計新挑戰

梯度科技入選2023年信息技術應用創新解決方案名單

思爾芯受邀參加CCF Chip 2024大會

兆芯金融方案入選工信部2023年信息技術應用創新典型解決方案

Wi-Fi 7射頻IP驗證系統發布!思爾芯EDA助力Sirius Wireless加速芯片設計

思爾芯在Arm Tech Symposia大會上展現基于 Arm 的 Chiplink AXI IP 創新解決方案

思爾芯在Arm Tech Symposia大會上展現基于 Arm 的 Chiplink AXI IP 創新解決方案

評論