隨著背面供電技術(shù)的完善和新型2D通道材料的采用,英特爾正致力于繼續(xù)推進(jìn)摩爾定律,在2030年前實(shí)現(xiàn)在單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管。

包括PowerVia背面供電技術(shù)、用于先進(jìn)封裝的玻璃基板和Foveros Direct技術(shù)預(yù)計(jì)將在2030年前投產(chǎn)。

12月9日,英特爾在IEDM 2023(2023 IEEE 國(guó)際電子器件會(huì)議)上展示了使用背面電源觸點(diǎn)將晶體管縮小到1納米及以上范圍的關(guān)鍵技術(shù)。英特爾表示將在2030年前實(shí)現(xiàn)在單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管。

PowerVia背面供電技術(shù)預(yù)計(jì)將于2024年隨Intel 20A制程節(jié)點(diǎn)推出。

英特爾表示,其將繼續(xù)推進(jìn)摩爾定律的研究進(jìn)展,包括背面供電和直接背面觸點(diǎn)(direct backside contacts)的3D堆疊CMOS晶體管,背面供電研發(fā)突破的擴(kuò)展路徑(如背面觸點(diǎn)),并在同一塊300毫米晶圓上(而非封裝)中實(shí)現(xiàn)硅晶體管與氮化鎵(GaN)晶體管的大規(guī)模單片3D集成。

隨著遵循摩爾定律的半導(dǎo)體技術(shù)不斷推進(jìn),半導(dǎo)體芯片的集成度越來越高,目前衡量芯片的微觀集成密度的單位也從納米轉(zhuǎn)向埃米(1埃米等于一百億分之一米,是納米的十分之一)。

“我們正在進(jìn)入制程技術(shù)的埃米時(shí)代,展望‘四年五個(gè)制程節(jié)點(diǎn)’計(jì)劃實(shí)現(xiàn)后的未來,持續(xù)創(chuàng)新比以往任何時(shí)候都更加重要。”英特爾公司高級(jí)副總裁兼組件研究總經(jīng)理桑杰·納塔拉詹(Sanjay Natarajan)表示,“英特爾展示了繼續(xù)推進(jìn)摩爾定律的研究進(jìn)展,這顯示了我們有能力面向下一代移動(dòng)計(jì)算需求,開發(fā)實(shí)現(xiàn)晶體管進(jìn)一步微縮和高能效比供電的前沿技術(shù)。”

據(jù)國(guó)際數(shù)據(jù)公司(IDC)預(yù)計(jì),全球人工智能硬件市場(chǎng)(服務(wù)器)規(guī)模將從2022年的195億美元增長(zhǎng)到2026年的347億美元,五年復(fù)合增長(zhǎng)率達(dá)17.3%。其中,用于運(yùn)行生成式人工智能的服務(wù)器市場(chǎng)規(guī)模在整體人工智能服務(wù)器市場(chǎng)的占比將從2023年的11.9%增長(zhǎng)至2026年的31.7%。

據(jù)英特爾透露,包括PowerVia背面供電技術(shù)、用于先進(jìn)封裝的玻璃基板和Foveros Direct技術(shù)預(yù)計(jì)將在2030年前投產(chǎn)。

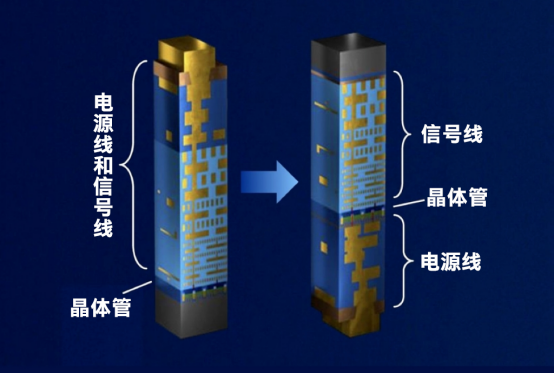

英特爾技術(shù)發(fā)展總監(jiān)毛羅·科布林斯基(Mauro Kobrinsky)表示:“摩爾定律推動(dòng)著更多晶體管的集成,這又推動(dòng)著更多的層次和更小的導(dǎo)線,增加了復(fù)雜性和成本。每一層次都必須提供信號(hào)和電源導(dǎo)線,這通常會(huì)導(dǎo)致優(yōu)化妥協(xié)和資源爭(zhēng)奪,形成互聯(lián)瓶頸,事情變得越來越具有挑戰(zhàn)性。”“背面電源從根本上改變了這種情況,通過在器件的兩側(cè)和垂直互連中使用電源過孔。我們明年將能夠在半導(dǎo)體Intel 20A(2nm)和18A(1.8nm)中部署這項(xiàng)技術(shù),這意味著在前面減少導(dǎo)線,因此我們可以放寬間距,不再需要進(jìn)行優(yōu)化妥協(xié)。”

“在電源過孔之外,我們的研究還涉及背面接觸,這使我們首次能夠連接器件兩側(cè)的晶體管。我們已經(jīng)能夠在研究中制造這些接觸,并且前后接觸無需使用電源過孔進(jìn)行布線。這使我們能夠減小電池的電容,提高性能并降低功耗。”科布林斯基說。

英特爾認(rèn)為,晶體管微縮和背面供電是滿足世界對(duì)更強(qiáng)大算力指數(shù)級(jí)增長(zhǎng)需求的關(guān)鍵。隨著背面供電技術(shù)的完善和新型2D通道材料的采用,英特爾致力于繼續(xù)推進(jìn)摩爾定律,在2030年前實(shí)現(xiàn)在單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管。

審核編輯:黃飛

-

英特爾

+關(guān)注

關(guān)注

61文章

10009瀏覽量

172344 -

摩爾定律

+關(guān)注

關(guān)注

4文章

636瀏覽量

79235 -

晶體管

+關(guān)注

關(guān)注

77文章

9746瀏覽量

138917 -

人工智能

+關(guān)注

關(guān)注

1796文章

47683瀏覽量

240313

原文標(biāo)題:英特爾:2030年前實(shí)現(xiàn)在單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管

文章出處:【微信號(hào):現(xiàn)代電子技術(shù),微信公眾號(hào):現(xiàn)代電子技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

英特爾IEDM 2024大曬封裝、晶體管、互連等領(lǐng)域技術(shù)突破

英特爾展示互連微縮技術(shù)突破性進(jìn)展

英特爾宣布擴(kuò)容成都封裝測(cè)試基地

英特爾擴(kuò)容在成都的封裝測(cè)試基地

技術(shù)前沿:“環(huán)抱”晶體管與“三明治”布線

英特爾是如何實(shí)現(xiàn)玻璃基板的?

英特爾計(jì)劃最快2026年量產(chǎn)玻璃基板

英特爾OCI芯粒在新興AI基礎(chǔ)設(shè)施中實(shí)現(xiàn)光學(xué)I/O(輸入/輸出)共封裝

英特爾實(shí)現(xiàn)光學(xué)IO芯粒的完全集成

英特爾引領(lǐng)未來封裝革命:玻璃基板預(yù)計(jì)2026年實(shí)現(xiàn)量產(chǎn)

英特爾逐步停止Ponte Vecchio GPU生產(chǎn),專注于Gaudi 2/3產(chǎn)品

Ansys多物理場(chǎng)簽核解決方案獲得英特爾代工認(rèn)證

英特爾首推面向AI時(shí)代的系統(tǒng)級(jí)代工

英特爾:2030年前實(shí)現(xiàn)單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管

英特爾:2030年前實(shí)現(xiàn)單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管

評(píng)論