今年3月24日,94歲的戈登·摩爾在夏威夷家中與世長辭——這恰似一個時代的隱喻:“摩爾定律”是否也正在和摩爾先生一起離我們遠去?

毋庸置疑的是,與“摩爾定律”緊密相關單芯片晶體管數量和工藝幾何尺寸演進正在迎來一個“奇點時刻”。與此同時,終端應用的高算力需求依然在不斷推高單芯片Die尺寸,在光罩墻的物理性制約之下,眾多芯片設計廠商在芯片工藝與良率的流片成本以及嚴苛的上市時間的平衡度上正在遭遇越來越嚴峻的挑戰。

幾十年來,半導體產業的發展史一直遵循著“奧卡姆剃刀”哲學理念,從設計到制造的整個流程都需要避免“重復造輪子”的無用功。業界呼喚重復設計再利用以提高芯片研發效率,剔除無效的設計成本冗余,催生了IP模塊的興起。當下,面對摩爾定律趨近極限的施壓,3DIC Chiplet先進封裝異構系統集成越來越成為產業界討論的焦點。這種創新的系統不僅在Chiplet的設計、封裝、制造、應用等方面帶來了許多突破,也為一眾高速Chiplet接口IP供應商打開了一扇窗。一時間Chiplet技術被廣泛視為延續摩爾定律生命力之有求必應的“阿拉丁神燈”。芯耀輝科技有限公司(以下簡稱“芯耀輝”)即是該“神燈”的“燃燈者”之一,為接口IP的關鍵作用提供了有力的支持。

作為國內少數擁有完整D2D和C2C IP解決方案的供應商,經過近三年時間的不懈努力,已在國內率先完成了多個行業最高標準的接口IP自主研發,并獲得頭部客戶的采用。

善戰者求之于勢,勢隨人為。芯耀輝的發展之路是多維度和立體的,無論是在“自上而下”的頂層設計,即接口標準制定的參與上,還是在“自下而上”的技術落地實踐,應對接口IP各種嚴酷挑戰的前沿探索上,始終保持著高度的專業性,在產品的可靠性方面全心致力于為客戶提供最佳技術支持。

一流企業做標準

芯耀輝不斷推動國內CCITA標準產業化

Chiplet的原理是把芯片切分成不同的小芯片并加以互聯。理想狀態下,多顆芯粒之間的互聯效率需要和單顆芯片內部的互連效率不相上下,這就需要將芯片內部總線的互聯系統“移植”拷貝到片間互聯,于是,片間接口可謂重任在肩。對片間高速互聯嚴苛標準和龐大需求,刺激著接口IP市場的火爆發展。曾接受過“集微訪談”專訪,年度“Design IP Report”權威榜單主筆人Eric Esteve向業內展示的最新數據顯示,過去5年間接口IP在眾多IP類別的市場占比從18%增長到了25%,去年USB、PCIe、DDR等前五大接口類別的市場營收為14.4億美元,未來五年將會有翻倍的增長。Esteve還向愛集微透露:“我們對未來高速IP接口的市場預測很有信心,誤差率從未大過5%。”

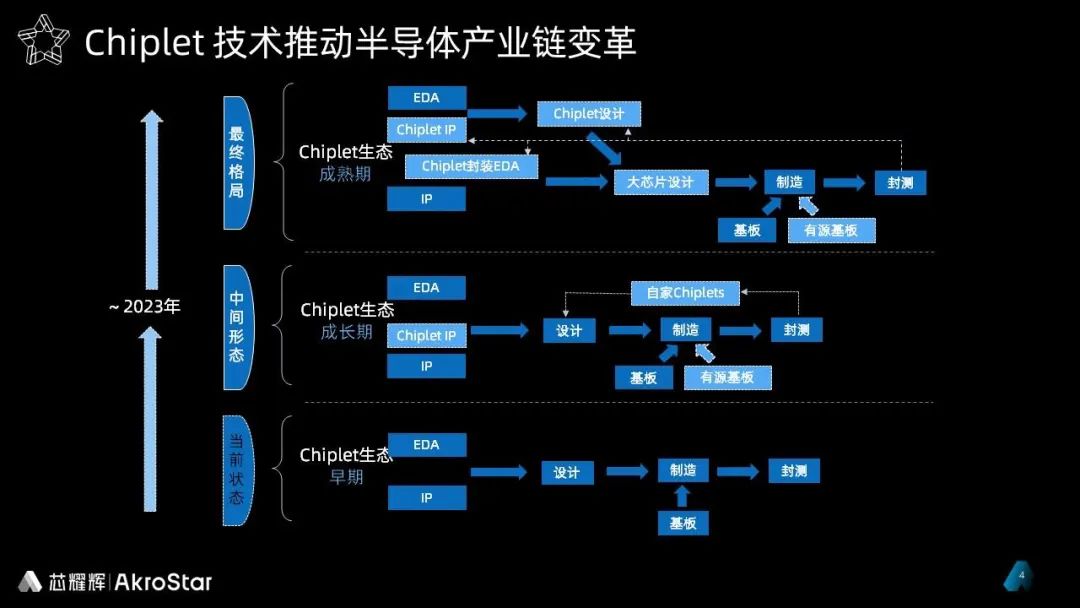

群雄逐鹿,技高者得之。雖然行業對Chiplet技術在芯片領域協同生態的討論有著十幾年的嚴肅討論,但真正商用落地的歷史并不長,芯耀輝董事長曾克強曾做出判斷,Chiplet技術推動產業鏈的整體變革需要經過早期、成長期和成熟期三個階段。

早期階段即芯片分拆和與之對應的先進封裝定義協議的“散裝化”階段,統一的標準亟待理清和確定;成長期則是Chiplet芯片部分單元在工藝上進行迭代并尋找最優解的階段,這時,工藝和互聯標準也在快速逐步成型和統一;曾克強預計,到2027年左右Chiplet生態才會真正進入“IP硬化時代”,彼時會誕生一批針對Chiplet技術應運而生的Fabless公司,有源基板供應商、支持集成Chiplet的EDA公司等等,圍繞Chiplet產業的IP生態圈將會更加立體和豐滿,相關上下游供應商的協同性也會更加系統化。

近年來,國際上的主流Chiplet D2D協議標準逐漸收斂集中為XSR、BOW、OpenHBI、UCIe等四種。如果我們以帶寬密度、能效比、走線間距、延遲和誤碼率這五大維度綜合評定這幾種標準的優劣,就會發現UCIe以較好的帶寬、能效和延遲組合,在產業界的接受度方面逐漸勝出,它可以定義邏輯 PHY、訓練機制、初始化序列、邊帶和鏈路控制,并且可以重用和繼承成熟的UCIe和CXL生態系統,得到了眾多設計公司、晶圓廠和封裝廠的推崇和支持。

但UCIe對IP實現和封裝工藝有更高的要求,并且由于一些客觀原因,如中外工藝代差和國際大廠標準割裂等,亟需標準本土化的落地。因此,適合國內產業鏈及需求的互聯標準CCITA標準應時而生——2022年10月,芯耀輝承接國家科技部重點研發專項,作為國家隊成員著力推動國內Chiplet標準CCITA產業化。該標準定義了并口和串口,與UCIe保持兼容,同時在封裝環節上,CCITA的Chiplet標準也主要采用國內可實現的技術,充分考慮了國內現實應用以及實際的封裝生產能力。

UCIe的國際主流化和本土化CCITA標準的應勢而行,此過程讓國內頭部接口IP廠商意識到國內環境和生態制訂自有標準的重要性。純粹的技術標準只是懸空的樓閣,還需要技術與商業模式的緊密結合才能探索出一條商用落地的可行之路,芯耀輝憑借在接口IP相關技術領域的深厚積累,在深度參與制訂CCITA協議的同時,也在同步開發相關產品。

芯耀輝的武器庫

從容應對高速Chiplet接口IP諸多挑戰

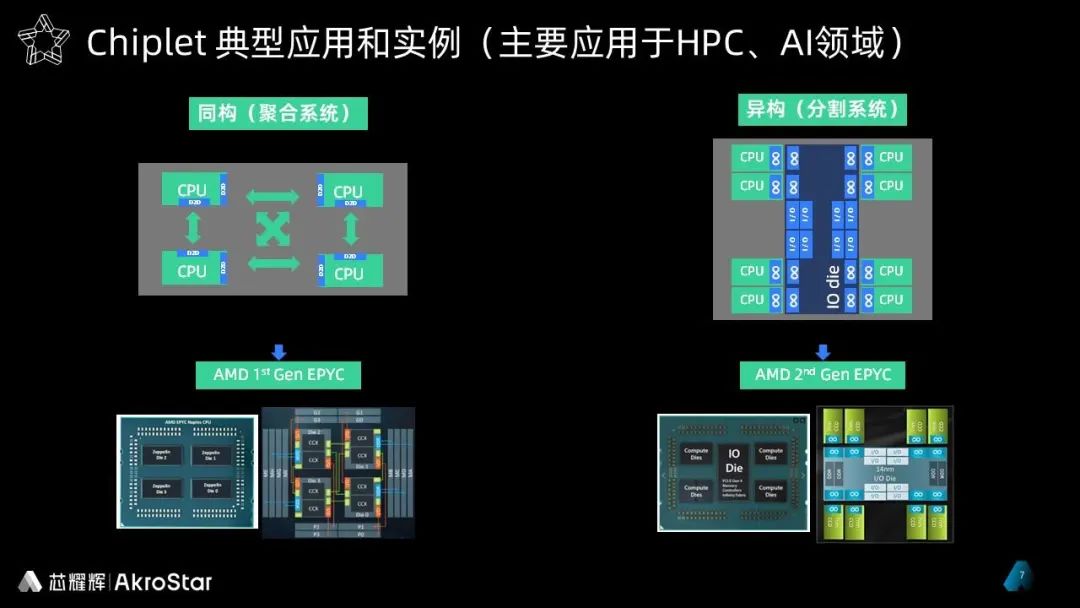

如前所述,傳統單片集成的SoC因其統一制程之故,芯片上不同的功能模塊需要同步進行迭代,導致芯片開發時間長且缺陷數量多。Chiplet技術可以實現功能切分,將制程差異化且部分單元工藝做選擇性迭代,可以加速產品的上市周期,減少重新流片和封裝的次數,進而降低了芯片企業資金投入成本和研制風險。換言之,Chiplet可以對芯片上部分單元在工藝上進行最優迭代,針對不同功能選擇最合適的工藝制程,在這種范導性技術路線的指引下,延伸出了同構(聚合系統)和異構(分割系統)兩種商用實地用例。

“同構”通過高速接口IP的實現和先進封裝,以相同的Die設計實現計算能力的擴展,適用于CPU、TPU、AI SoC等低延遲和低誤碼率的應用場景;而“異構”則是將芯片的功能做差異化的拆分,做到“異”和“構”的有機結合——負責高算力和性能的先進工藝的Die和負責特色功能的成熟制程的Die被封裝在一起。這兩種最典型的實用案例可以通過AMD服務器CPU Epyc系列具體而微地得到展現。

第一代AMD EYPC利用同構的方法聚合了4個設計原理相同的Die,4個Die均采用了7nm制程,通過多個Die的互聯構建了可擴展系統,在降低單一芯片的復雜性的同時提高了計算能力和制造成功率;而在第二代EYPC將芯片功能拆分為CCD運算Die(Compute Core Die)和IO Die,前者負責高性能計算,后者負責特定功能,實現了不同先進、成熟工藝芯片的巧妙融合。

高速接口和先進封裝雙軌并驅,一顆大芯片通過同構或者異構的方法論融合了多個Die,實現了算力的擴展,也對接口的可移植性、標準化、兼容性,以及低延時和低誤碼率提出了更高的要求。以AMD和聯發科為代表的Chiplet技術先鋒派,勢必會帶動高速接口IP供應商和封測廠的進一步協同發展。

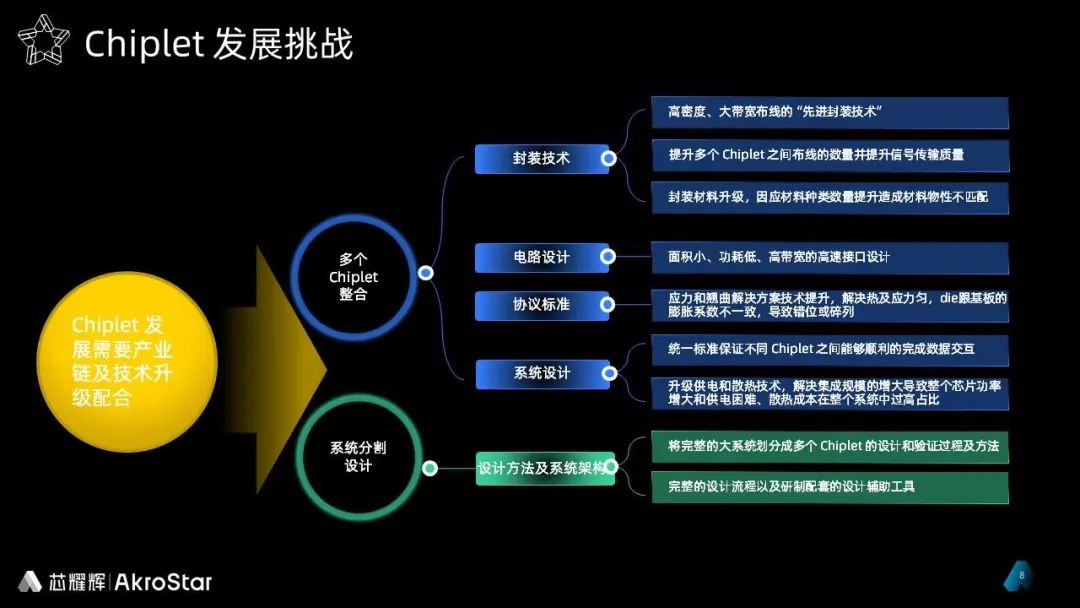

雖然說Chiplet技術已成為半導體產業在摩爾定律逐漸減緩下的共識性選擇,但時至今日,它依然面臨著諸多挑戰。以芯耀輝為代表的高速IP接口供應商認識到,Chiplet并非一個獨立的技術點,而是一個復雜的綜合技術體系,需要整個產業鏈各方面的共同努力,這項技術的持續推進有賴于整個產業鏈的協同發展。

芯耀輝董事長曾克強在采訪時表示,Chiplet發展的挑戰,可以歸納為微電子層面上的純技術挑戰,以及生態系統的挑戰兩個維度。首先,Chiplet本身整合要求高密度、大帶寬布線的先進封裝技術,其中涉及到多個Chiplet之間的布線數量和封裝材料升級,會造成材料數量種類提升造成的物料不匹配問題等等,純技術挑戰還包括了片間的D2D傳輸,要求面積小,功耗低高帶寬的高速接口設計,同時業界也需要建立一個標準化的規范以解決不同芯片之間的通信困難問題等等。

第二個大的挑戰和設計方法及系統架構硬相關,Chiplet所帶來的系統分割設計,所對應的是將完整的大系統劃分為多個Chiplet的設計驗證過程和方法,這需要與EDA工具的協同工作,同時也需要完整的設計方法學,以確保拆分的有效性。

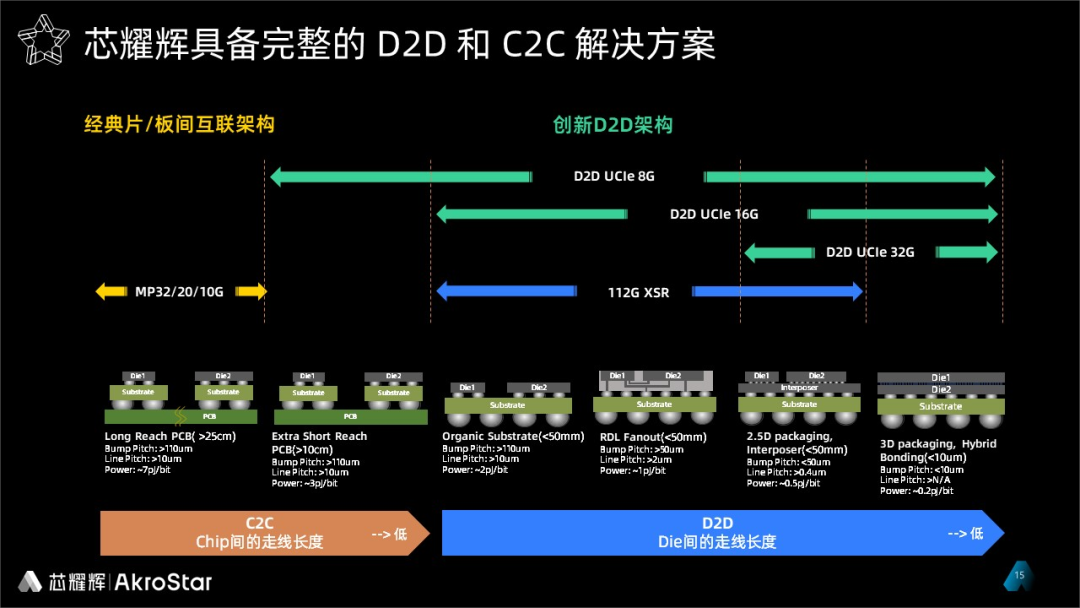

哲人有諺:密涅瓦的貓頭鷹只有在黃昏后才會起飛。產業競爭并不總是一個從基礎研究向產業化順序展開的進程,強大的下游產業化能力,往往也會反向影響基礎技術路線的走向。多種技術因素讓客戶有了在權衡D2D和C2C技術路線時會有具象化的參照系,如芯片系統性能需求(如延遲、能耗、總帶寬等)、芯片物理實現限制(如芯片面寬、bump pitch)以及封裝選擇和設計限制(如封裝層數、封裝厚度、線寬線距等)。

芯耀輝作為國內領先的先進接口IP供應商,具備完整的D2D(Die to Die)和C2C(Chip to Chip)解決方案。在Chiplet技術框架下,芯耀輝提供了能夠滿足不同封裝、互連和應用需求的多維度,全方位的解決方案,不斷滿足客戶對最佳性能和靈活性的需求,具體到Chiplet D2D解決方案,無論是長距離的互連、超短距離的高速通信,還是不同封裝層次的需求,芯耀輝均可精準匹配用戶應用場景。

在中長距離互聯方面,芯耀輝可提供針對長距離的PCB和芯片之間、芯片與芯片之間的互連而設計的“long range”解決方案,在超短距離高速互連方面,芯耀輝的112G的XSR(Chiplet間超短距離互連)解決方案可獨當一面,它在芯片與芯片之間的緊密互連中有著出色的表現。尤其值得一提的是,芯耀輝的D2D UCIe產品已經實現了迭代,從UCIe 8G演進到了UCIe 16G,能夠在各種先進封裝中展現出色的性能,它支持RISC-V MCU Based Firmware training架構,可獨立完成PHY的初始化、參數協商和training以及ATE測試,支持周期性的PVT補償及校準機制,同時該解決方案還具有優化的通道面寬架構,可以適配多種封裝形式和高密度Die間走線。

并非單點突破

芯耀輝在高速接口IP領域的全局性視角

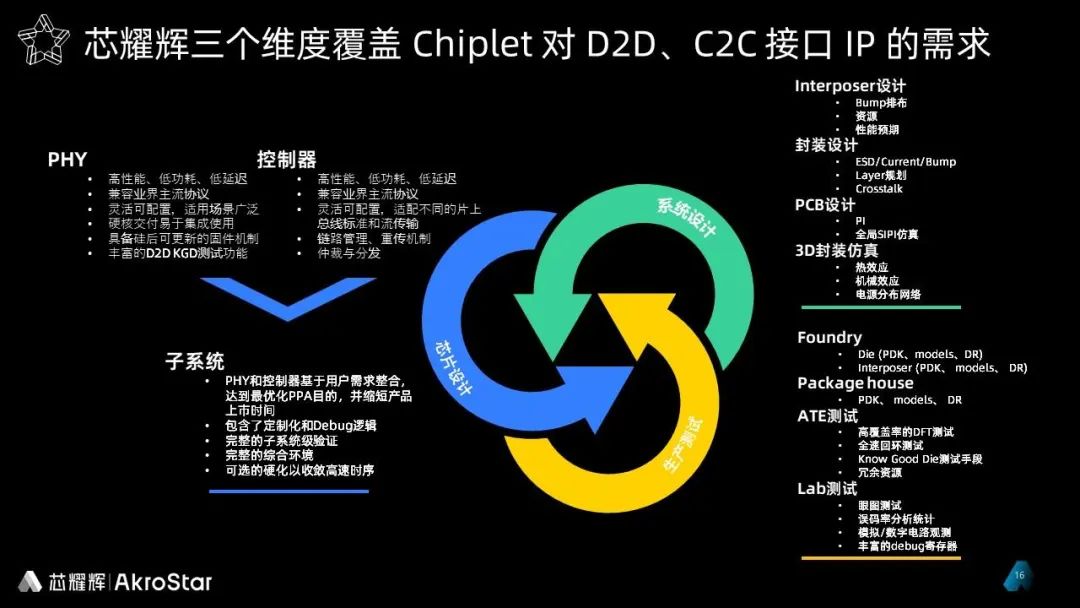

從技術、市場、用戶、創新等諸多復雜的要素中,我們可以一窺芯耀輝對Chiplet接口IP研發哲學的整體性方法論和多維立體性視角。具體來講,這種視角可以從芯片設計、系統設計和生產測試三個維度加以表達。

打造一系列有競爭力的Chiplet 接口IP解決方案,必須把Chiplet技術理解為一個完整的系統設計。芯耀輝除了PHY IP外,解決方案還包括PHY、控制器和將PHY及控制器集成在一起的子系統。同時,芯耀輝還提供Interposer設計、封裝設計、PCB設計和3D封裝仿真等技術支持,以及完整的測試方案,多方位支撐客戶Chiplet產品的高效運行,實現高性能、低功耗、低延遲,幫助不同的客戶都能得到適合自己的最佳PPA的需求。

為了加快客戶芯片上市時間和一次流片成功率,芯耀輝并沒有將Chiplet技術挑戰性推向系統設計和生產測試以適應IP,而是“逆流而上”,在IP設計的源頭就來解決這些挑戰。我們可以從企業應對Chiplet D2D先進封裝時如何保證信號完整性、電源完整性的應對之策,以及KGD測試環節中以點帶面地理解芯耀輝對IP技術knowhow的掌握度。

D2D封裝對信號完整性的要求更為緊迫,此過程中為了連接各個芯片單元,不得不通過眾多Via來穿越深層封裝的線路,帶來了較為嚴重的信號crosstalk(串擾)問題,從而可能導致數據的失真和錯誤。芯耀輝建立了發射器、接收器、通道綜合模型,模擬真實通道的頻率響應。這有助于更好地將頻率響應參數應用于Chiplet模型,有望為解決這一問題帶來重要價值;與信號完整性有著密切關聯的是電源的完整性,芯耀輝以on-die-cap(ODC)這一在高速接口設計中扮演關鍵角色的元件作為切入口,通過巧妙的電源鏈路設計和對ODC的優化運用,確保了對整個系統的穩定運行,為客戶提供了完整的支持和服務。

此外,為了保證客戶的時序收斂,芯耀輝的“硬核技術”還包括了對KGD(Know Good Die)測試的融合。先進封裝體系下多Die互聯,沒法像常規芯片一樣放探針來確定里面的Die是否正常工作或者D2D互聯是否出現短路,芯耀輝的PHY提供了豐富的D2D KGD測試功能,與ATE供應商實現了高質量共頻聯動,優化了芯片的流片成本,著重于客戶的一次性量產需求,加速了產品上市時間。

賦能產業數字化

芯耀輝ESG的多維展現

高端半導體IP和EDA工具是銜接集成電路設計、制造和封測的關鍵紐帶,同時也是數字產業化倒金字塔的“底座”,半導體IP產業以幾十億美元的全球產值撬動的是金字塔頂端數萬億級別的數字經濟。三年多以來,芯耀輝打造了一系列全面的國產先進工藝完成IP解決方案,在高性能計算、人工智能、5G、物聯網、消費電子等多個領域都能提供一站式接口IP解決方案,賦能各個領域SoC國產浪潮和數字化。尤其值得一提的是,自今年6月起,芯耀輝已連續獲得由SGS頒發的ISO 26262:2018 ASIL D車規級功能安全流程認證以及MIPI CDPHY TX、MIPI CDPHY RX和PCIe 3 PHY的功能安全產品認證證書,是國內唯一能夠提供符合車規認證標準的國產接口IP廠商,在助力車規級IP上車方面,芯耀輝的每一次突破都代表了國內該賽道的“鑿空之舉”。

自2020年6月芯耀輝成立以來,從產品研發、標準制定等等,每一次里程碑式的大事記,既是企業ESG的自身呈現,也是更宏觀視野下的國產半導體IP企業具體鮮活的微觀史。如前所述,芯耀輝判斷,在Chiplet生態發展的高級階段,IP供應商須面臨著重要的角色轉變——有潛力演變為Chiplet供應商,不但需具備高端芯片的設計能力,還要有多品類的IP布局和平臺化的運作能力。為了符合IP產業核心競爭力的內在要求,芯耀輝朝著這一方向布局未來不斷突破,這也是芯耀輝ESG秉承多維發展之路,作為Chiplet技術之“燃燈者”的題中之義。

審核編輯:劉清

-

單芯片

+關注

關注

3文章

422瀏覽量

34667 -

DDR

+關注

關注

11文章

715瀏覽量

65529 -

SoC芯片

+關注

關注

1文章

617瀏覽量

35042 -

chiplet

+關注

關注

6文章

434瀏覽量

12631 -

芯耀輝

+關注

關注

3文章

44瀏覽量

10001

原文標題:作為“燃燈者”的芯耀輝:推動國內高速Chiplet接口IP不斷破局

文章出處:【微信號:AkroStar-Tech,微信公眾號:芯耀輝科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

乾瞻科技UCIe IP設計定案,實現高速傳輸技術突破

乾瞻科技宣布最新UCIe IP設計定案,推動高速傳輸技術突破

芯耀輝:從傳統IP到IP2.0,AI時代國產IP機遇與挑戰齊飛

乾瞻科技發布車用高速接口IP系列,助力AI與自動駕駛

芯耀輝榮登2024半導體與集成電路最具商業潛力榜

芯耀輝榮登2024中國半導體與集成電路領域最具商業潛力榜

芯耀輝榮獲2025 IC風云榜“年度領軍企業獎”

芯耀輝一站式完整IP平臺解決方案如何助力AI芯片發展

芯耀輝榮獲“中國芯”優秀支撐服務IP企業

IMEC組建汽車Chiplet聯盟

芯耀輝推動國內高速Chiplet接口IP不斷破局

芯耀輝推動國內高速Chiplet接口IP不斷破局

評論