半導體對各行各業(yè)都有著潛移默化的影響,其重要性不言而喻。現(xiàn)如今半導體已徹底改變了我們的業(yè)務形態(tài),無論是汽車行業(yè),還是物聯(lián)網(wǎng)、通信和高性能計算等等。然而隨著對高性能和即時滿足需求的增加,SoC 的復雜性也相應提高。隨著數(shù)以百計的 IP 被集成到 SoC 中,漏洞變得越來越常見,修復也變得愈加困難。SoC 級的驗證過程所需的時間不斷增加,從而造成了流片計劃的延遲。伴隨著幾何尺寸的減少及門數(shù)的增加,要在有限的預算和規(guī)定時間內檢測漏洞變得越來越困難。

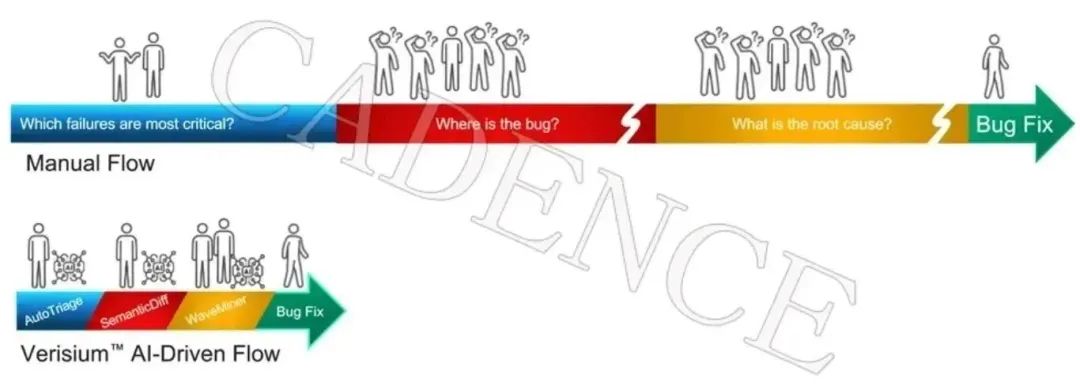

SoC 設計工程師往往需要花費超過 70% 的時間用于驗證,而檢測單個漏洞平均需要 16-20 個工程時。讓我們試想一下,一個設計中如果有 1000 個漏洞,那將造成多大的影響!

是時候采取行動,簡化 SoC 設計流程,節(jié)省寶貴的資源以確保項目及時完成了。只要通過實現(xiàn)自動化部署、新的工具和基于人工智能的方法就可以顯著提高生產力和驗證吞吐量。利用基于人工智能的方法,SoC 設計和驗證工程師可以更快地檢測錯誤,縮短驗證時間,并在多個引擎和運行中優(yōu)化性能。帶有人工智能的 EDA 工具更是可以幫助芯片制造公司更快、更高效地實現(xiàn)目標。SoC 設計和驗證中的人工智能不再是天方夜譚而是必需品,我們將通過它極大地提高產品質量,同時幫助減少開發(fā)時間和成本。

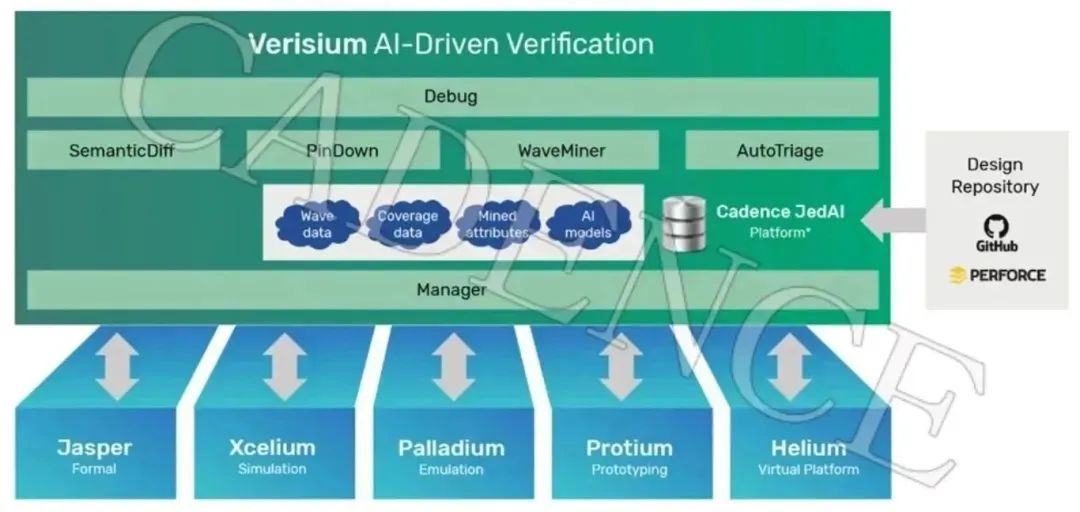

Cadence 正在通過使用 Verisium(人工智能驅動的驗證平臺)徹底改變芯片驗證。該平臺能利用大數(shù)據(jù)提高整體驗證吞吐量,特別是在調試方面。Verisium 建立在 Cadence Joint Enterprise Data and AI(JedAI)Platform 上,可以匯總包括波形覆蓋、源代碼、日志文件等在內的驗證數(shù)據(jù)。

Verisium platform 在日志文件、RTL 和測試平臺迭代、版本控制和波形上使用人工智能來加速和輔助調試,從而將手工工作量減少多達 32 倍。Verisium Debug platform 還提供了一種名為 VWDB 的新的波形格式,速度較以往的格式有極大幅度的提升。提高整體驗證吞吐量的關鍵是清楚所有數(shù)據(jù)的位置,進而對其進行利用、控制并管理。Verisium 可加快對設計錯誤根本原因的分析,提高覆蓋范圍,并優(yōu)化復雜 SoC 的驗證計算服務器資源。

Cadence 專注于持續(xù)創(chuàng)新,利用 Verisium AI-Driven Verification Platform(人工智能驅動的驗證平臺 Verisium)提供了一系列包括引擎、驗證 IP 和 Verisium 在內的工具。通過借助 Auto Triage、Semantic Diff、Pin Down 和 Wave Miner 等應用程序,Verisium 可以加速并協(xié)助調試,減少工程師在故障分類和調試上的時間。因此使用 Verisium 平臺的 SoC 調試可將生產力和整體驗證吞吐量提高 10 倍。

Verisium 如何提高

調試效率和驗證吞吐量?

Verisium Debug 工具是一款高級的調試工具,旨在幫助設計工程師、集成商和驗證工程師探索、分析和調試復雜的設計和測試平臺,而無需考慮它們的規(guī)模、語言或來源。該工具提供了幾種主要模式,如探索模式(仿真前)、后處理模式(仿真后)和交互模式(仿真中)。在這些模式中,用戶可以執(zhí)行如下各種任務:

●控制仿真器執(zhí)行步驟并執(zhí)行交互性調試

●記錄仿真結果后執(zhí)行后處理調試

●對 Palladium 仿真結果執(zhí)行調試并支持按需信號擴展

●調查仿真進入特定狀態(tài)的可能原因

●過濾測試環(huán)境的全部報文

●在 UPF 環(huán)境下調試功耗內容

Verisium Debug 工具的優(yōu)勢

使用 Verisium 對復雜設計和測試平臺調試比傳統(tǒng)工具更快、更高效。Verisium Debug 工具的部分主要優(yōu)勢包括:

1

可擴展性

2

可操縱性

3

SmartLog 有助于定位產生報文的層次目標,并向波形發(fā)送信息

4

驅動追蹤——很多 Verisium Debug 窗口中的直接訪問箭頭圖標允許您調用驅動追蹤

5

連接性分析顯示原始被追蹤信號和該信號驅動信號之間線路連接,并允許對追蹤路徑進行導航

6

根本原因分析(RCA)有助于診斷故障的根本原因

Verisium Manager 是一個真正卓越的工具,它為驗證規(guī)劃、故障分類、覆蓋收斂和回歸管理提供了一系列可靠的功能。它的特點在于具有能聯(lián)合企業(yè)數(shù)據(jù)和人工智能(JedAI)數(shù)據(jù)以及分析平臺的強大能力。這種集成方式將對驗證過程進行無以倫比的優(yōu)化,使其成為尋求簡化操作和最大限度提升生產力的芯片制造商的寶貴工具。憑借其集成的回歸管理功能,Verisium Manager 允許跨多個站點的覆蓋收斂,為不同規(guī)模的企業(yè)提供全面、可靠、有效且高效的解決方案。其強大的 API 集、企業(yè)級的可擴展性和性能,使其能夠無縫連接驗證流程中的所有引擎,包括模擬、形式化、仿真和原型平臺,為您提供全面的驗證解決方案,并可以通過定制和優(yōu)化實現(xiàn)最大的驗證吞吐量。

但真正使 Verisium Manager 如此與眾不同的原因在于它能夠應用 AI 和機器學習顯著提高調試和回歸吞吐量的生產力。通過直接與智能 Verisium Apps 集成,該工具可以幫助您在驗證過程中取得突破性成果,讓您在競爭中保持領先地位并實現(xiàn)業(yè)務目標。簡而言之,如果您希望驗證流程提升到一個新的水平,那么 Verisium Manager 就是您需要的終極驗證管理工具。

Verisium 應用

Verisium Platform 和相關應用程序在提高調試效率和提高驗證周期上發(fā)揮核心作用。這些應用包括:

VerisiumAutoTriage

對存在相同錯誤而導致失敗的測試進行自動分組。

Verisium SemanticDiff

通過識別故障原因來減少調試時間,并實現(xiàn)效率的顯著提高。

Verisium WaveMiner

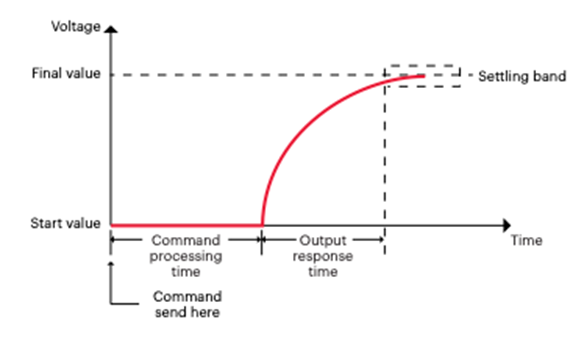

幫助驗證工程師在正確與錯誤測試中更方便地比較并找到錯誤點。波形格式完美適合現(xiàn)代驗證需求,并將仿真波形生成速度提高了 2 倍。

Verisum PinDown

在編輯工具上固定某個標簽,并分析仿真日志和代碼簽入之間的關系。

審核編輯:劉清

-

半導體

+關注

關注

334文章

27703瀏覽量

222617 -

EDA工具

+關注

關注

4文章

268瀏覽量

31935 -

soc

+關注

關注

38文章

4204瀏覽量

219083 -

人工智能

+關注

關注

1796文章

47666瀏覽量

240272 -

UPF

+關注

關注

0文章

50瀏覽量

13576

原文標題:利用人工智能優(yōu)化調試效率和驗證吞吐量

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何提高CYBT-243053-02吞吐量?

網(wǎng)卡吞吐量測試解決方案

如何利用NI LabVIEW技術提高測試系統(tǒng)的吞吐量?

如何提高VLD的吞吐量和執(zhí)行效率?

防火墻術語-吞吐量

如何提高無線傳感器網(wǎng)絡的吞吐量

如何提高系統(tǒng)設計容量和吞吐量

debug 吞吐量的辦法

debug 吞吐量的辦法

Cadence Verisium驗證平臺以AI助力瑞薩電子提高糾錯效率

如何顯著提高ATE電源吞吐量?

影響ATE電源系統(tǒng)吞吐量的關鍵因素

Verisium如何提高調試效率和驗證吞吐量呢?

Verisium如何提高調試效率和驗證吞吐量呢?

評論