讀出電路將紅外探測(cè)器二極管激發(fā)產(chǎn)生的光電子收集、積分成為電壓信號(hào)并按序讀出,使其變成后端系統(tǒng)可讀的電信號(hào),是紅外焦平面探測(cè)器的重要組成部分。電荷處理能力作為衡量讀出電路的一項(xiàng)重要指標(biāo),探測(cè)器的性能以及某些應(yīng)用條件下要求讀出電路具有大的電荷處理能力。

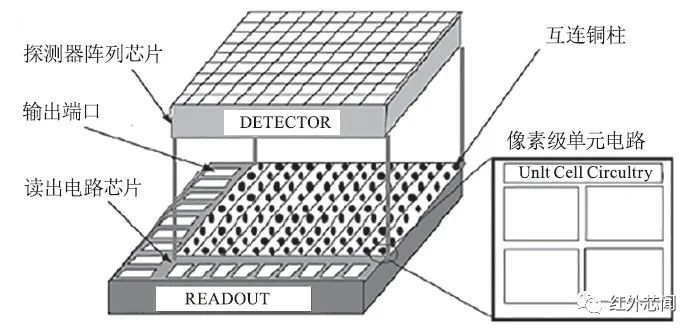

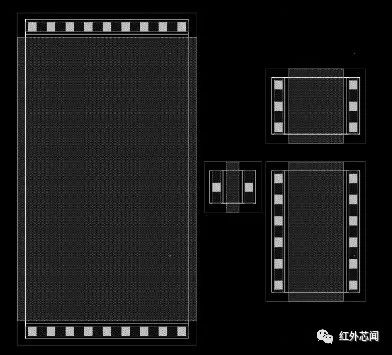

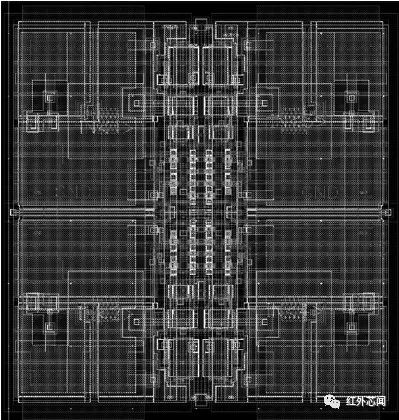

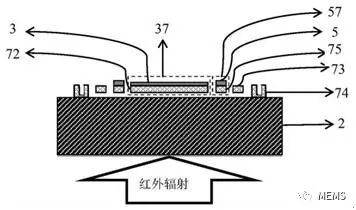

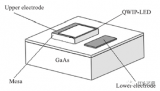

焦平面紅外探測(cè)器的核心是如圖1所示的探測(cè)器陣列與讀出電路倒裝互聯(lián)在一起的混成芯片,其工作原理是探測(cè)器陣列在視場(chǎng)內(nèi)受到特定波段的紅外光激發(fā),每個(gè)像素單元產(chǎn)生微弱的光電流,這些電流通過銦柱流入或流出與之相對(duì)應(yīng)的讀出電路的像素級(jí),通過時(shí)序的控制,在像素級(jí)的積分電容上產(chǎn)生與光電流相應(yīng)的電壓信號(hào),然后讀出電路按序輸出給后端采集系統(tǒng)成像。

圖1 焦平面探測(cè)器混成芯片結(jié)構(gòu)示意圖

據(jù)麥姆斯咨詢報(bào)道,近期,中電科光電科技有限公司的科研團(tuán)隊(duì)在《激光與紅外》期刊上發(fā)表了以“大電荷處理能力紅外探測(cè)器讀出電路像素設(shè)計(jì)”為主題的文章。該文章第一作者為楊斯博。

本文介紹一種具備大電荷處理能力的模擬讀出電路像素級(jí)設(shè)計(jì),在15 μm像元間距內(nèi)最大積分電容達(dá)到832 fF,最大電荷處理能達(dá)到10.92 Me?,且具備良好的線性度。

讀出電路電荷處理能力與紅外探測(cè)器性能的關(guān)系

動(dòng)態(tài)范圍(DR)和噪聲等效溫差(NETD)是衡量紅外探測(cè)器靈敏度的主要指標(biāo)。由于本探測(cè)器需要在110 K這個(gè)相對(duì)較高的溫度下工作,探測(cè)器的暗電流會(huì)隨著工作溫度的升高而迅速增大,從而對(duì)探測(cè)器的最終信噪比造成嚴(yán)重影響,從而造成NETD數(shù)值升高,成像質(zhì)量不佳。從讀出電路著手考慮,需要在讀出電路噪音中需要將KTC噪音降到最低。KTC噪聲是像素單元因復(fù)位動(dòng)作而產(chǎn)生的一項(xiàng)噪聲。

從設(shè)計(jì)的角度考慮減小KTC噪聲,Cp作為分母項(xiàng),可以通過設(shè)計(jì)盡可能大的積分電容達(dá)到減小KTC噪聲的目的,電路的積分電容越大,KTC噪聲Vn就會(huì)越小,相應(yīng)的紅外探測(cè)器性能指標(biāo)也會(huì)越好。

大電荷處理能力像素單元設(shè)計(jì)

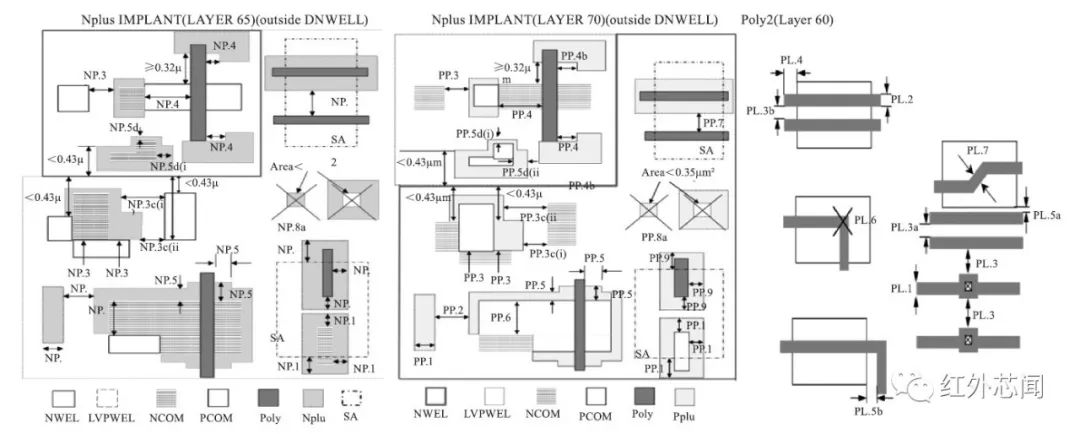

電路的積分電容布置在像素單元內(nèi),一般采用MOS電容設(shè)計(jì),其單位面積電容密度較大。版圖設(shè)計(jì)要遵守符合半導(dǎo)體集成電路制造可靠性的最小的設(shè)計(jì)規(guī)則,圖2列舉出一些版圖設(shè)計(jì)規(guī)則。

圖2 0.18 μm工藝設(shè)計(jì)規(guī)則

設(shè)計(jì)規(guī)則中構(gòu)成的MOS管的金屬和金屬、多晶硅與多晶硅,N阱與NMOS之間有嚴(yán)格的距離限制,違反這些規(guī)則可能導(dǎo)致制造工藝失敗從而引起電路失效。由于本款電路像元中心間距僅為15 μm,因此在非常有限的像素區(qū)域內(nèi)很難布置出大的積分電容,這對(duì)像素單元的版圖設(shè)計(jì)是不小的挑戰(zhàn)。本次設(shè)計(jì)采用如下三個(gè)方法提升像素的積分電容。

輸入級(jí)結(jié)構(gòu)選型

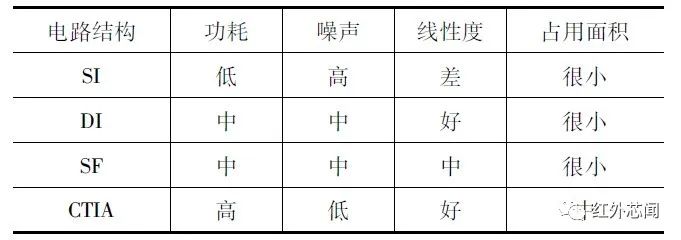

讀出電路像素的輸入級(jí)直接通過銦柱與探測(cè)器相連,常用的輸入級(jí)結(jié)構(gòu)主要有以下幾種:自積分(SI)、直接注入型(DI)、源跟隨器型(SF)、電容跨導(dǎo)放大器結(jié)構(gòu)(CTIA)等,各種結(jié)構(gòu)在噪聲、占用面積等方面各有優(yōu)劣,性能對(duì)比見表1所示。

表1 各種輸入級(jí)結(jié)構(gòu)性能對(duì)比

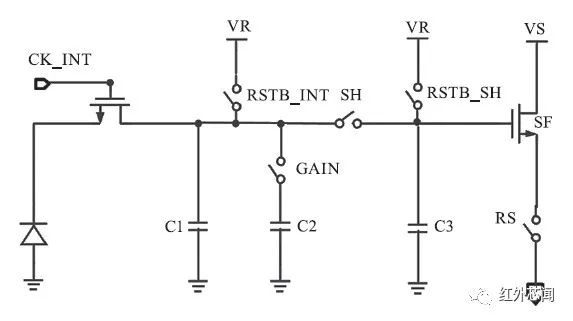

本次設(shè)計(jì)選擇DI搭配SF的像素級(jí)結(jié)構(gòu),這種結(jié)構(gòu)在噪聲表現(xiàn)、線性度和占用面積方面均有不錯(cuò)的表現(xiàn),其典型結(jié)構(gòu)如圖3所示。

圖3 輸入級(jí)結(jié)構(gòu)

優(yōu)化MOS電容設(shè)計(jì)

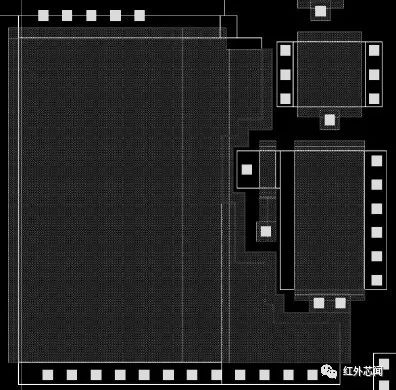

集成電路版圖設(shè)計(jì)一般調(diào)用PDK中標(biāo)準(zhǔn)的MOS器件,通過設(shè)置寬、長(zhǎng)參數(shù)以及插指數(shù)便可直接得到MOS器件的版圖圖形,如圖4所示。這種方法十分方便,缺點(diǎn)是這樣調(diào)用的MOS器件均是規(guī)整的矩形,無法充分利用像素面積。采用自定義設(shè)計(jì)的積分電容MOS器件,手動(dòng)按層繪制,可以設(shè)計(jì)出不規(guī)則圖形的MOS器件,通過細(xì)微調(diào)整,在滿足DRC規(guī)則的前提下,可以充分利用像素空間,優(yōu)化后的MOS電容如圖5所示。

圖4 典型PCELL MOS器件版圖

圖5 自定義設(shè)計(jì)MOS器件版圖

采用立體垂直式MIM電容疊層設(shè)計(jì)

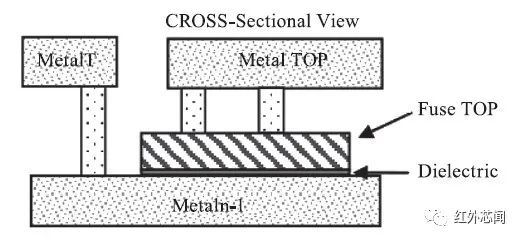

多層金屬布線集成電路工藝的金屬與金屬之間通過絕緣鈍化層隔離,在兩層導(dǎo)體之間夾雜絕緣介質(zhì)的結(jié)構(gòu)形成了天然的電容器,這種電容器稱為MIM電容器,結(jié)構(gòu)如圖6所示。像素單元中的積分電容采用MOS管的柵氧化層電容,但是受像素單元面積限制不能做的很大。MIM電容結(jié)構(gòu)在集成電路后道工藝中制作,不占用MOS器件結(jié)構(gòu)的面積,在底層的MOS電容無法再增大的情況下,可以在MOS電容上方并聯(lián)疊加MIM電容,充分利用像素單元縱向空間結(jié)構(gòu),達(dá)到增大積分電容的目的。

圖6 MIM電容器結(jié)構(gòu)剖面圖

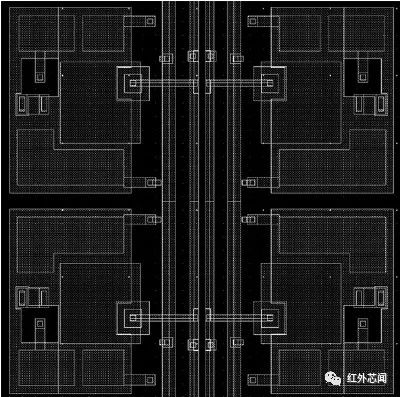

因?yàn)镸IM電容的上下極板均為金屬,在進(jìn)行版圖設(shè)計(jì)時(shí)要綜合考慮貫穿像素陣列的橫向和縱向信號(hào)線,預(yù)留走線空間。還要在數(shù)字信號(hào)線與敏感模擬節(jié)點(diǎn)間布設(shè)屏蔽金屬層,避免數(shù)字信號(hào)對(duì)模擬節(jié)點(diǎn)通過寄生的干擾。經(jīng)過幾十種布線方案的迭代,最終確定疊加MIM電容的尺寸分別為11 μm2、25.25 μm2、8.09 μm2,按照其電容密度2 fF/μm2計(jì)算,最終MIM電容大小分別為22 fF、50.5 fF、16.18 fF。像素中并聯(lián)疊加的MIM電容如圖7所示,其中METALTOP為MIM電容的上極板,METAL5為MIM電容的下極板。像素設(shè)計(jì)最終的完整版圖如圖8所示。

圖7 像素中并聯(lián)的MIM電容

圖8 像素單元完整版圖

讀出電路設(shè)計(jì)仿真結(jié)果

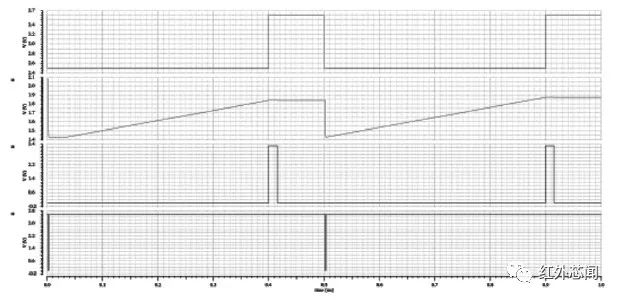

使用ADE軟件對(duì)電路進(jìn)行模擬仿真,仿真積分時(shí)長(zhǎng)設(shè)置為400 μs,仿真結(jié)果如圖9所示。

圖9 像素單元控制信號(hào)與積分電壓仿真結(jié)果

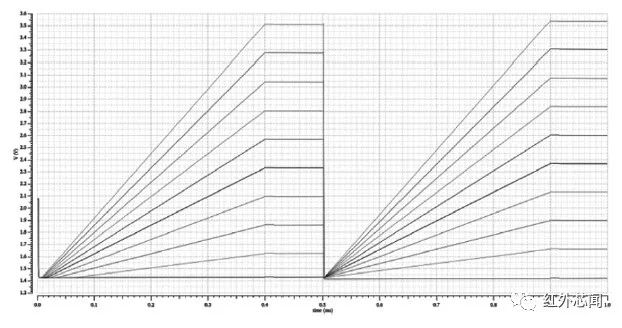

對(duì)像素單元進(jìn)行掃描仿真,設(shè)置探測(cè)器電流范圍0~4.5 nA,步長(zhǎng)0.5 nA,仿真電路輸出電壓值與激勵(lì)電流對(duì)應(yīng)情況,如圖10所示。

圖10 仿真不同激勵(lì)下的積分電壓結(jié)果

結(jié)論

本文論述了紅外焦平面探測(cè)器讀出電路電荷處理能力對(duì)探測(cè)器NETD的影響,針對(duì)減小讀出電路KTC噪聲,設(shè)計(jì)了一款小像元間距大電荷處理能力讀出電路,電路設(shè)計(jì)通過采用DI輸入級(jí)結(jié)構(gòu)、優(yōu)化設(shè)計(jì)MOSCAP和并聯(lián)疊層MIM電容三種方法,提升了像素單元積分電容值,最終使讀出電路實(shí)現(xiàn)了在ITR模式下10.92 Me?的電荷處理能力。經(jīng)過仿真驗(yàn)證讀出電路可以正常工作,且Ⅰ-Ⅴ線性度良好。

審核編輯:劉清

-

二極管

+關(guān)注

關(guān)注

147文章

9702瀏覽量

167566 -

MOS

+關(guān)注

關(guān)注

32文章

1283瀏覽量

94308 -

紅外探測(cè)器

+關(guān)注

關(guān)注

5文章

290瀏覽量

18157 -

電信號(hào)

+關(guān)注

關(guān)注

1文章

840瀏覽量

20673 -

暗電流

+關(guān)注

關(guān)注

0文章

28瀏覽量

10129

原文標(biāo)題:大電荷處理能力紅外探測(cè)器讀出電路像素設(shè)計(jì)

文章出處:【微信號(hào):MEMSensor,微信公眾號(hào):MEMS】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

光子探測(cè)器

高增益低噪聲的探測(cè)器讀出電路設(shè)計(jì)

三波段紅外火焰探測(cè)器參考設(shè)計(jì)

如何設(shè)計(jì)一種Vernier陽極探測(cè)器的信號(hào)處理電路?

如何去設(shè)計(jì)一種高增益低噪聲的探測(cè)器讀出電路?

光學(xué)讀出紅外探測(cè)器的兩種制造方法

紅外探測(cè)器有幾種_紅外探測(cè)器作用

一種用于封裝長(zhǎng)波QWIP-LED量子阱紅外探測(cè)器的結(jié)構(gòu)

被動(dòng)式紅外探測(cè)器和主動(dòng)式紅外探測(cè)器有什么區(qū)別

紅外探測(cè)器:熱探測(cè)器與光子探測(cè)器

一種接近像素級(jí)讀出的超導(dǎo)納米線單光子探測(cè)器(SNSPD)陣列

探索紅外熱成像探測(cè)器的基礎(chǔ)原理

一種大電荷處理能力紅外探測(cè)器讀出電路像素設(shè)計(jì)

一種大電荷處理能力紅外探測(cè)器讀出電路像素設(shè)計(jì)

評(píng)論