引言

在過去的幾年中,MOSFET結構從平面結構改變為鰭型結構(FinFETs ),這改善了短溝道效應,并導致更高的驅動電流泄漏。然而,隨著柵極長度減小到小于20nm,進一步小型化變得越來越困難,因為它需要非常窄的鰭寬度,這導致驅動電流惡化。

在亞納米工藝中,SiGe有望用于p-FET溝道,而Si仍然作為n-FET的溝道材料,就雙溝道結構的各向異性干法刻蝕而言,需要同時刻蝕Si和SiGe。然而,不僅通過鹵素化學,而且通過物理濺射,導致SiGe蝕刻速率比Si快。 因此,有必要找到一種蝕刻化學物質來獲得相對于SiGe的選擇性Si蝕刻。

實驗與討論

在這項研究中,英思特使用日立微波電子回旋共振(M-ECR)系統。在該系統中,源頻率和晶片偏置頻率分別為2.45 GHz和400 kHz。腔室具有噴淋板,工藝氣體通過該噴淋板引入。一個300mm的晶片用靜電吸盤固定在電極上,晶片的溫度由背面氦冷卻系統控制。

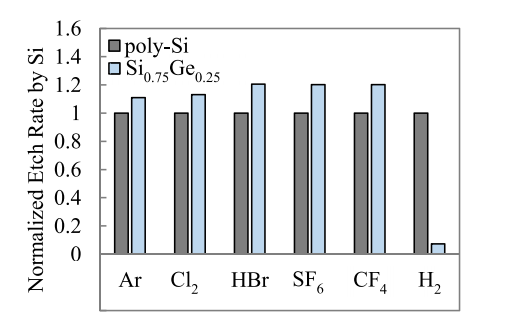

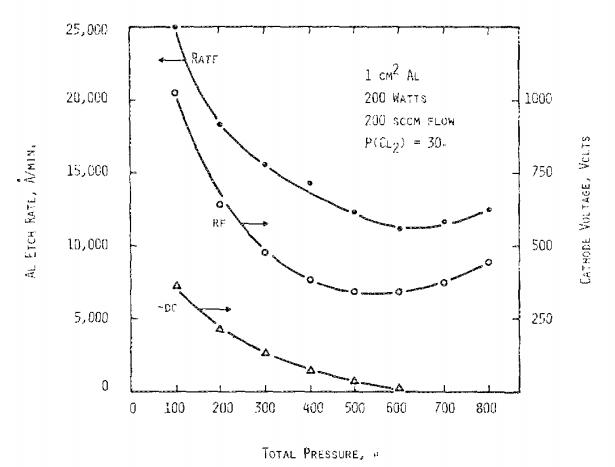

由硅蝕刻速率標準化的硅鍺蝕刻速率如圖1所示。使用鹵素化學等離子體(Cl2、HBr、SF6和CF4),SiGe的蝕刻速率高于Si。甚至通過Ar等離子體的物理濺射顯示出比Si蝕刻速率更高的SiGe蝕刻速率。

英思特提出了幾個原因來解釋Si上的選擇性SiGe蝕刻:1、可能是由于Si-Ge (3.12 eV)和Ge-Ge (2.84 eV)的鍵合能低于Si-Si (3.25 eV),2、可能是由選擇性去除高應變層以穩定系統引起的,因為在Si上外延生長的SiGe由于晶格失配而發生應變。 3、是因為SiGe的帶隙較窄,電子效應可能導致SiGe蝕刻的化學反應增強。

圖1:不同等離子體的SiGe蝕刻速率

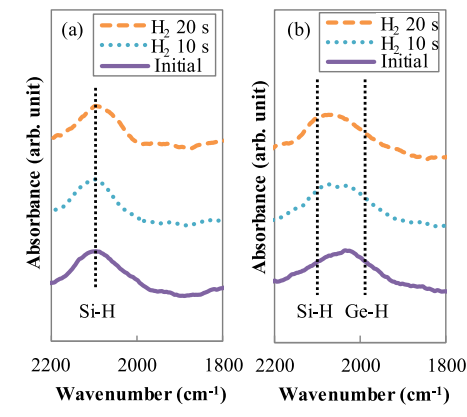

圖1:不同等離子體的SiGe蝕刻速率為了了解Si-SiGe的蝕刻機理,我們研究了ATR-FTIR氫等離子體暴露后的Si和Si0.5Ge0.5。.圖2為氫等離子體暴露10 s和20 s后Si和SiGe的吸光譜。對于圖2(a)所示的Si表面,在氫等離子體暴露10s和20s后沒有變化。

另一方面,對于圖2 (b)所示的SiGe表面,在初始樣品中發現Ge-H鍵和Si-H鍵之間存在寬峰。隨著氫等離子體暴露時間的增加,峰值向Si-H方向移動,這意味著Si-H鍵被選擇性地在Ge-H鍵上產生。

圖2:(a) Si和(b) SiGe暴露于氫等離子體中10和20 s的吸光度光譜

圖2:(a) Si和(b) SiGe暴露于氫等離子體中10和20 s的吸光度光譜結論

在本研究中,英思特研究了硅蝕刻控制在硅雙通道鰭圖案的應用。結果表明,不僅鹵素化學性質和物理濺射蝕刻SiGe對硅有選擇性,而氫等離子體蝕刻硅對SiGe也有選擇性。這是因為SiH鍵的形成在能量上有利于Ge-H鍵的形成,即表面Ge會阻止蝕刻副產物的形成。

英思特還通過提出了一個離子能量沉積模型來解釋蝕刻速率隨著離子能量的增加而降低的現象。我們利用所開發的蝕刻化學方法,將Si和SiGe鰭的CDs和蝕刻深度的差異從正值控制到負值。在此研究中,我們還表明,該低溫氫等離子體在SiGe表面會誘導硅偏析。

審核編輯 黃宇

-

等離子體

+關注

關注

0文章

126瀏覽量

14278 -

光纖

+關注

關注

19文章

3952瀏覽量

73628 -

SiGe

+關注

關注

0文章

63瀏覽量

23515 -

蝕刻

+關注

關注

9文章

419瀏覽量

15509

發布評論請先 登錄

相關推薦

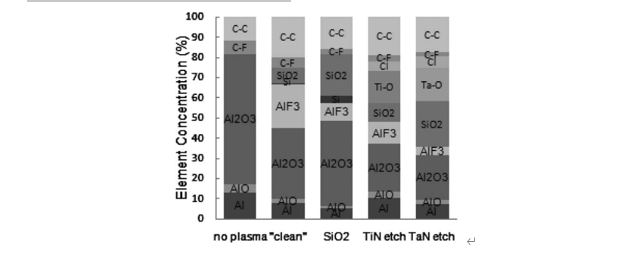

金屬蝕刻殘留物對對等離子體成分和均勻性的影響

等離子體蝕刻和沉積問題的解決方案

PCB多層板等離子體處理技術

PCB電路板等離子體切割機蝕孔工藝技術

PCB板制作工藝中的等離子體加工技術

低溫等離子體廢氣處理系統

TDK|低溫等離子體技術的應用

等離子體應用

大氣壓低溫等離子體的研究

低溫等離子體氣體溫度參數研究

低溫等離子體處理廢氣

低溫等離子體發生器的應用資料說明

低溫等離子體技術的應用

硅雙通道光纖低溫等離子體蝕刻控制與SiGe表面成分調制

硅雙通道光纖低溫等離子體蝕刻控制與SiGe表面成分調制

評論