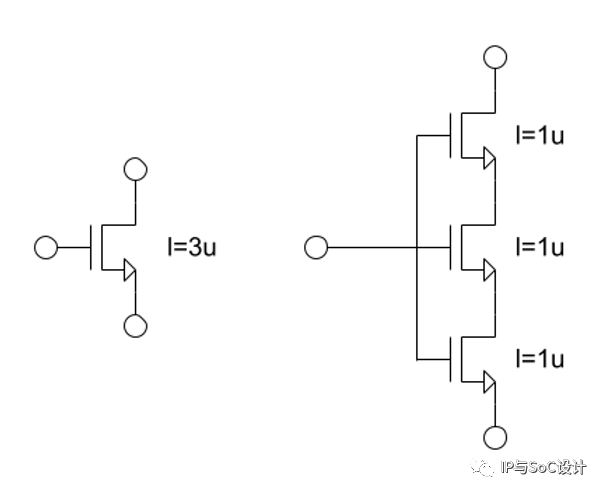

在28nm以下,最大器件長度限制意味著模擬設(shè)計者通常需要串聯(lián)多個短長度MOSFET來創(chuàng)建長溝道器件。這些串聯(lián)連接的器件通常被稱為堆疊MOSFET或堆疊器件。例如,將三個1um MOSFET串聯(lián)堆疊可產(chǎn)生溝道長度為3um的有效器件。

堆疊MOSFET在現(xiàn)代模擬設(shè)計中非常常見,但并非沒有問題。主要問題是電容增加和面積增大。電容的增加很大程度上是由于器件周圍互連的增加。總體柵極面積和柵極電容與非堆疊等效物保持相似,但在互連上存在額外的寄生電容。與單個長通道器件相比,堆疊中器件的物理分離增加了整體設(shè)計面積。

當(dāng)在電路中使用堆疊的MOSFET時,布局質(zhì)量變得比平時更加關(guān)鍵。糟糕的布局顯著增加了寄生電容和設(shè)計面積,并可能導(dǎo)致電路不能滿足所需的性能特性。布局工程師必須非常小心地設(shè)計此類設(shè)備的布局。在這些較小的流程節(jié)點上工作的大多數(shù)設(shè)計師都經(jīng)歷過布局前和布局后模擬非常不同的情況。通常,這是由于堆疊器件上的互連寄生效應(yīng)造成的。

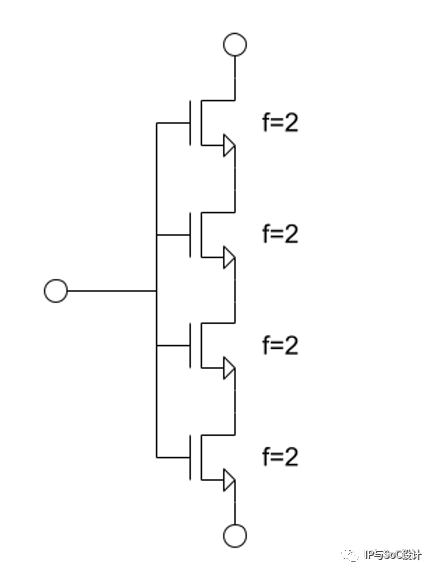

讓我們來看看為堆疊MOSFET實現(xiàn)高質(zhì)量布局的幾種方法。下面的子電路顯示了四個nmos MOSFET,它們堆疊在一起形成了一個長溝道器件。

在這個電路中,你可以看到所有的柵極引腳都連接在一起(所有四個體連接也是如此);你還可以看到MOSFET已經(jīng)串聯(lián)連接,其中一個的漏極連接到下一個的源極。因為在這種情況下,每個器件都是一個簡單的單指MOSFET,所以在設(shè)計這種結(jié)構(gòu)的布局時,我們可以使用簡單的擴散共享布局模式。

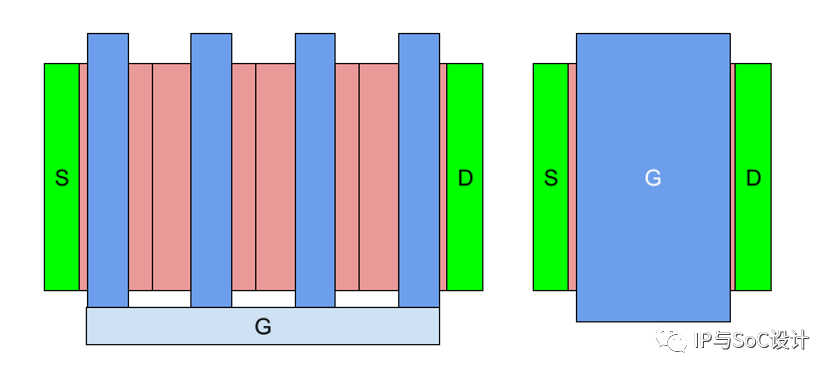

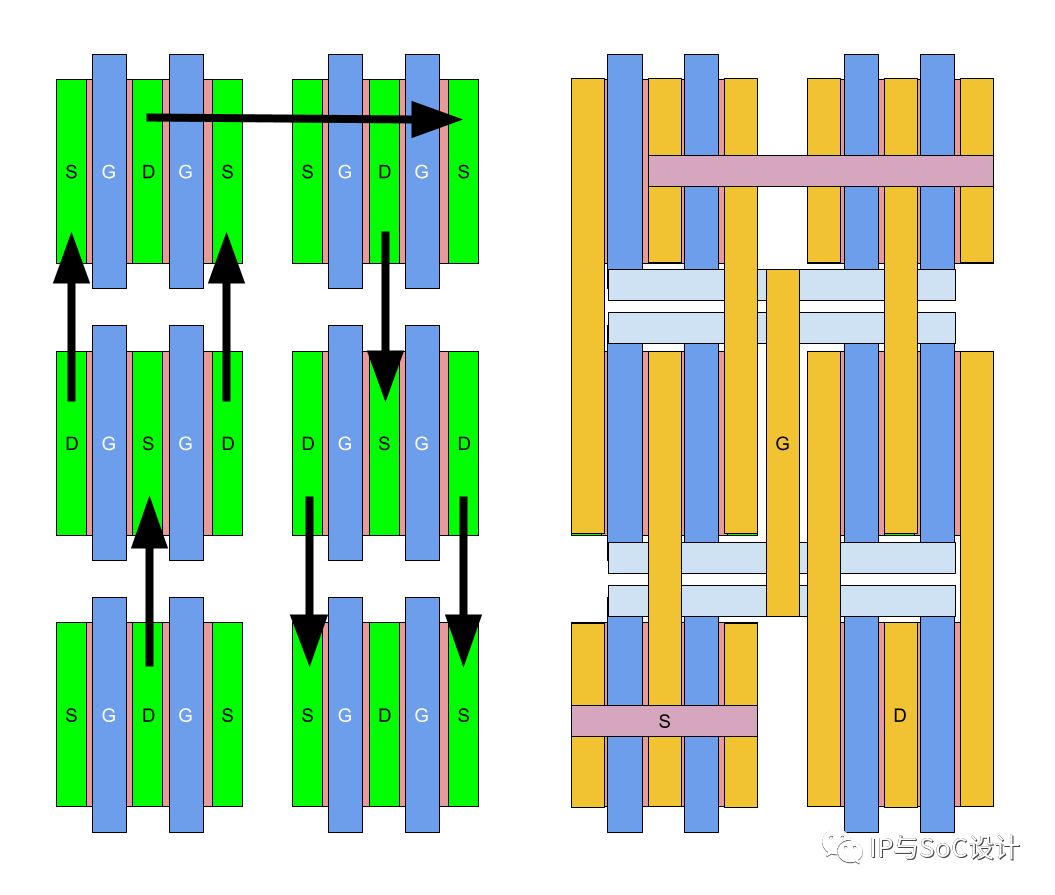

簡單堆疊案例的布局如上圖左側(cè)所示;您可以看到,幾乎沒有額外的互連,因為等效的長溝道器件(右側(cè))也需要多晶接觸。在這種情況下,面積懲罰是顯著的,但這是不可避免的,并由poly-min間距規(guī)則決定。

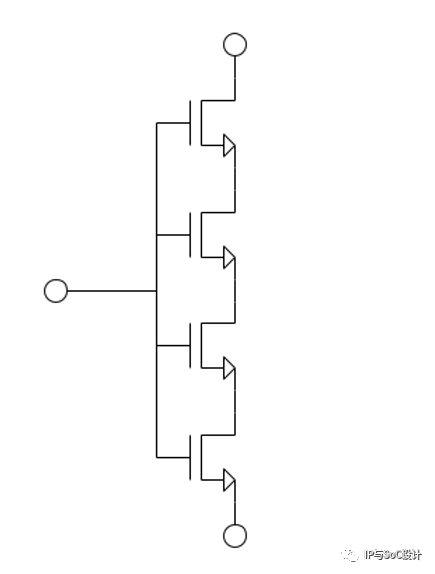

這種方法的另一個問題是,非常長的有效器件可能導(dǎo)致長的擴散共享鏈。但是,可以將長鏈折疊成多行,如下所示。折衷的是,這增加了額外的互連,并進(jìn)一步增加了堆疊器件的電容。

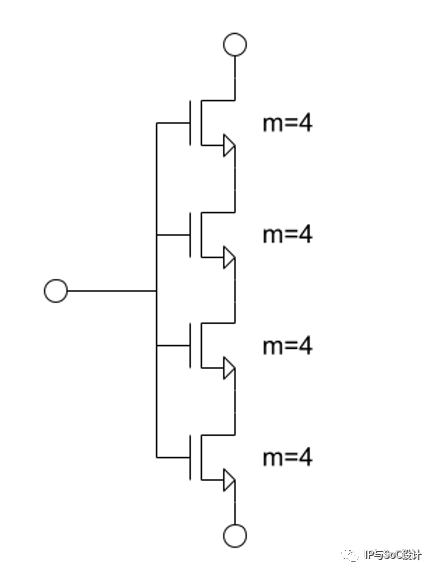

下面的電路顯示了電路設(shè)計者想要在電路中使用兩個指狀MOSFET以實現(xiàn)更好匹配的情況。

兩個手指設(shè)備不能通過擴散共享連接,因此我們必須使用不同的放置和路由方法。為了實現(xiàn)緊湊的布局,設(shè)備按列連接,而不是前面示例中所示的基于行的模式。

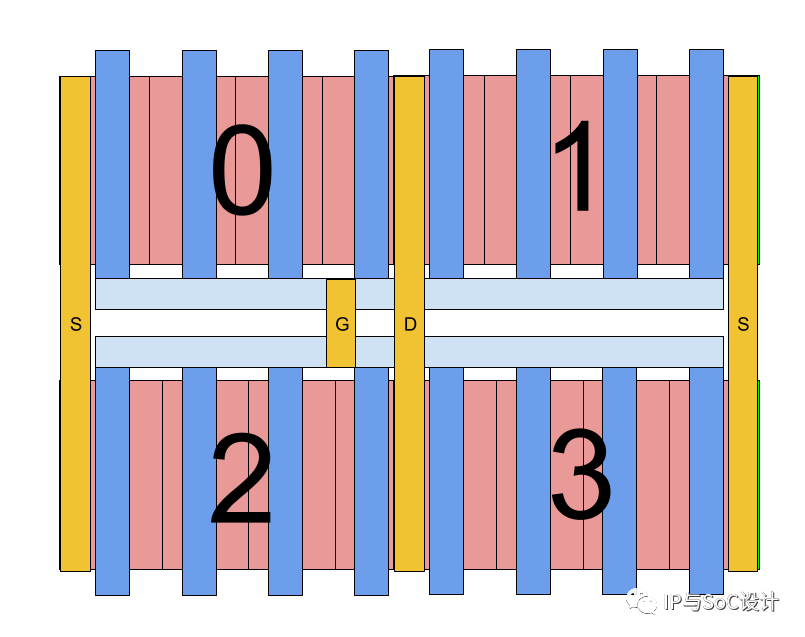

左邊的圖像顯示了連接模式,一個器件的漏極垂直連接到下一個器件源極。正如你所看到的,連接是按列運行的,交替的器件具有不同的參數(shù),可以在MOSFET的漏極中心和源極中心變體之間交換。交換的觸點允許在列中的設(shè)備之間進(jìn)行直線布線,避免了彎曲和額外的過孔。

您可以在右側(cè)看到此基于列的模式的布線模式。存在額外的互連,但并不明顯多于通常用于接觸增強所需的互連。

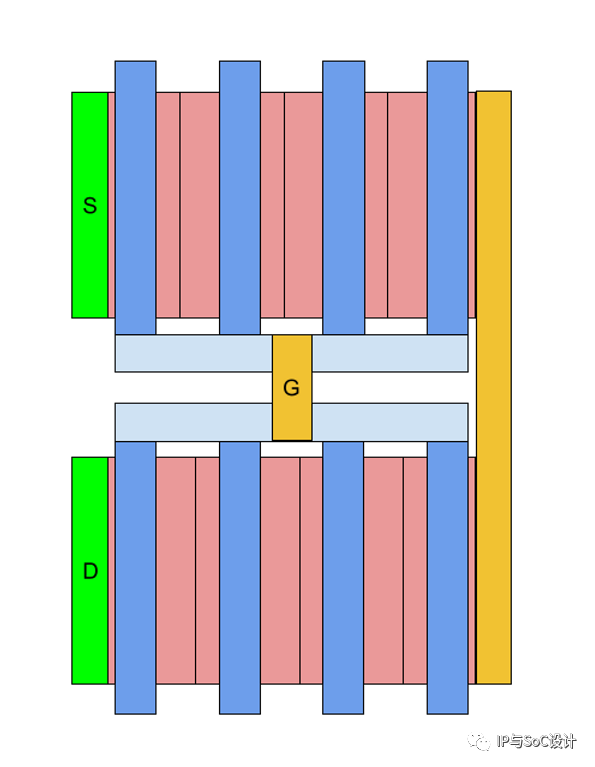

電路設(shè)計者還可以為堆疊的器件指定m因子。堆疊和m因子拓?fù)湓试S電路設(shè)計者使用許多小型MOSFET構(gòu)建具有長溝道和寬溝道的器件。該示例示出了具有m因子4的單指堆疊器件。

在下面的布局中,您可以看到該模式具有上一個基于行的模式的四個副本,這些副本的排列確保設(shè)備之間的額外路由量最小。

在本文中,我展示了一些可以與堆疊MOSFET一起使用的基本模式。在所有這些例子中,器件的放置和布線對于實現(xiàn)高質(zhì)量布局至關(guān)重要。

Pulsic新的動畫預(yù)覽工具中的技術(shù)將放置和布線結(jié)合在一個操作中。這允許動畫預(yù)覽實現(xiàn)上面顯示的堆疊設(shè)備的最佳布局模式類型。必須優(yōu)化每個設(shè)備的確切位置、方向和參數(shù)化,以獲得所需的結(jié)果。同時,該工具必須考慮通過每個設(shè)備的電流,以使互連復(fù)雜性和長度最小化。模擬布局總是需要仔細(xì)平衡多個相互競爭的優(yōu)先級;沒有一種做事方式在任何情況下都能奏效。

審核編輯:劉清

-

MOSFET

+關(guān)注

關(guān)注

147文章

7240瀏覽量

214267

原文標(biāo)題:博文速遞:Stacked MOSFETs in analog layout

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

MOSFET和封裝技術(shù)的進(jìn)步使得TI能夠成功應(yīng)對挑戰(zhàn)

驅(qū)動功率MOSFET,IBGT,SiC MOSFET的PCB布局需要考慮哪些因素?

CAD入門學(xué)習(xí):CAD文字堆疊的樣式

HarmonyOS Java UI 之 StackLayout 布局示例

轉(zhuǎn):HarmonyOS Java UI 之 StackLayout 布局示例

芯片堆疊的主要形式

在模擬版圖設(shè)計中堆疊MOSFET

什么是堆疊設(shè)計

關(guān)于模擬布局中MOSFET差分對寄生效應(yīng)的平衡問題探討

平衡MOSFET差分對中的模擬布局寄生效應(yīng)

基于序列對和模擬退火算法的布局問題研究

淺談PCB布局設(shè)計的層堆疊規(guī)劃

什么是交換機堆疊?有哪些設(shè)備可以堆疊?如何建立堆疊?

采用高側(cè)N-MOSFET的堆疊式BQ769x2設(shè)計注意事項

MOSFET并聯(lián)在高功率設(shè)計中的應(yīng)用

模擬布局中的堆疊MOSFET設(shè)計

模擬布局中的堆疊MOSFET設(shè)計

評論