PCI Express (PCIe) 是一種高性能通用 I/O 互連協議,廣泛用于各種計算產品和通信產品。由于時延低、帶寬明顯要更高,因此業界正在融合到 PCIe,作為高速串行總線標準。PCIe在NVM Express SSD應用中尤其流行。

PCIe 既有串行通信接口,又有存儲接口,這 一點與 SAS 和 SATA 不同,因此實現了額外的行業擴充能力。PCIe 在跟復合 (系統/主機) 與端點 (插件) 之間基于點到點總線拓撲,支持全雙工通信。這些規范是由 PCI-SIG 開發和維護的,這是一家由 900 多家公司組成的協會。

PCIe 物理層包括

差分低壓100MHz基準時鐘

可以擴充通路寬度:x1, x2, x4, x8, x12, x16, x32

可以擴充速度:2.5GT/s(Gen1), 5GT/s(Gen2), 8GT/s(Gen3), 16GT/s (Gen4)

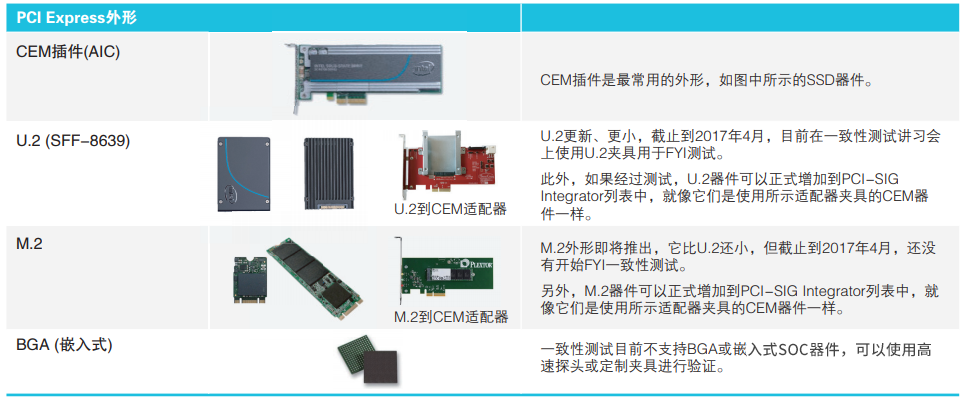

在一致性測試中使用不同的連接器,如CEM、U.2(SFF-8639)、M.2或直接焊接到PCB

ChrentPCI Express 它用在哪里?

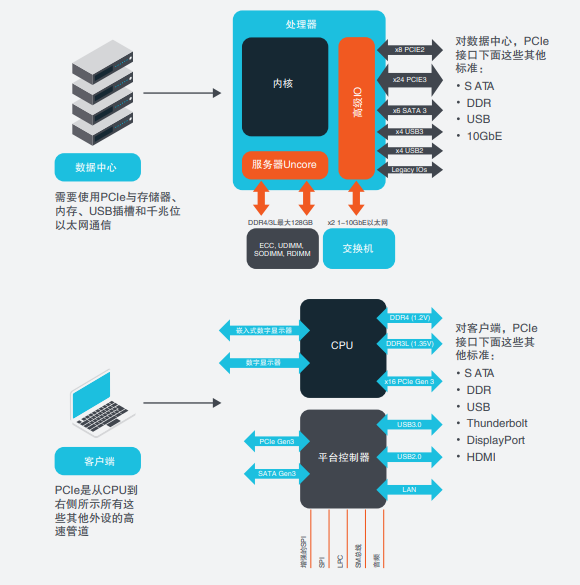

PCIe 是數據中心和客戶端應用中使用的主要的新興高性能存儲和串行總線。PCIe 在外設之間實現了數據通信。

數據中心應用和客戶端應用都有一個核心處理器, 為主機系統上的架構提供原始處理能力。這兩種應用還必須接口各種外設器件,如 SATA 驅動器、 USB 設備等。在跟復合主機與端點器件之間,通常有許多路長損耗通道和連接器,帶來了噪聲、串擾、 定時不規則特點和其他損傷。因此,客戶端和數據中心側的 PCIe 器件必須能夠可靠地演示 PCI 規定的一致性,補償損傷,與 PCIe 器件互操作。

ChrentPCIe Gen4 最新進展

由于業界需要提高數據吞吐量和帶寬吞吐量,因此 PCIe 數據速率必須提高,以跟上需求發展步伐。所以 Gen4 中最大的變化之一,是數據速率提高了 2 倍,從 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

下面列明了最新Gen4標準的主要增強功能

16GT/s, 使用加擾 , 與 8GT/s 相同 , 編碼與Gen3相比無變化 (128b/130b)

對加壓的Rx眼圖參數,RJ (隨機性抖動) 從3ps (PCIe3)下降到~1ps (PCIe4)

Gen4連接器向下兼容Gen1/2/3

與行為Rx EQ數據速率有關

限定通道:對更長的通道和/或第二個連接器,要求使用中繼器 (再驅動器和再定時器)

測試通道大約長12”,總損耗-28dB

在同一個器件上同時測試Gen3和Gen4時,被測試的各個預置值數量將翻一倍, 總 計22個。Gen3 有11個預置值(P0~P10),Gen4有11個預置值 (P0~P10)

新的SRIS獨立RefClk模式-SRNS-單獨的獨立RefClk, 沒有SSC結構-SRIS-單獨的獨立RefClk,采用SSC結構

新的Rx通路裕量功能測量通道最后的眼高 (EH)/ 眼寬 (EW) 裕量

Gen4的最小眼高已經下降到15mVpp

Gen4 CEM規范發布了rev 0.5

ChrentPCIe Refclk 結構

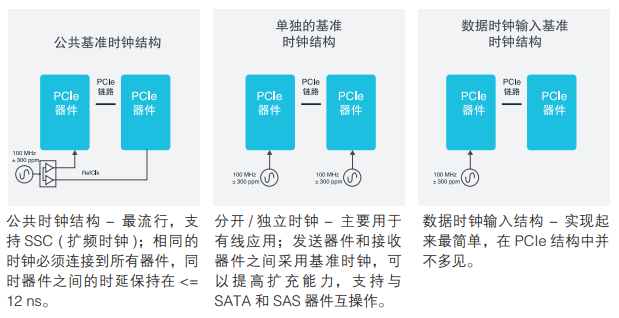

為了方便發射器件和接收器件可靠地傳輸數據,PCI-SIG 對基準時鐘提出了非常嚴格的要求。標準規定使用 100 MHz 時鐘 (Refclk),發 射器件和接收器件上的頻率穩定性大于 ±300 ppm,并支持三種不同的時鐘結構,同時協調根復合芯片和端點芯片。

在傳統上,PCIe 一直采用公共時鐘結構,跟復合和芯片可以偏離相同的時鐘配置,而不是以不同的間隔運行,后者測試起來更具有挑戰性。公共時鐘是 一種更加精確的結構,但整合到系統中的靈活性較差。通過采用 Gen4 標準,系統可望更多地采用分開 / 獨立的時鐘結構。時鐘穩定性必不可少,以支持三種不同的時鐘輸入結構。

ChrentPCI Express 外形

為了方便發射器件和接收器件可靠地傳輸數據,PCI-SIG 對基準時鐘提出了非常嚴格的要求。標準規定使用 100 MHz 時鐘 (Refclk),發射器件和接收器件上的頻率穩定性大于 ±300 ppm,并支持三種不同的時鐘結構,同時協調根復合芯片和端點芯片。

Chrent一致性測試預置值

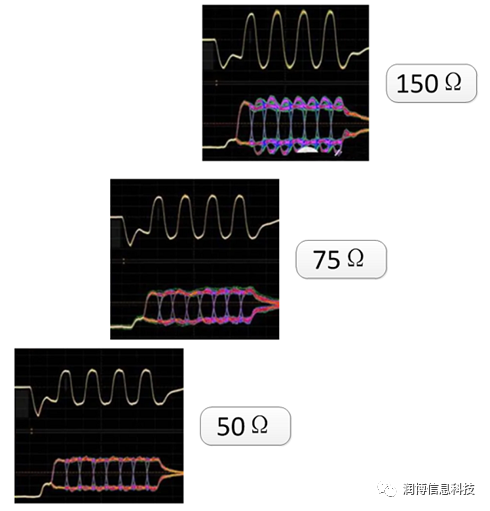

為通過一致性測試,實現互操作,每臺器件都要求進行 PCI-SIG 認證,它基于一個預置值或發射機均衡設置列表,從每秒 2.5 Gb/s 的低 數據速率直到最新的 16 Gb/s 的高數據速率。這些預置值用來均衡通道損耗,優化鏈路上的信號完整性。每個預置值都是主機應用到端 點的下沖和去加重的具體組合。

下表詳細列出了 Gen3 和 Gen4 的 11 種預置值。DUT 必須支持所有預置值。為降低測試時間,提高自動化速度,建議使用 100MHz 時鐘突發,作為一致性測試夾具的輸入,在這些預置值之間快速切換。如果您可以使用 100MHz 脈沖撥碼開關自動執行預置測試,那么您可以節約寶貴的測試時間,因為您可以自動采集和分析各個指標,如抖動、電壓和定時。

下面預置值同時適用發射機測試和接收機測試。

Chrent發射機 (Tx) 測試基礎知識

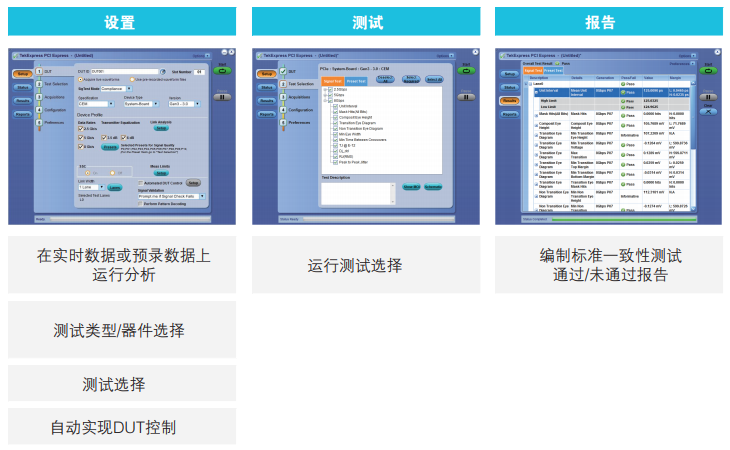

下面列明了對 PCIe 發射機自動進行一致性測試的各個步驟。自動軟件至關重要,因為它可以使用 100 MHz 基準時鐘自動切換預置測試模式,與手動按鈕進行撥碼切換相比,可以把測試時間縮短兩倍。

許多 PCI-SIG 測試早期實現者更愿意使用泰克 DPOJET 和 SDLA 軟件之類的工具,來完成早期 Gen4 表征和調試。

Chrent基本規范發射機 (Tx) 測試

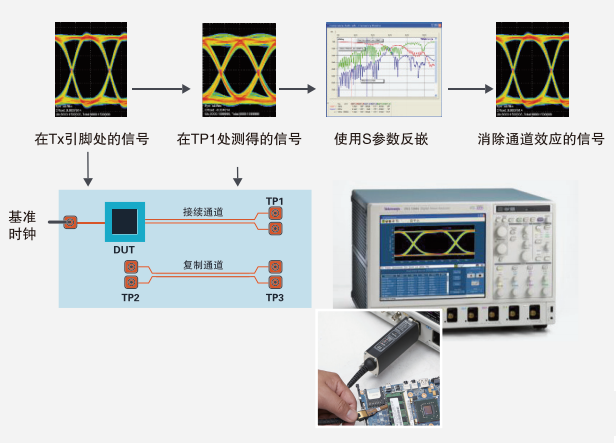

在芯片器件的基本發射機測試中,直接規定了發射機引腳上的測量項目。由于有時不可能接入引腳,因此應在盡可能靠近這個基準點的位置執行測量。

在芯片級可通過多種方式完成這一測試

如果您深入了解類似的復制通道的S參數,那么可以反嵌接續通道的損耗。您可以看到發射機引腳上的信號是什么樣的,而沒有增加通道影響。

在示波器上使用均衡或CTLE,均衡消除通道損耗。

使用高帶寬探頭,探測位置應盡可能靠近發射機引腳 。

示波器可以使用 SDLA、Seasim 和 SigTest 之類 的軟件工具,執行嵌入 / 反嵌、均衡和眼圖分析。這種軟件級分析允許設計人員在試產前優化和調試芯片性能,節約時間、資金及全面調試。確保采用的測量系統足夠靈活,能夠測試和調試被測器件的特定功能。

ChrentCEM 和 U.2 規范發射機 (Tx) 測試

在芯片器件的基本發射機測試中,直接規定了發射機引腳上的測量項目。由于有時不可能接入引腳,應在盡可能靠近此基準點的位置執行測量。

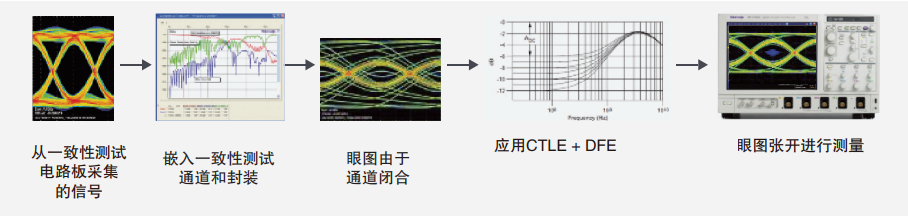

系統和插件在CEM級發射機測試中,會像接收機分片器看到的那樣測量發射機的信號完整性,但由于外形及測試過程中使用的夾具,不可能直接接入信號。為保證測量精度,應實現下面介紹了兩個重要組件。

1. 把一致性測試通道的性能特點向回嵌入到正在測量的信號中。這要求深入了解通道的插入損耗和S參數。由于這個原因,PCI-SIG為CEM測試提供了一致性測試夾具及已知的S參數。

2. 使用軟件工具應用通道均衡,測量和分析通道末端張開的眼圖。PCI-SIG提供了一個軟件工具,稱為SIG-Test,應用與PCI-SIG特性有關的行為均衡器,提供測試通過/未通過結果。定制示波器軟件,如泰克DPOJET和SDLA,可以從閉上的眼圖到張開的眼圖,全面表征和調試均衡的信號。

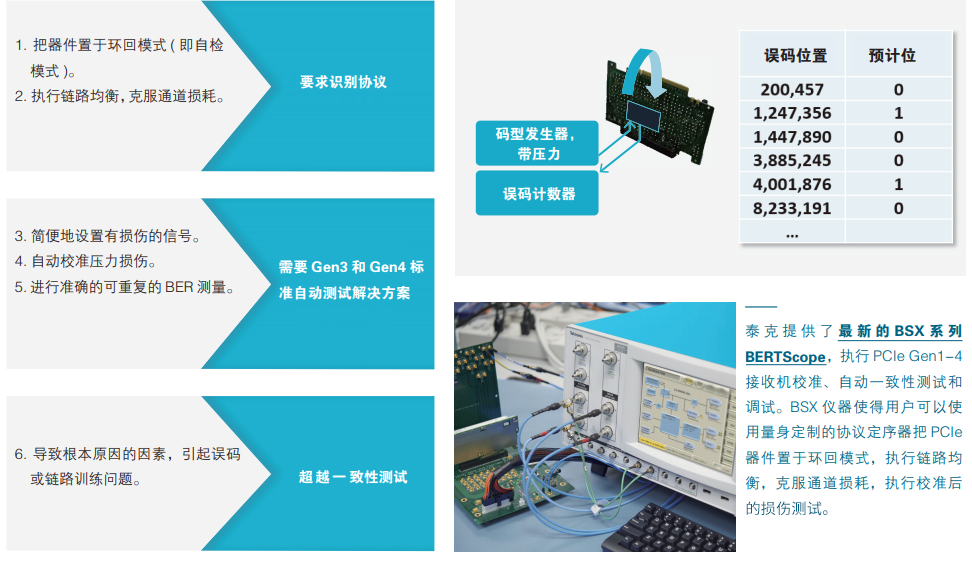

Chrent接收機 (Rx) 測試基礎知識

ChrentPCIe 測試和調試設置中的關鍵考慮因素

由于Gen 4標準的出現,PCIe的速度和復雜度正不斷提高,工程師面臨著新的設計挑戰、更短的產品開發周期,同時需要了解新的標準規范及新的一致性測試要求。

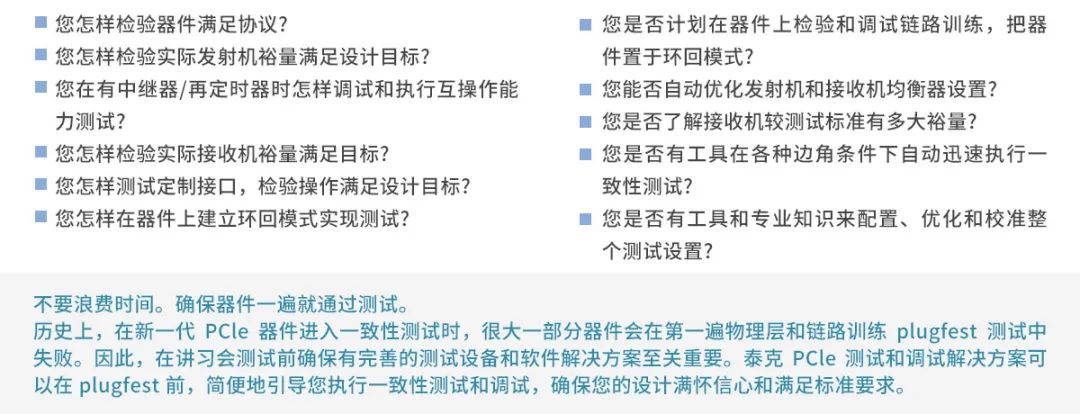

在您處理Gen3或Gen4 PCIe器件測試和調試前,要問以下幾個關鍵問題:

-

測試

+關注

關注

8文章

5375瀏覽量

127056 -

PCIe

+關注

關注

15文章

1260瀏覽量

83184 -

串行通信接口

+關注

關注

0文章

17瀏覽量

9588

發布評論請先 登錄

相關推薦

信號完整性與電源完整性的仿真分析與設計

高速串行信號的信號完整性和物理層測量與分析

PCIe物理層的基本概念

PCIe Tx/Rx 物理層信號完整性測試方法詳解

PCIe Tx/Rx 物理層信號完整性測試方法詳解

評論