首先需要指出本文題目所指的仿真指的是功能仿真,即不帶時序信息的仿真。

每個FPGA developer都會做功能仿真驗證RTL代碼功能的正確性。我們知道在功能仿真中是沒有考慮延遲的,組合邏輯是零延遲,寄存器也是在時鐘跳變沿瞬時完成采樣。

對于同步電路來說,功能仿真完成后,再加上靜態時序分析,我們基本能確保設計的電路能正確工作(有一些情況例外,比如綜合的結果和仿真的結果不同)。但是對于異步電路,功能仿真的零延遲特性沒法很好模擬跨時鐘域時的情況,在靜態時序分析時我們一般也是false path,不做后仿真(時序仿真)則很難確保跨時鐘域電路設計的正確性。

那么我們在做仿真時有沒有辦法更好得模擬跨時鐘域的情況?

先看看跨時鐘域有什么特性?一是亞穩態導致采樣到的信號出現隨機值,二是跨時鐘域不是瞬時結束的,而是會持續一段時間。

依據此特性,我們在功能仿真時可以手動給跨時鐘域信號加延遲。延遲的大小可以是random的一個值來更好得模擬隨機采樣值,而且最好是能在真實延遲的大概范圍。

舉個例子。

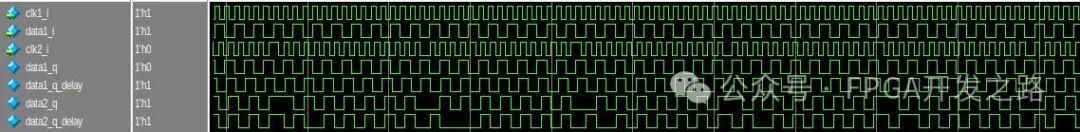

假設我們是跨時鐘域采樣一個bit的信號,輸入信號不停在0和1之間跳變。如下圖所示,data1_q是輸入單bit信號的寄存器輸出,data1_q_delay則是對data1_q添加延遲后的信號。data2_q是在目的時鐘域clk2對data1_q的采樣,data2_q_delay則是在目的時鐘域對data1_q_delay的采樣。

從圖中可以看到,data2_q在跨時鐘域時只有一個cycle采到錯誤的值,data2_q_delay則較好的模擬出了采樣值的隨機性,而且會持續多個cycle出現“隨機”值。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5363瀏覽量

121172 -

靜態時序分析

+關注

關注

0文章

28瀏覽量

9608 -

時鐘信號

+關注

關注

4文章

453瀏覽量

28666

原文標題:跨時鐘域如何仿真?

文章出處:【微信號:FPGA開發之路,微信公眾號:FPGA開發之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IGBT驅動波形負壓關斷時有上升尖峰,請問有沒有辦法可以抑制?

gpio0有沒有辦法切換復位以防止獲取時鐘輸出?

有沒有辦法模擬FET的大信號時域

TCL有沒有辦法在沒有重新運行模擬的情況下獲得HDL對象的值?

有沒有辦法在不清潔ZMK的情況下更換新電池?

AT+HTTPCLIENT有沒有辦法打斷命令?

如何利用FPGA設計一個跨時鐘域的同步策略?

有沒有辦法像debug RTL代碼一樣將UVM中變量拉到波形上看呢?

在做仿真時有沒有辦法更好得模擬跨時鐘域的情況?

在做仿真時有沒有辦法更好得模擬跨時鐘域的情況?

評論