電阻是如何實現上下拉功能的呢?

上下拉功能是指在電路中通過連接電阻來實現對信號的上拉和下拉控制。在數字電路中,上拉和下拉功能通常用于控制輸入端的電平狀態,確保輸入端在沒有外部信號輸入時能夠保持穩定的電平狀態,以避免未定義或干擾信號的產生。

實現上下拉功能的核心是使用特定大小的電阻與輸入端相連,通過不同的電阻值來實現上拉或下拉效果。具體的實現方法有下面幾種:

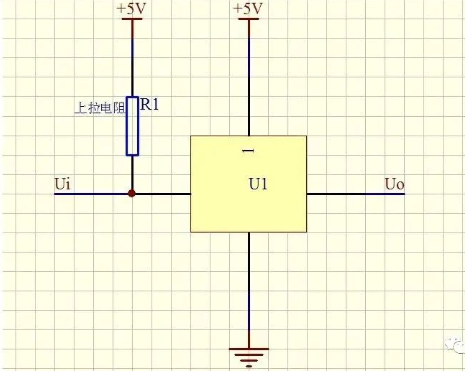

1. 上拉電阻:

上拉電阻通常與輸入端的引腳相連,以確保在沒有外部信號輸入時,輸入端能夠被上拉到高電平狀態。上拉電阻的作用是將輸入端與電源(通常是Vcc)相連接,通過電阻上的電流使得輸入端始終保持在高電平。

2. 下拉電阻:

下拉電阻通常與輸入端的引腳相連,以確保在沒有外部信號輸入時,輸入端能夠被下拉到低電平狀態。下拉電阻的作用是將輸入端與地(通常是GND)相連接,通過電阻上的電流使得輸入端始終保持在低電平。

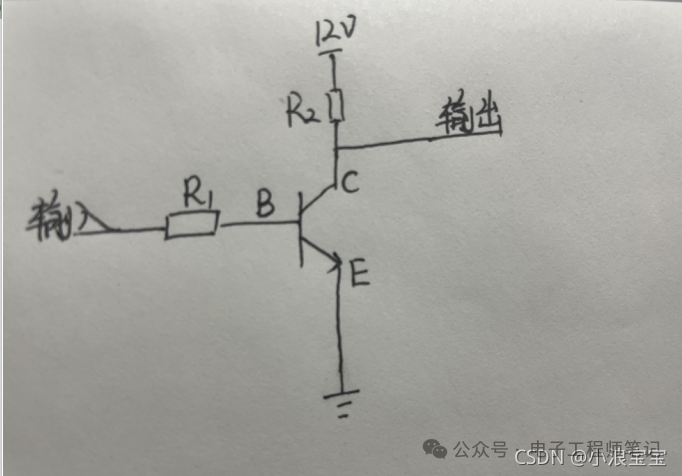

3. 上下拉電阻組合:

在一些應用中,可能需要同時實現上拉和下拉功能。此時可以通過使用上下拉電阻的組合來實現。一種常見的做法是使用上拉電阻與下拉電阻并聯,以確保輸入端在沒有外部信號輸入時能夠保持中間狀態(通常是Vcc/2或GND/2)。這種組合可以在需要既能拉高又能拉低的輸入端上使用,以提供更大的靈活性。

上下拉電阻的大小通常是根據具體應用的要求和特定的芯片規格來確定的。選擇合適的電阻值是保證輸入端能夠在正確電平狀態下工作的關鍵。如果電阻值太小,可能會導致電流過大,消耗過多功耗;如果電阻值太大,可能會導致輸入端的電平不穩定或對外部信號的響應不敏感。

此外,還需要注意的是,在使用上下拉電阻時,必須確保電阻與信號源(如傳感器、開關等)之間沒有其他電路連接,以免短路或干擾信號的產生。同時,還需要注意選擇合適的電阻類型和功率承受能力,以滿足具體應用的需求。

總之,上下拉電阻是實現對信號的上拉和下拉控制的重要手段。通過選擇合適的電阻值和電路連接方式,可以確保輸入端在沒有外部信號時保持穩定的電平狀態,提高系統的可靠性和穩定性。

-

上拉電阻

+關注

關注

5文章

363瀏覽量

30732 -

下拉電阻

+關注

關注

4文章

147瀏覽量

20594 -

GND

+關注

關注

2文章

540瀏覽量

38900

發布評論請先 登錄

相關推薦

MAX13487接了終端電阻120Ω時,下降沿有很長的毛刺,是什么原因導致的?

當LMK00725的輸入為LVPECL電平時,由于芯片輸入管腳內部存在51KOhm上下拉,在芯片外部是否還需要增加上下拉偏置電阻呢?

【RS-485總線】詳解RS-485上下拉電阻的選擇

Lattice MachXO3 Family默認IO上下拉配置

請問ESP32-WROOM-32某些管腳上下拉是不是固定的呢?

STM32F103XX引腳拉低時,什么時候加下拉電阻,什么時候不加呢?

上拉電阻和下拉電阻的用處和區別介紹

下拉電阻的作用有哪些

上拉電阻和下拉電阻是什么

電阻是如何實現上下拉功能的呢?

電阻是如何實現上下拉功能的呢?

評論