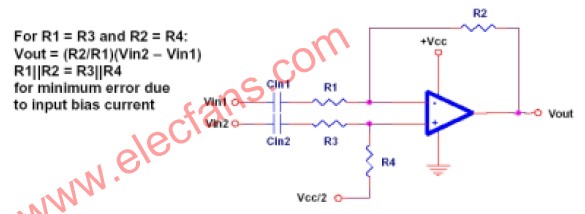

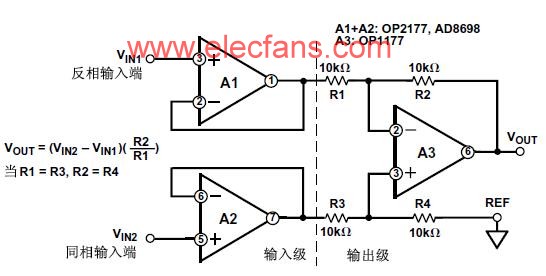

減法電路是基本集成運放電路的一種,算術(shù)運算電路主要包括數(shù)字加法器電路、數(shù)字減法器電路、數(shù)字乘法器電路和數(shù)字除法器電路。

由于基本的算術(shù)運算加法、減法、乘法、除法最終都可歸結(jié)為加法或減法運算,因此,在算術(shù)運算電路中數(shù)字加法器電路與數(shù)字減法器電路是最基礎(chǔ)的電路。一般是由集成運放外加反饋網(wǎng)絡(luò)所構(gòu)成的運算電路來實現(xiàn)。

Verilog設(shè)計

設(shè)計一個16比特的減法器

(1)基于全減器設(shè)計“行波借位減法器”,基礎(chǔ)的全減器模塊

行波借位減法器

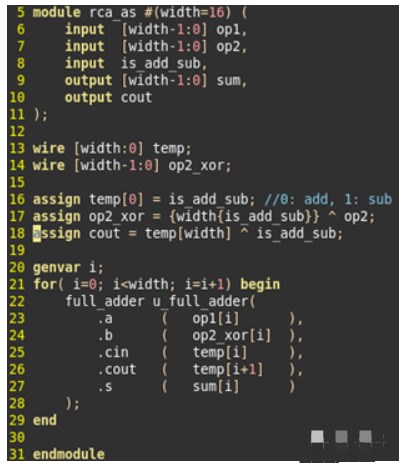

(2)根據(jù)行波進位加法器,通過控制信號,使其同時具有加法和減法的功能,注意進位。

加減法器

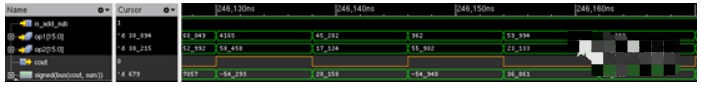

測試波形

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110390 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30229 -

減法電路

+關(guān)注

關(guān)注

0文章

15瀏覽量

8067 -

減法器

+關(guān)注

關(guān)注

1文章

26瀏覽量

16878

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)字電路中加法器和減法器邏輯圖分析

菜鳥請教一個運放減法器的問題

減法器的4個電阻到底是什么關(guān)系呢?

哪一個是減法器?負(fù)反饋在減法器電路中的原理?

設(shè)計一個基于RS觸發(fā)器余3碼十進制減法器

本的二進制加法/減法器,本的二進制加法/減法器原理

減法器電路

如何設(shè)計一個16比特的減法器呢?

如何設(shè)計一個16比特的減法器呢?

評論