近日,浙江微鈦先進封測研發基地項目開工。

據悉,項目建設地點位于經濟開發區輝埠片區,總投資15億元。項目總用地面積110畝,總建筑面積約10.5萬平方米,建設內容主要包括新建廠房及辦公樓等,購置數控機床、臥式加工中心、立式加工中心等設備。建設單位為浙江微鈦集成電路有限公司,建設工期為2024—2026年,計劃2024年3月開工。

項目投用后,可形成年封裝/測試3.96億顆FCCSP10x10芯片、0.198億FCBGA33x33芯片及1.342億WBBGA芯片的生產能力,年銷售收入38億元,年可貢獻稅收約為3.5億元以上。本文來源:衢州發布

FCCSP封裝 是什么?

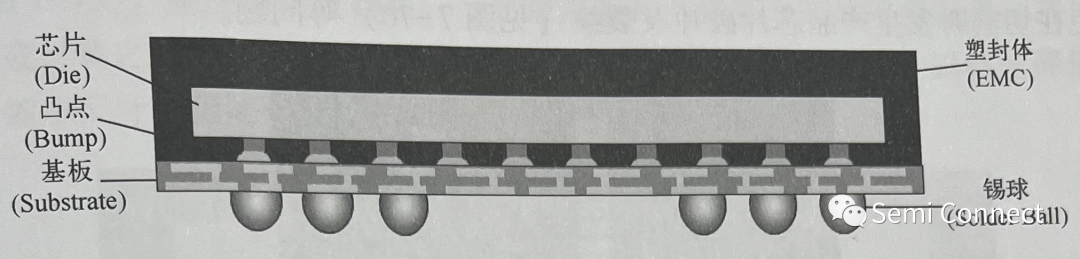

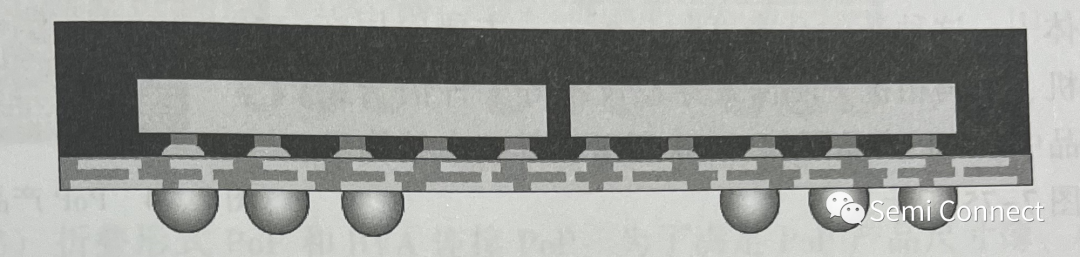

FC-CSP 是芯片級尺寸封裝(CSP)形式中的一種。根據J-STD-012 標準的定義口,CSP 是指封裝體尺寸不超過裸芯片 1.2倍的一種封裝形式,它通過凸塊與基板倒裝焊方式實現芯片與基板的電氣互連,且芯片面朝下,芯片焊區與基板焊區直接互連。相比于 WB 和TAB 鍵合方法,FC-CSP 中的半導體芯片與基板的間距更小,信號損失減小,I/O密度高,更適合大規模集成電路 (LSI)、超大規模集成電路(VLSI)和專用集成電路(ASIC)芯片使用。FC-CSP 的基本封裝結構如圖所示。

作為一種先進的封裝技術,FC-CSP 主要具有如下技術特點。

(1)封裝尺寸較小:FC-CSP 的封裝面積不到 QPP (0.5mm 節距)的1/10,只有BCA 封裝的 1/3~1/10;特別是運用銅杜凸塊封裝,可以進一步滅小凸塊間距,從而減小封裝面積。

(2)引腳數(I0)更多:在相同尺寸的芯片封裝中,相對于傳統的打線封裝,FC-CSP 可容納更多的引腳數。

(3) 電性能更優:由于芯片與封裝外殼布線之間的互連線更短,寄生參數更小,信號干擾較小,且信號傳輸延遲時問短,因此具有更小的電阻率,以區更快的信號傳輸速度。

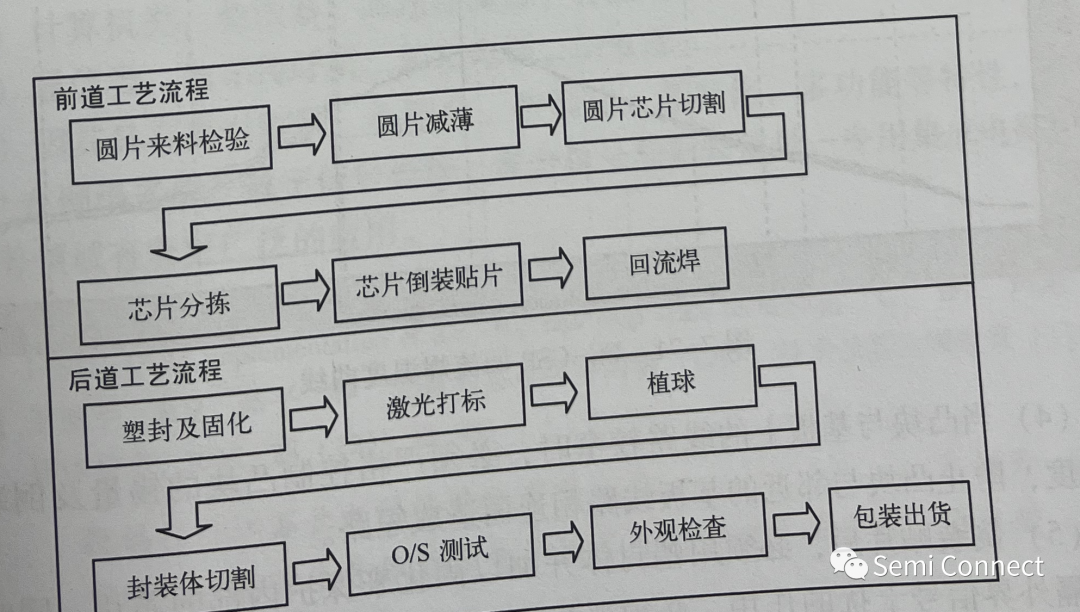

(4) 實現多種不同功能芯片及器件的一體式封裝。以單芯片 (Single Die) FC-CSP 產品為例,FC-CSP 封裝工藝流程如圖所示。

FC-CSP 的關鍵技術如下所述、

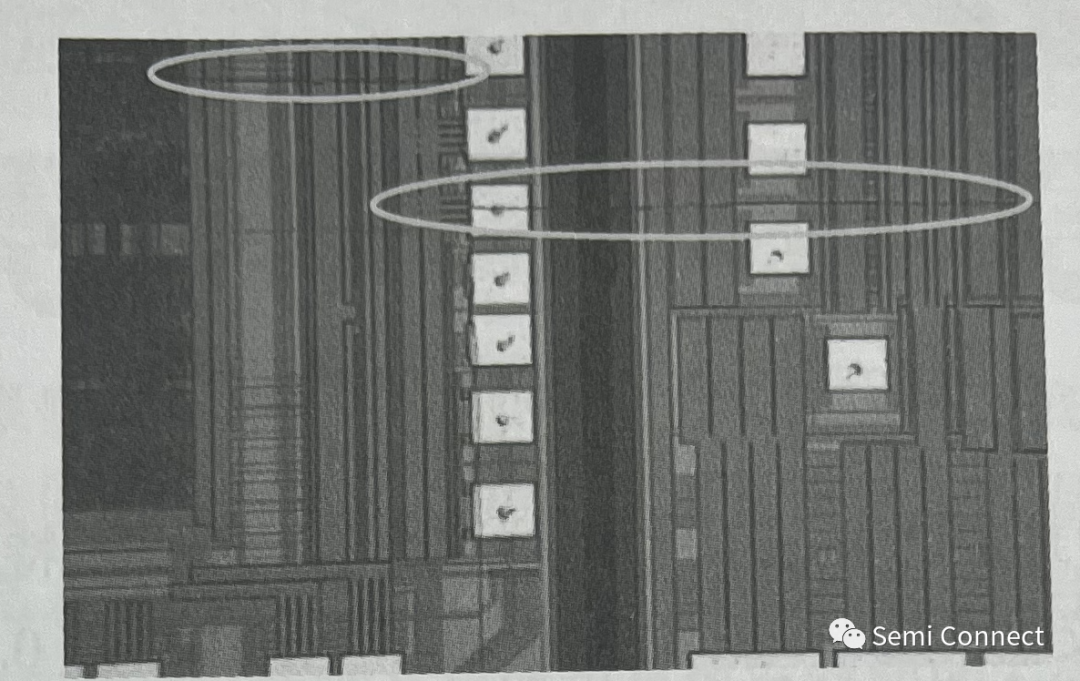

(1)FC-CSP 對于封裝的厚度有較高的要求,因此在圓片減薄時,需要嚴格控制好最終的厚度(在目標值士151μm 以內)。另外,還要控制好工藝參數避免在切割時發生產品芯片破片及裂紋如圖等問題

(2)由于采用回流焊連接芯片凸塊及基板的線路,所以需要防止回流過程中的斷路,以及過小間距時的短路問題。特別是當芯片與基板的面積比較大時,由于芯片與基板材料的熱收縮比有所不同,可能造成高溫回流焊時的翹曲不致,從而產生一定的應力,導致凸塊與基板連接處發生斷裂。

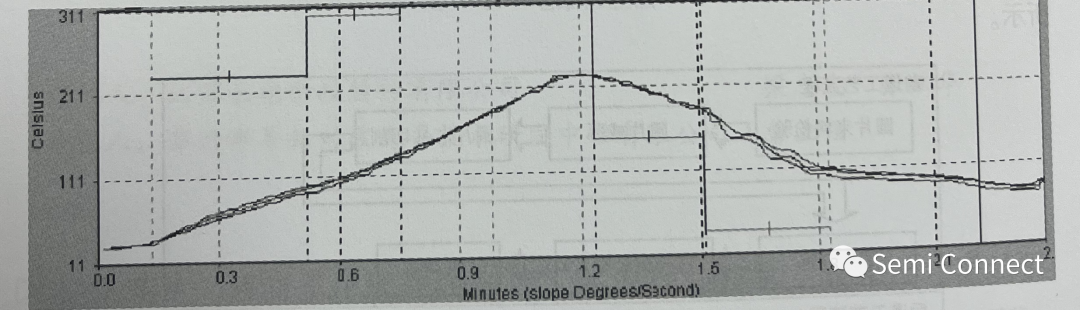

(3)必須嚴格控制回流焊的降溫速率,避免凸塊與基板結合處及圓片內低K材料的斷裂。通常,降溫到 150攝氏度以下時,應控制降溫速率在4攝氏度/s以內,如圖所示。

(4)當凸塊與基板上的線路較窄時,必須嚴格控制凸塊的錫量及倒裝對位的精度,防止凸塊與鄰近的基板線路相連而造成短路。

(5)倒裝貼片后,必須用塑封體并加以固化來保護內部的芯片,同時也起到阻隔外界信號干擾的作用。必須嚴格控制塑封過程中的固化時間及溫度,避免塑封體與芯片分離,以及塑封后產品翹曲問題等的發生。

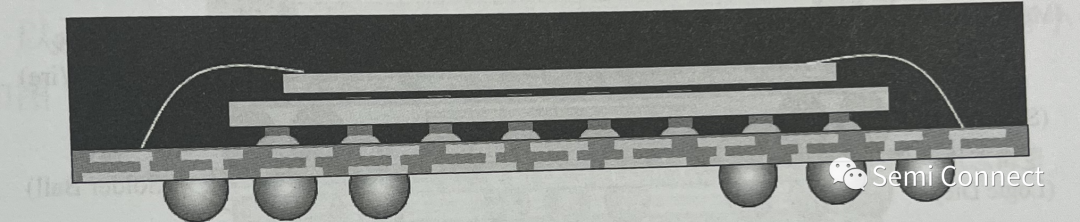

結合工藝和目前各 IC 制造廠 商的研發情況來看,FC-CSP 的主要結構類型有單芯片 (Single Die) FC-CSP、多芯片平置 ( Muli-Chip Side byside) FC-CSP(見圖1)和疊層芯片混聯 (Stacked-Die Hybid) FC-CSP(見圖2)。疊層封裝是指在一個芯腔或基片上將多個芯片堆看起來,芯片與芯片或封裝之問實現連接。疊層封裝主要應用在手機處理器中,以此來降低功耗、縮小尺寸,提高封裝的集成度和性能。

隨著 FC-CSP 技術的迅速推廣,其應用也越來越廣泛,主要應用領域如下

所述

(1)消費類電子產品:手機、便攜式攝像機、數碼電子產品、DVD、無線產品等。

(2)計算機類:穩壓器、高速存儲器、智能卡、外設等。

(3)通信類:數宇傳呼機、移動電話、CPS 等。

(4)因其具有高引腳數、小型化、微型化、薄型化、多功能等特性,使得FC-CSP 在網絡通信、數宇信號處理、混合信號和射頻信號、專用集成電路、微控制器等領域有著更廣泛的應用。

審核編輯:劉清

-

集成電路

+關注

關注

5389文章

11576瀏覽量

362378 -

CSP封裝

+關注

關注

0文章

17瀏覽量

11595 -

信號傳輸

+關注

關注

4文章

430瀏覽量

20218 -

ASIC芯片

+關注

關注

2文章

92瀏覽量

23810

原文標題:總投資15億!年產3.96億顆!浙江再添先進封測項目

文章出處:【微信號:today_semicon,微信公眾號:今日半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

年產3.96億顆!浙江再添先進封測項目

年產3.96億顆!浙江再添先進封測項目

評論