wafer--晶圓

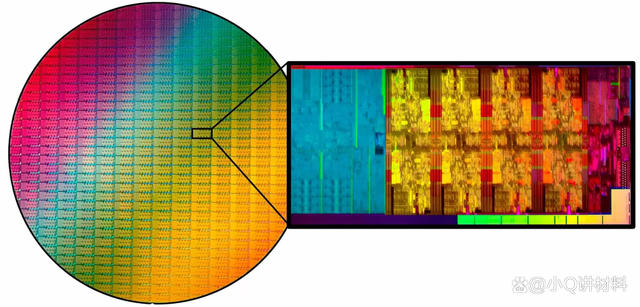

wafer即為圖片所示的晶圓,由純硅(Si)構(gòu)成。一般分為6英寸、8英寸、12英寸規(guī)格不等,晶片就是基于這個(gè)wafer上生產(chǎn)出來(lái)的。晶圓是指硅半導(dǎo)體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結(jié)構(gòu),而成為有特定電性功能的集成電路產(chǎn)品。

die--晶粒Wafer上的一個(gè)小塊,就是一個(gè)晶片晶圓體,學(xué)名die,封裝后就成為一個(gè)顆粒。晶粒是組成多晶體的外形不規(guī)則的小晶體,而每個(gè)晶粒有時(shí)又有若干個(gè)位向稍有差異的亞晶粒所組成。晶粒的平均直徑通常在0.015~0.25mm范圍內(nèi),而亞晶粒的平均直徑通常為0.001mm數(shù)量級(jí)。

chip--芯片一片載有Nand Flash晶圓的wafer,wafer首先經(jīng)過(guò)切割,然后測(cè)試,將完好的、穩(wěn)定的、足容量的die取下,封裝形成日常所見(jiàn)的Nand Flash芯片(chip)。芯片一般主要含義是作為一種載體使用,并且集成電路經(jīng)過(guò)很多道復(fù)雜的設(shè)計(jì)工序之后所產(chǎn)生的一種結(jié)果。

wafer、chip、die的關(guān)系好比下面這張圖

什么是芯片?

通俗點(diǎn)來(lái)說(shuō),芯片就是把一個(gè)電路所需的晶體管和其他器件制作在一塊半導(dǎo)體上。通常情況下半導(dǎo)體所應(yīng)用到的材料就是單晶硅(Monocrystalline Silicon),如果要制造用于處理元宇宙數(shù)據(jù)的高性能芯片,那么單晶硅的純度需要達(dá)到99.99999999999%以上。如圖所示,芯片最初的材料便是這一塊一塊的單晶硅硅錠了。

生產(chǎn)芯片的原料——單晶硅硅錠

我們不可能在這么大的硅錠上制作芯片,于是晶圓廠將硅錠按照要求裁切成一個(gè)一個(gè)的圓片,圖中那個(gè)大大的圓片便是我們說(shuō)的晶圓(Wafer),而放大的部分里面包含著復(fù)雜的線路圖,這些獨(dú)立的結(jié)構(gòu)單元稱為chips,在某些場(chǎng)合下,芯片也指代chips。

晶圓以及圓上的chips

芯片的制造工藝

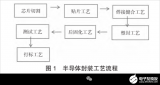

在半導(dǎo)體界有這么一種說(shuō)法,“如果將制造核彈的難度設(shè)定為1,那么制造芯片的難度可能是100,制造高性能芯片的難度可能是10000。”為什么這么說(shuō)呢?我們首先來(lái)看一張制造芯片的流程簡(jiǎn)圖:

是不是已經(jīng)被嚇到了?注意,這還是一張簡(jiǎn)圖,實(shí)際上芯片制造分為前道工藝和后道工藝,每一段工藝又分為幾十甚至上百道工序,中間只要一個(gè)環(huán)節(jié)走不通,那都是半途而廢。最后,為了讓大家能看得清楚一些,筆者將上述的圖再簡(jiǎn)化如下所示:

芯片制造簡(jiǎn)圖

通過(guò)上述的圖片,我們已經(jīng)初步了解了制造一枚芯片的流程,芯片制造的困難不僅僅包括設(shè)備,同時(shí)也包括材料方面的問(wèn)題。接下來(lái),筆者分別介紹芯片制造中所用到的重要材料。

單晶硅,制備芯片結(jié)構(gòu)的襯底

沒(méi)有高純度的單晶硅,就不要提芯片,更不用說(shuō)構(gòu)建一個(gè)元宇宙的虛擬世界了。作為地球上第二豐度的元素,硅廣泛地存在于自然界當(dāng)中。它成本低廉,溫度穩(wěn)定性好,穿透電流低,如此優(yōu)異的性能使它代替鍺,成為了半導(dǎo)體的主流材料。

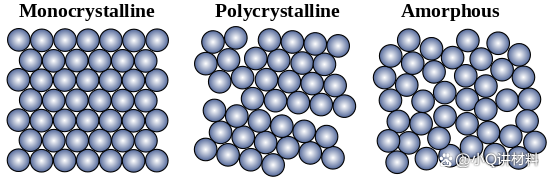

單質(zhì)硅主要有單晶、多晶以及非晶硅三類形態(tài),后兩種形態(tài)缺陷太多,若用于芯片制造,在加工過(guò)程中會(huì)引起基材的電學(xué)以及力學(xué)性能變差,因此只能用高純的單晶硅作為芯片的基元材料。

硅單質(zhì)的三種形態(tài)

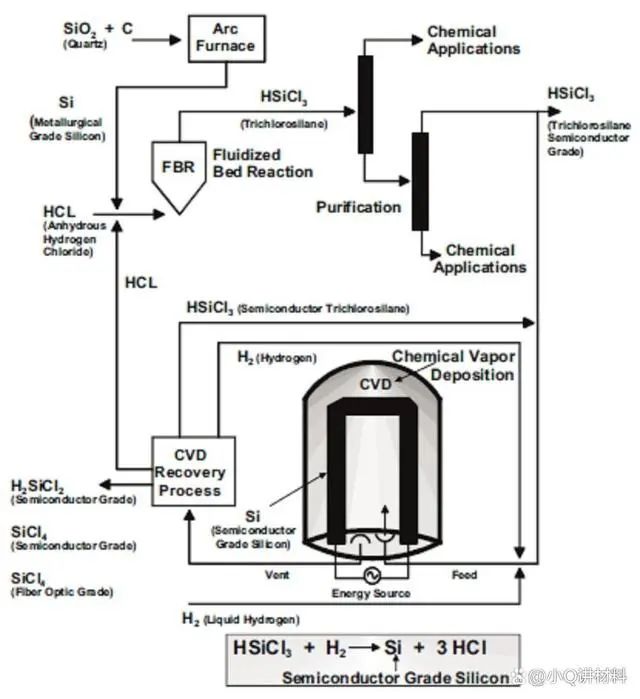

然而自然界中別說(shuō)單晶硅,就連硅單質(zhì)也是不存在的,硅元素主要以硅酸鹽以及硅的氧化物形式存在,想從原料中獲取單晶硅并不是一個(gè)簡(jiǎn)單的過(guò)程,要經(jīng)過(guò)西門子法提純以及CZ法制備單晶硅兩大步驟,這兩大步驟具體包括:二氧化硅原料→金屬硅→HCl提純→氫氣還原→多晶硅→熔融→拉制單晶硅→切片。

首先,利用焦炭,在1500℃的條件下,將二氧化硅原料還原成金屬硅,此時(shí)的金屬硅純度僅僅為97%,具有雜質(zhì);隨后,利用氯化氫(HCl)在300℃的低溫下將金屬硅變?yōu)?span style="color:rgb(230,46,46);">三氯硅烷,而氯化氫也會(huì)將金屬硅中的雜質(zhì)溶解,由于雜質(zhì)和三氯硅烷蒸汽壓較大的差異,此時(shí),雜質(zhì)的氯化物會(huì)受熱蒸發(fā),硅的純度得到進(jìn)一步提高。

接下來(lái),利用高純度氫氣將高純度的三氯硅烷通入爐中,在1100℃的高溫下,爐子內(nèi)部的硅芯棒上會(huì)逐漸長(zhǎng)出多晶硅晶體,此時(shí)多晶硅的純度可達(dá)99.999999999%。

西門子法制備高純多晶硅

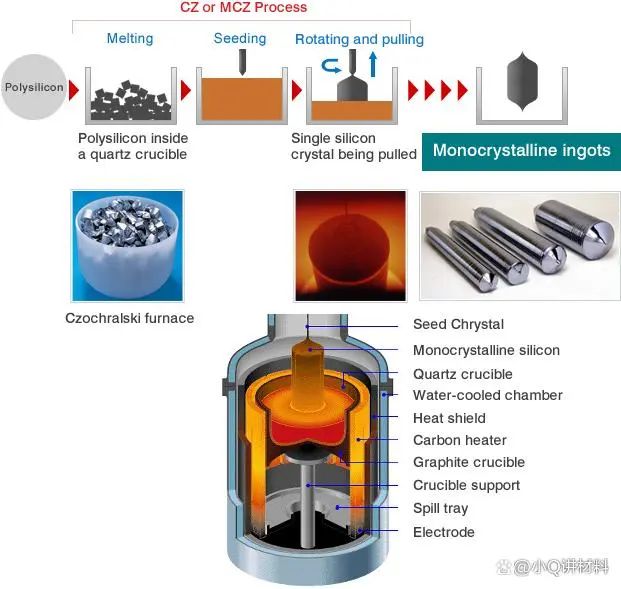

最后一步便是利用多晶硅制備單晶硅,首先將多晶硅加熱熔化,隨后加入單晶硅的籽晶(Seed),觸碰多晶硅的熔體,此時(shí)界面處的硅便會(huì)沿著同一個(gè)晶面方向生長(zhǎng),通過(guò)調(diào)控合適的工藝參數(shù),便可得到硅單晶棒。

CZ法制備單晶硅流程

單晶硅硅棒經(jīng)過(guò)打磨,拋光,外延,切片等工藝,就形成晶圓了。別急,這只是做芯片的第一步。

光刻膠,轉(zhuǎn)印芯片電路的媒介

當(dāng)制備好的晶圓經(jīng)過(guò)氧化處理后,便進(jìn)入了芯片前道工藝的光刻工序,大家應(yīng)該都知道光刻機(jī),如果將光刻機(jī)比作芯片行業(yè)的引擎,那么光刻膠就是助推引擎的燃料。

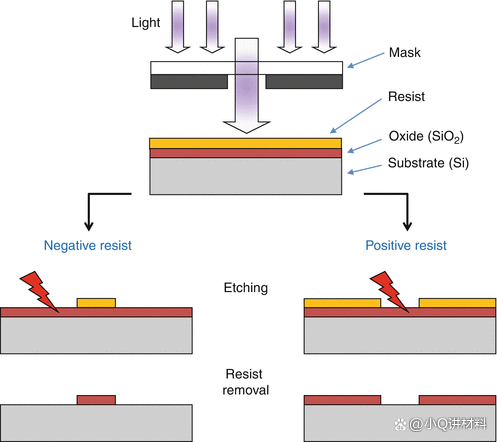

光刻流程簡(jiǎn)圖

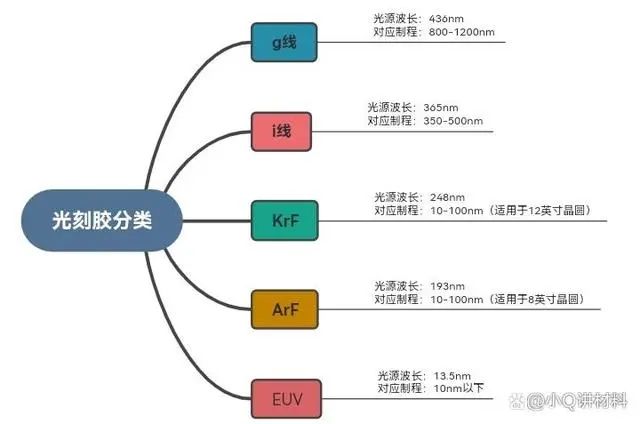

光刻膠就是圖中橙色的部分,也有人將其稱為光阻劑。光刻膠分為正膠和負(fù)膠,正膠經(jīng)過(guò)曝光后會(huì)溶解于顯影液,負(fù)膠則是相反的。按照曝光光源的波長(zhǎng)分類,光刻膠分為g線,i線,KrF,ArF以及EUV光刻膠,由左到右,光刻膠對(duì)應(yīng)的曝光波長(zhǎng)逐漸變短,先進(jìn)的EUV光刻膠對(duì)應(yīng)曝光波長(zhǎng)只有13.5nm,可用于10nm以下的芯片制程,但目前EUV光刻機(jī)只有荷蘭ASML能制造。

光刻膠分類

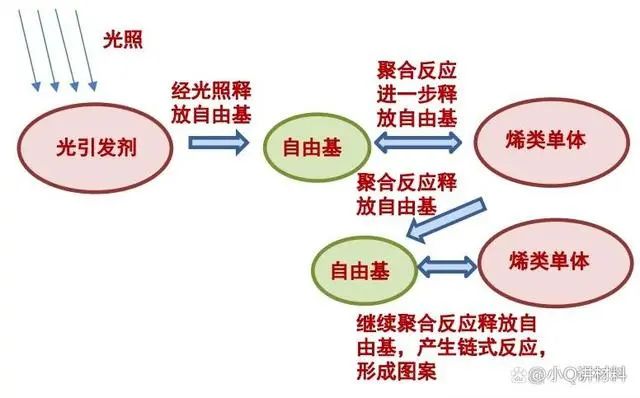

光刻膠的組分一直是國(guó)外廠商的機(jī)密,很難通過(guò)逆向解析的手段還原。一般而言,光刻膠的組分包括光引發(fā)劑,樹(shù)脂基體,單體以及助劑。當(dāng)光刻膠經(jīng)過(guò)紫外光照射后,發(fā)生一系列的物理化學(xué)變化,電路圖形就從掩膜版上轉(zhuǎn)移到光刻膠上面,經(jīng)過(guò)刻蝕后,晶圓片上就形成了對(duì)應(yīng)的圖案。

光刻膠反應(yīng)機(jī)理簡(jiǎn)圖

我國(guó)目前28nm工藝制程使用的光刻膠為KrF型號(hào),目前正在積極開(kāi)發(fā)ArF型光刻膠,而更為高端的產(chǎn)品已經(jīng)被美國(guó)與日本所壟斷。

成膜,分隔芯片結(jié)構(gòu)的骨架

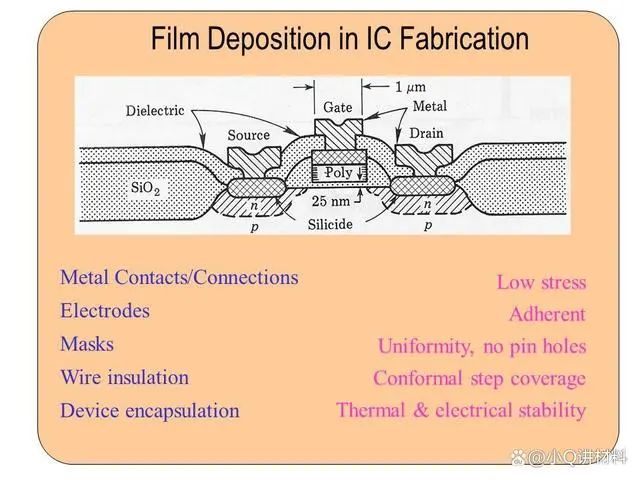

經(jīng)過(guò)刻蝕,我們已經(jīng)得到了芯片的基本平面形貌,為了防止各個(gè)器件之間的干擾,同時(shí)賦予芯片三維結(jié)構(gòu),我們就需要薄膜(<1μm)沉積工藝。

芯片薄膜沉積工藝

薄膜沉積工藝分為化學(xué)氣相沉積(CVD)以及物理氣相沉積(PVD)兩種方式。

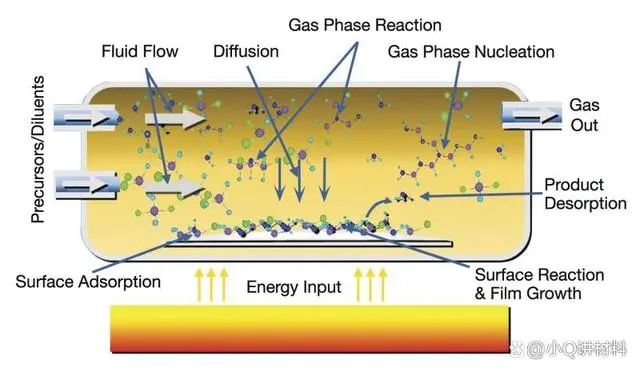

典型的CVD工藝是將晶圓(基底)暴露在一種或多種不同的前驅(qū)物下,在基底表面發(fā)生化學(xué)反應(yīng)或化學(xué)分解來(lái)產(chǎn)生所需的沉積薄膜。CVD 的基本流程如圖所示:

CVD基本流程

上述的流程包括反應(yīng)物傳輸,先驅(qū)體反應(yīng),氣體擴(kuò)散,襯底吸附,CVD主要用在芯片的氮化層成膜。而PVD的方式包括蒸鍍與濺射,主要用于芯片的金屬層,目前多用離子濺射的方式成膜。離子濺射的基本原理是通過(guò)氣體等離子轟擊靶材,將靶材原子“打”出來(lái),并使它沉積在襯底上成膜。

PVD基本流程

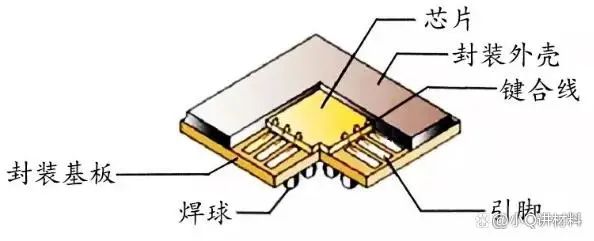

封裝,連接芯片電路的外衣

封裝屬于后道工藝,但也是至關(guān)重要的一步。芯片封裝是半導(dǎo)體開(kāi)發(fā)的最后一個(gè)階段,不僅僅是為了保護(hù)芯片的內(nèi)部結(jié)構(gòu)和提高芯片的性能,更是為芯片內(nèi)部結(jié)構(gòu)與外部電路建立了一道溝通的橋梁。

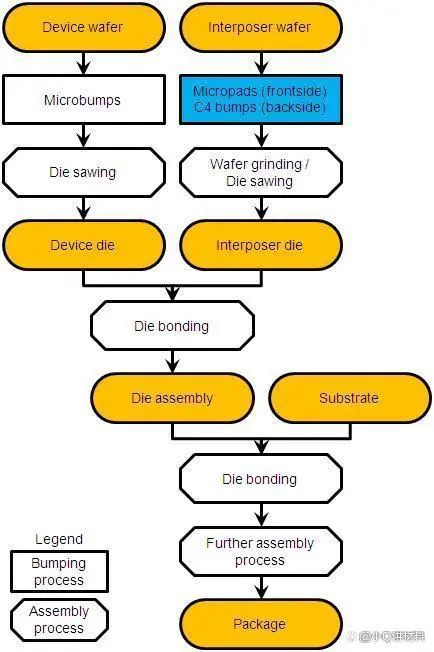

2.5D芯片封裝工藝

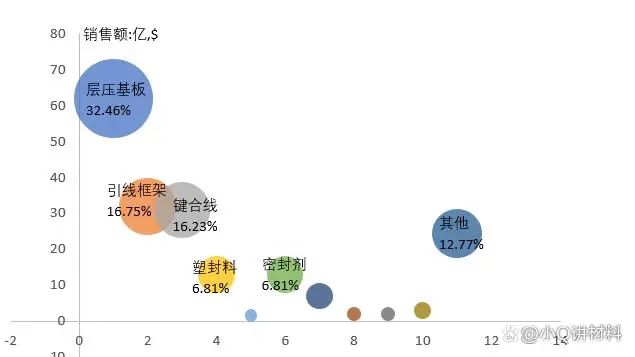

芯片的封裝材料主要包括封裝基板、引線框架、鍵合絲、塑封料等四類材料。這四類材料的市場(chǎng)份額在芯片封裝材料里占70%以上。

封裝材料市場(chǎng)占有率

封裝基板是芯片的內(nèi)外承載和保護(hù)結(jié)構(gòu)。對(duì)于高端芯片,會(huì)選擇環(huán)氧樹(shù)脂,聚苯醚樹(shù)脂,聚酰亞胺樹(shù)脂作為基板材料,相比于金屬基板和陶瓷基板,有機(jī)基板具有密度小,生產(chǎn)成本低以及加工簡(jiǎn)單的優(yōu)勢(shì)。而引線框架則是連接內(nèi)外電路的媒介,它需要較高的導(dǎo)電導(dǎo)熱性能,一定的機(jī)械強(qiáng)度,良好的熱匹配性能,同時(shí)環(huán)境穩(wěn)定性要好。一般采用銅基引線框架材料。鍵合絲是芯片內(nèi)部與引線框架的內(nèi)引線,對(duì)于高端產(chǎn)品而言,要求化學(xué)穩(wěn)定性和導(dǎo)電率更高,因此高端芯片一般采用鍵合金絲作為鍵合材料,但是缺點(diǎn)是成本過(guò)高,因此在一些較為低端的產(chǎn)品,一般用鍵合銀絲以及鍵合銅絲。塑封料則是對(duì)芯片和引線架構(gòu)起保護(hù)作用。塑封料有金屬,陶瓷,高分子塑封料三種方式。相比于前兩者,高分子環(huán)氧塑封具有低成本,小體積,低密度等優(yōu)點(diǎn),目前絕大多數(shù)的集成電路都采用高分子環(huán)氧塑封。

封裝材料示意圖

展望

在經(jīng)過(guò)封裝測(cè)試之后的其它工藝,一枚小小的芯片就這么誕生了。強(qiáng)大的算力是支持元宇宙運(yùn)行的基礎(chǔ),根據(jù)半導(dǎo)體的摩爾定律:

集成電路上可以容納的晶體管數(shù)目在大約每經(jīng)過(guò)18個(gè)月到24個(gè)月便會(huì)增加一倍。換言之,處理器的性能大約每?jī)赡攴槐叮瑫r(shí)價(jià)格下降為之前的一半。

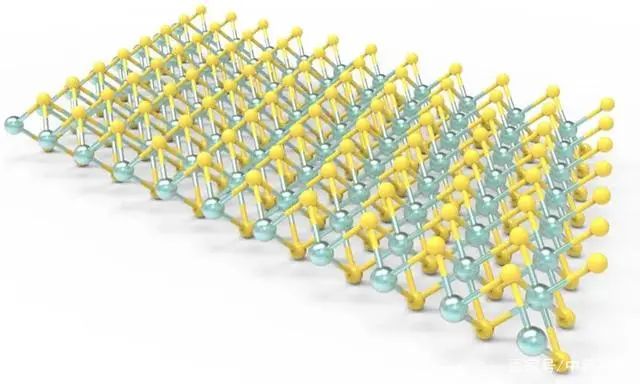

但是隨著芯片制成的不斷縮小,甚至到現(xiàn)在網(wǎng)傳的1.4nm,摩爾定律的適用性在面臨挑戰(zhàn)。那么,我們不禁要問(wèn),能否在原材料上有所突破呢?答案是肯定的,科學(xué)家們?cè)?jīng)說(shuō)石墨烯是下一代芯片材料,但是石墨烯的量產(chǎn)與提純又是一大問(wèn)題。近期,科學(xué)家們發(fā)現(xiàn)二維二硫化鉬這種新型半導(dǎo)體:

二硫化鉬結(jié)構(gòu)圖

相比于單晶硅,它具有的優(yōu)勢(shì):

- 沒(méi)有單晶硅表面的“懸掛鍵”,性能比單晶硅更穩(wěn)定;

- 很薄,單層的二硫化鉬只有6.5埃的厚度,比現(xiàn)在的3nm制程小了5倍,芯片的制程可以進(jìn)一步縮小,獲得更高的算力;

- 若能批產(chǎn),可以減少芯片的制作流程。

但是,需要說(shuō)明的是,作為一種二維材料,它與石墨烯一樣很難穩(wěn)定批產(chǎn),這就需要材料學(xué)家進(jìn)一步去探索新的制備工藝和新的合成方法了,希望那一天能夠早日到來(lái)。

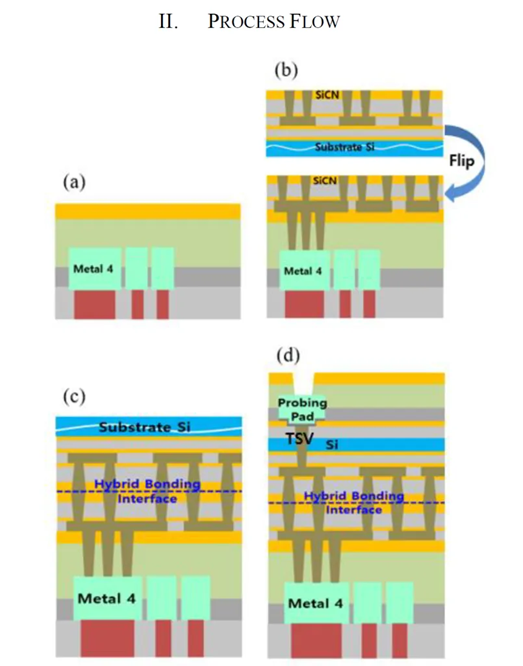

先進(jìn)封裝開(kāi)始嶄露頭角,以蘋果和臺(tái)積電為代表,開(kāi)啟了一場(chǎng)新的革命,其主要分為兩大類,一種是基于XY平面延伸的先進(jìn)封裝技術(shù),主要通過(guò)RDL進(jìn)行信號(hào)的延伸和互連;第二種則是基于Z軸延伸的先進(jìn)封裝技術(shù),主要通過(guò)TSV進(jìn)行信號(hào)延伸和互連。前者為2D先進(jìn)封裝,代表為FOWLP和FOPLP等,而后者即為3D封裝,代表為SoIC和Foveros等,目前還有兼具兩種封裝特點(diǎn)的2.5D封裝,代表為CoWoS和EMIB等。

目前3D 封裝大多應(yīng)用于提升HPC 芯片的性能,常見(jiàn)于HBM與CPU、GPU、FPGA、或NPU 等處理器彼此間的芯片整合。如臺(tái)積電提出的SoIC 整合封裝架構(gòu),其主要利用W2W 及C2W 的混合鍵合技術(shù),實(shí)現(xiàn)10um 以下I/O 節(jié)點(diǎn)互連、減少寄生效應(yīng)、并使芯片更薄等優(yōu)勢(shì)。

三星則于2020 年推出名為X-Cube 的3D 封裝技術(shù),將4 顆SRAM 堆疊在邏輯核心運(yùn)算芯片上,并通過(guò)TSV 結(jié)構(gòu)進(jìn)行連接。

英特爾于2018 年底推出名為Foveros的3D 邏輯芯片封裝技術(shù),通過(guò)TSV 與Micro Bumps 將不同芯片以Face-to-Face 方式堆疊連接,目前Foveros 技術(shù)能使凸點(diǎn)間距達(dá)到50um,未來(lái)有望縮減到10um,讓凸點(diǎn)數(shù)量達(dá)到每平方毫米10,000 個(gè)。

在這幾種封裝方式里,其主要目的都是將不同類型的芯片,通過(guò)3D立體堆疊的形式整合在一起,從而實(shí)現(xiàn)高性能、小體積、低耗電等目標(biāo)優(yōu)勢(shì),也即異構(gòu)集成。

混合鍵合革命

封裝中最早采用的引線鍵合(Wire Bonding),由于其接點(diǎn)僅能以周列形式排列在芯片周圍,接點(diǎn)的I/O 數(shù)量有限,而IBM 提出的倒裝接合(Flip Chip Bonding),利用焊錫微凸塊(Solder Bump)當(dāng)作接點(diǎn)將芯片與芯片接合在一起,接點(diǎn)為陣列式排列,可以分布于整個(gè)芯片上,可以提高接點(diǎn)I/O 數(shù)量,不過(guò)這項(xiàng)技術(shù)在 50μm 或 40μm 的間距時(shí)表現(xiàn)尚可,人們很快發(fā)現(xiàn),這種方式由于熱膨脹不匹配,會(huì)出現(xiàn)翹曲和芯片移位。

事實(shí)上,微凸塊一旦做到 10 微米以下的間距時(shí),暴露的問(wèn)題就愈發(fā)增多,當(dāng)凸塊結(jié)構(gòu)較大時(shí),電鍍微凸塊高度的極小不均勻性或回流焊過(guò)程中的變化可能可以忽略不計(jì),但對(duì)于細(xì)間距微凸塊,這些微小的變化可能會(huì)導(dǎo)致接合處形成不良,并影響電氣良率,最終導(dǎo)致晶粒和封裝出現(xiàn)缺陷。

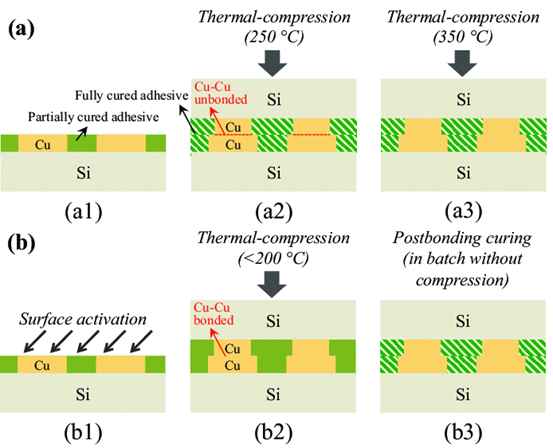

銅─銅混合鍵合(Cu-Cu Hybrid Bonding)技術(shù)應(yīng)運(yùn)而生,將金屬接點(diǎn)鑲嵌在介電材料(Dielectric Material)之間,并同時(shí)利用熱處理接合兩種材料,利用銅金屬在固態(tài)時(shí)的原子擴(kuò)散來(lái)達(dá)到接合,故不會(huì)有Bridging 問(wèn)題。銅制程是半導(dǎo)體業(yè)非常成熟的技術(shù),銅─銅接點(diǎn)的間距可以微縮到10μm以下,因此在1×1cm2 的晶片內(nèi),能夠制作出超過(guò)一百萬(wàn)的接點(diǎn),因此金屬的直接接合變得非常重要。

混合鍵合此前在業(yè)界通常被稱為DBI(Direct Bond Interconnect,直接鍵合),20世紀(jì)80年代中期,Paul Enquist,Q.Y. Tong和Gill Fountain在三角研究所(RTI)的實(shí)驗(yàn)室首次提出了這一技術(shù),2000年,三人成立了Ziptronix公司,并于2005年推出了一種稱為低溫直接鍵合互連 (DBI) 的技術(shù),這是混合鍵合的第一個(gè)版本。

它驗(yàn)證了低溫直接鍵合(Direct Bond Interconnection, DBI)的可行性,首先準(zhǔn)備好晶片具有SiO 2(介電材料)與銅(接點(diǎn)金屬),此時(shí)銅部分將會(huì)有點(diǎn)略低于介電材料厚度,利用電漿(Plasma)做表面活化處理,將晶片面對(duì)面在室溫下進(jìn)行對(duì)位接合,由于凡德瓦力作用已具有一定的接合強(qiáng)度,接著在100℃ 下持溫讓SiO 2與SiO 2之間進(jìn)行縮合反應(yīng),形成強(qiáng)力共價(jià)鍵提高接合強(qiáng)度 。接著再將溫度提高到300℃ 至400℃ 持溫,此時(shí)由于銅金屬的熱膨脹系數(shù)較SiO 2來(lái)的大,銅表面將會(huì)碰觸在一起,并自然受到一壓應(yīng)力,促使銅接點(diǎn)進(jìn)行擴(kuò)散接合。

有研究學(xué)者指出,想要達(dá)到低溫鍵合,介電材料層與金屬層在經(jīng)過(guò)化學(xué)拋光研磨后造成的高度差異將會(huì)是關(guān)鍵,研磨液與研磨參數(shù)的選擇是導(dǎo)致不同厚度的主因,厚度差越小,便可于較低溫度使銅表面接觸并開(kāi)始進(jìn)行接合。

混合鍵合與倒裝接合比,它帶來(lái)了三大新優(yōu)勢(shì),第一為可以達(dá)到超細(xì)間距與超小接點(diǎn)尺寸,實(shí)現(xiàn)更高I/O 數(shù)量;第二,由介電材料接合取代底部填充劑,進(jìn)一步節(jié)省填充成本;第三,倒裝技術(shù)會(huì)讓芯片與基板或芯片片間存在約10 至30 μm的厚度,而混合鍵合幾乎沒(méi)有厚度,在多層堆疊的情況下可以大幅減少總體厚度。

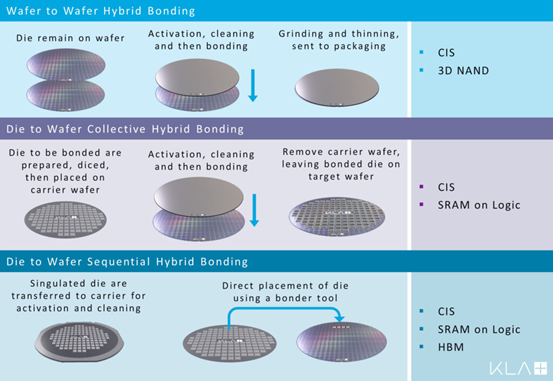

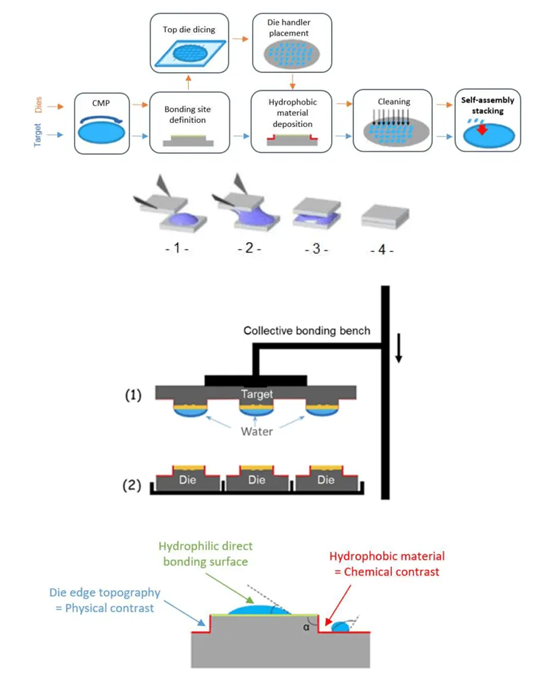

目前銅─銅混合鍵合主要分為了三種方式,分別為最常見(jiàn)的晶圓到晶圓(W2W)工藝,芯片到晶圓(D2W)和芯片到晶圓(C2W)工藝,后兩種工藝目前還在研發(fā)當(dāng)中。

其中,W2W 雖然已經(jīng)實(shí)現(xiàn)量產(chǎn),但它對(duì)于上下芯片的大小限制須為一樣大小,否則將有區(qū)域浪費(fèi);D2W是將切割好的Die用臨時(shí)鍵合的方式粘到晶圓上,然后整片地和另一片產(chǎn)品晶圓整片鍵合再解鍵,這項(xiàng)技術(shù)容易累計(jì)誤差,且成本高,對(duì)Die的厚度變化范圍也有較高要求;C2W將切好的Die分別放置晶圓的對(duì)應(yīng)位置上,位置精度雖然提高且厚度變化要求不在嚴(yán)苛,但顆粒控制也是影響它繼續(xù)普及的問(wèn)題。

2015年,發(fā)明混合鍵合技術(shù)的Ziptronix被Xperi收購(gòu),2019年,Xperi 完成了混合鍵合技術(shù)的最終專利布局,而在此之前,這項(xiàng)技術(shù)已經(jīng)授權(quán)給了包括索尼在內(nèi)的多家廠商。

從20世紀(jì)80年代的構(gòu)想,到2005年的初步驗(yàn)證,再到2015年之后的技術(shù)授權(quán),混合鍵合歷經(jīng)三十余年,終于為先進(jìn)封裝鋪平了道路,解決了芯片廠商對(duì)封裝未來(lái)的最大疑慮,此后混合鍵合領(lǐng)域更是呈現(xiàn)出了一篇千帆競(jìng)逐的景象。

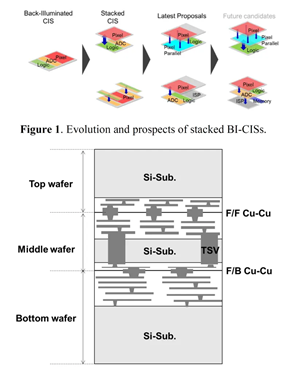

群雄決戰(zhàn)封裝

2016 年,索尼首先將混合鍵合技術(shù)應(yīng)用在三星Galaxy S7 的背照式CMOS 影像傳感器(Backside-illuminated CMOS Image Sensor, BI-CIS)中,大幅提高了鏡頭解析度。目前索尼每年出貨數(shù)百萬(wàn)個(gè)采用 6.3 微米間距混合鍵合技術(shù)的 CMOS 圖像傳感器,并堆疊了 3 個(gè)芯片,而其他公司采用的間距密度要低得多,出貨量也要小得多。

作為這項(xiàng)技術(shù)的急先鋒,索尼在2022年展示了 1 微米間距的面對(duì)面混合鍵合和 1.4 微米的背對(duì)背混合鍵合,而它之所以如此激進(jìn),就是希望通過(guò)這項(xiàng)技術(shù)繼續(xù)分解和堆疊圖像傳感器像素的功能,以此捕捉更多光線和數(shù)據(jù),將其轉(zhuǎn)化為實(shí)際的照片和視頻。

SK海力士最早將于2025年量產(chǎn)混合鍵合,并準(zhǔn)備將其用于HBM4產(chǎn)品,與現(xiàn)有工藝相比,混合鍵合提高了散熱效率并減少了布線長(zhǎng)度,從而實(shí)現(xiàn)了更高的輸入/輸出密度,能夠把當(dāng)前的最大12層堆疊增加到 16 層。而SK 海力士 PKG 技術(shù)開(kāi)發(fā)負(fù)責(zé)人Ki-il Moon 表示:“我們正在專注于該技術(shù)的開(kāi)發(fā)(與混合鍵合相關(guān)),并且實(shí)際上已經(jīng)獲得了有意義的產(chǎn)量,該技術(shù)將于2025~2026年實(shí)現(xiàn)商業(yè)化。”

三星在2020年8月,就對(duì)外展示了其自己的3D封裝技術(shù)——X-Cube,全稱為“eXtended-Cube”,將SRAM層堆疊在邏輯層之上,允許多層超薄堆疊,其表示三星代工廠正在開(kāi)發(fā)超細(xì)間距銅-銅混合鍵合,其已經(jīng)實(shí)現(xiàn)了小于 4微米的間距。

英特爾在2022年12月的IEEE國(guó)際電子器件會(huì)議上,宣布了全新的混合鍵合技術(shù),gaijishu將互連間距繼續(xù)微縮到3微米,英特爾實(shí)現(xiàn)了與單片式系統(tǒng)級(jí)芯片(system-on-chip)連接相似的互連密度和帶寬,與IEDM 2021上公布的成果相比,英特爾在IEDM 2022上展示的最新混合鍵合技術(shù)將功率密度和性能又提升了10倍。

此外,2002年6月,CEA-Leti 和英特爾宣布了一種全新的混合鍵合自對(duì)準(zhǔn)工藝,使用水滴的毛細(xì)力(capillary forces)來(lái)對(duì)齊目標(biāo)wafer上的die,該工藝有可能增加校準(zhǔn)精度以及每小時(shí)數(shù)千個(gè)芯片的制造吞吐量,采用取放工具后鍵合的最先進(jìn)的對(duì)準(zhǔn)是 1μm,最好的情況是 700nm,而新工藝提供低于 500nm 甚至小于 200nm 的后鍵合對(duì)準(zhǔn)。

imec高級(jí)研究員、研發(fā)副總裁兼3D系統(tǒng)集成項(xiàng)目主任Eric Beyne在IEDM的一篇論文中表示,目前imec的研究已經(jīng)證明了在7微米間距實(shí)現(xiàn)混合鍵合的可行性。imec官方表示,利用這項(xiàng)技術(shù),芯片之間或芯片與硅中介層之間的 3D 互連密度比現(xiàn)有技術(shù)高出十六倍以上其開(kāi)發(fā)間距小至3μm且具有高公差拾放精度的芯片間混合鍵合。

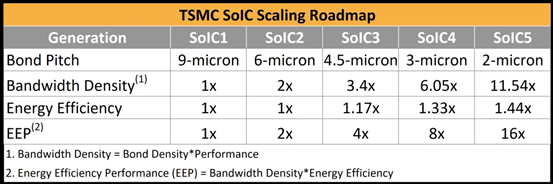

臺(tái)積電無(wú)疑是混合鍵合的集大成者,其SoIC 封裝技術(shù)依靠混合鍵合,在芯片 I/O 上實(shí)現(xiàn)了強(qiáng)大的接合間距可擴(kuò)展性,實(shí)現(xiàn)了高密度的芯片到芯片互連,其鍵合間距從 10 微米以下開(kāi)始,臺(tái)積電表示與目前業(yè)界最先進(jìn)的封裝解決方案相比,短芯片到芯片連接具有外形尺寸更小、帶寬更高、電源完整性和信號(hào)完整性更好以及功耗更低的優(yōu)點(diǎn)。此前,臺(tái)積電已經(jīng)展示了其第四代混合鍵合技術(shù)的研究成果,該技術(shù)可實(shí)現(xiàn)每平方毫米 100,000 個(gè)接點(diǎn)數(shù)量。

2021年底,AMD介紹了他們?cè)诜?wù)器處理器上已采用的臺(tái)積電混合鍵合技術(shù),2022 年初,AMD宣布Ryzen 7 5800X3D 也采用了Hybrid Bonding 技術(shù),將7nm SRAM 疊接在7nm 處理器之上,銅─銅混合鍵合能提升200 倍的接點(diǎn)密度,而且每個(gè)訊號(hào)傳遞所需的能量降低至三分之一以下。

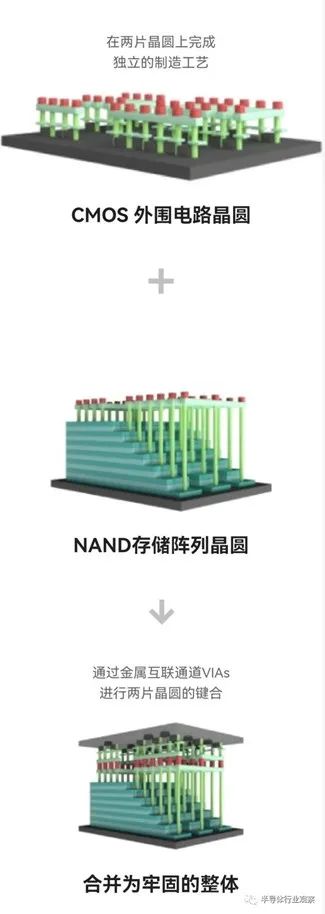

值得一提的是,國(guó)內(nèi)的長(zhǎng)江存儲(chǔ)所推出的Xtacking架構(gòu),即采用了W2W的混合鍵合技術(shù),利用不同的工藝,先后制作Memory晶圓和CMOS晶圓,在后道制程中構(gòu)建兩者的觸點(diǎn)。通過(guò)混合鍵合,這些觸點(diǎn)被鏈接導(dǎo)通,Memory和CMOS在垂直方向?qū)崿F(xiàn)了互聯(lián)。

長(zhǎng)江存儲(chǔ)官方表示,混合鍵合在3D NAND閃存上實(shí)現(xiàn)數(shù)十億根金屬通道的連接,隨著層數(shù)的不斷增高,基于晶棧Xtacking所研發(fā)制造的3D NAND閃存將更具成本和創(chuàng)新優(yōu)勢(shì)。

針對(duì)這一項(xiàng)新興技術(shù),設(shè)備廠商們也未能置身事外,混合鍵合作為一項(xiàng)后道工藝,其設(shè)備主要由德國(guó)的蘇斯(Karl Suss)和奧地利的EVG(EV Group)所提供,日本的佳能和三菱目前也有意發(fā)展該鍵合設(shè)備,但目前市占率和技術(shù)水平還和歐洲廠商有一定差距。

混合鍵合即是未來(lái)?

對(duì)于混合鍵合技術(shù)來(lái)說(shuō),目前最大的應(yīng)用方式依舊是以索尼為代表的堆棧式CIS,經(jīng)過(guò)數(shù)年的優(yōu)化后,目前CIS領(lǐng)域在利用這項(xiàng)工藝時(shí)可謂是得心應(yīng)手,未來(lái)也有望實(shí)現(xiàn)更大規(guī)模的量產(chǎn)。

而第二大應(yīng)用領(lǐng)域無(wú)疑是DRAM和NAND,我們可以看到三星、海力士和長(zhǎng)江存儲(chǔ)等在這方面的積極布局,部分廠商已經(jīng)拿出了一定成果,可能在2025年,我們就能見(jiàn)到混合鍵合技術(shù)在該領(lǐng)域的量產(chǎn)落地。

而最后的應(yīng)用場(chǎng)景即以臺(tái)積電的SoIC技術(shù)為代表的3D先進(jìn)封裝,目前在AMD處理器上已經(jīng)實(shí)現(xiàn)量產(chǎn),未來(lái)蘋果也有望在MacBook所搭載的M系列處理器上采用這一技術(shù),其大規(guī)模投產(chǎn)可能也會(huì)在2025年左右。

芯片提升性能以往看制程,如今看封裝,封裝看向異構(gòu)集成,而異構(gòu)集成的過(guò)往難點(diǎn)就是鍵合,如今銅─銅混合鍵合日趨成熟,背后環(huán)環(huán)相扣的工藝就有望實(shí)現(xiàn)芯片性能的下一步飛躍,我們深信這一天已不再遙遠(yuǎn)。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27714瀏覽量

222660 -

芯片材料

+關(guān)注

關(guān)注

0文章

9瀏覽量

8878 -

硅晶片

+關(guān)注

關(guān)注

0文章

74瀏覽量

15251

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

倒裝封裝(Flip Chip)工藝:半導(dǎo)體封裝的璀璨明星!

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過(guò)程和生產(chǎn)工藝

【「大話芯片制造」閱讀體驗(yàn)】+ 半導(dǎo)體工廠建設(shè)要求

先進(jìn)封裝有哪些材料

富士膠片開(kāi)始銷售用于最先進(jìn)半導(dǎo)體生產(chǎn)的材料

led封裝和半導(dǎo)體封裝的區(qū)別

晶體硅為什么可以做半導(dǎo)體材料

PCB半導(dǎo)體封裝板:半導(dǎo)體產(chǎn)業(yè)的堅(jiān)實(shí)基石

半導(dǎo)體封裝材料全解析:分類、應(yīng)用與發(fā)展趨勢(shì)!

閑談半導(dǎo)體封裝工藝工程師

柳鑫實(shí)業(yè)總部大樓及半導(dǎo)體封裝新材料項(xiàng)目奠基儀式

半導(dǎo)體封裝工藝面臨的挑戰(zhàn)

半導(dǎo)體封裝工藝的研究分析

半導(dǎo)體后端工藝:封裝設(shè)計(jì)與分析

半導(dǎo)體先進(jìn)封裝技術(shù)

半導(dǎo)體芯片材料工藝和先進(jìn)封裝

半導(dǎo)體芯片材料工藝和先進(jìn)封裝

評(píng)論