在硬件調(diào)試時,經(jīng)常需要用 ILA 采集一些 FPGA 內(nèi)部或者對外的初始化信號,然而在下載完 Bitstream 后立即采集這些變化稍縱即逝的信號,比如在 1uS 內(nèi)手動觸發(fā) ILA 采集信號,以普通人的手速顯然是無能為力的。有的變通方法比如在程序中加入一定的延時量或者外部按鍵做觸發(fā) ILA 采集也可以實現(xiàn)。但是某些應(yīng)用場景下,初始化必須在上電后的一定時間范圍內(nèi)完成。本文將介紹一種可適用于上述場景的方法,即在下載 Bitstream 后自動觸發(fā) ILA 采集,為硬件調(diào)試提供更多便利。

調(diào)試方法:

1. 設(shè)備信息

操作系統(tǒng):Win10

硬件平臺:Xilinx VCU118開發(fā)板

軟件版本:AMD Vivado2022.1

2. 代碼分析

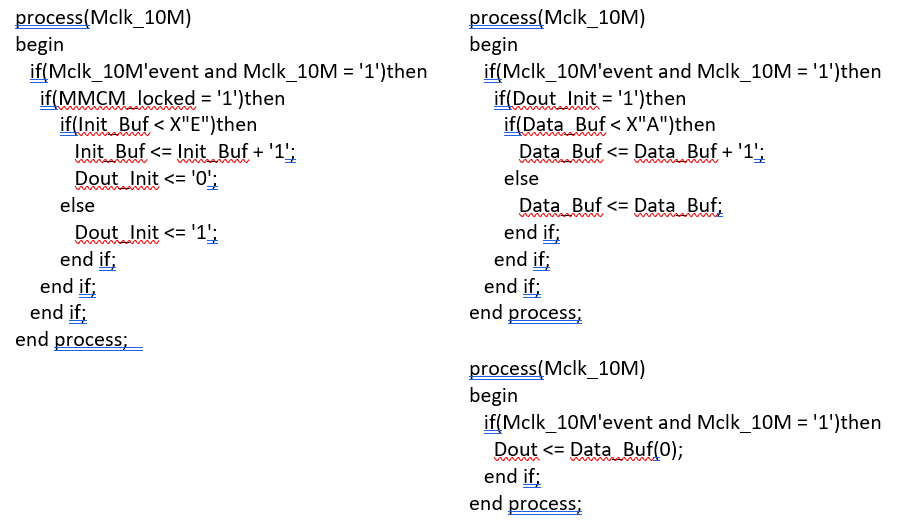

當(dāng) MMCM 初始化完成,Locked 信號置1后,Init_Buf 開始計數(shù),當(dāng) Init_Buf 等于 0x0E 時,Dout_Init 置1觸發(fā) Data_Buf 開始計數(shù),最終控制 Dout 輸出5個脈沖。整個過程大約在 1uS 內(nèi)結(jié)束,普通人的手速是無法在如此短的時間內(nèi)采集到這組信號。

3. Vivado 操作步驟

打開 Vivado,新建工程按照常規(guī)流程完成 synthesis 后,點擊 Setup Debug,將 Data_Buf, Dout, MMCM_locked, Dout_Init, Init_Buf 這些信號加入到 ILA 中,設(shè)置 100MHz 的時鐘作為 ILA 的采集時鐘。

Implementation 后 Generate Bitstream 并且下載到 FPGA。

此時可以看到之前連接到 ILA 的信號都已經(jīng)顯示,設(shè)置 ILA 的觸發(fā)條件,本工程設(shè)置為當(dāng) Dout_Init =1 時觸發(fā) ILA 采集。

運行

cdc:/ILA_Startup/ILA_Startup.runs/impl_1/

粗體部分可設(shè)置為任意的工程路徑,這樣便于在生成 bit 以后找到對應(yīng)的文件。

在 Tcl Console 窗口輸入:

run_hw_ila -file ila_trig.tas [get_hw_ilas hw_ila_1] -force

Open implementation design,在Tcl窗口輸入:apply_hw_ila_trigger ila_trig.tas

在Tcl窗口輸入:

write_bitstreamc:/ILA_Startup/ILA_Startup.runs/impl_1/trig_at_startup.bit -force

粗體部分可設(shè)置為任意的工程路徑。

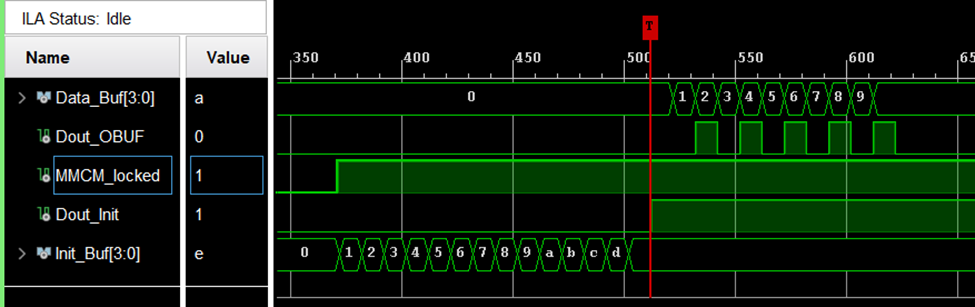

把新生成的 trig_at_startup.bit 通過 JTAG 下載到器件,下載完成后可以看到 ILA 將自動觸發(fā)采集信號,如下圖所示:

注意事項:

改變 ILA 的觸發(fā)條件后,需要重復(fù)上面 Step4- Step7 的步驟。

改變 ILA 的信號連接后,需要重復(fù)上面 Step2- Step7 的步驟。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606057 -

操作系統(tǒng)

+關(guān)注

關(guān)注

37文章

6896瀏覽量

123755 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

5121瀏覽量

98217 -

ILA

+關(guān)注

關(guān)注

0文章

5瀏覽量

3630

原文標(biāo)題:開發(fā)者分享|AMD Vivado Hardware Debug 技巧-如何在下載 Bitstream 后自動觸發(fā) ILA 采集

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何實現(xiàn)ILA Cross Trigger

如何在下載flash圖像時從IAR編程選項字節(jié)

如何使用AXI配置的ILA調(diào)試PCIe AXI接口?

LabVIEW如何控制工業(yè)相機軟觸發(fā)采集圖像

Vivado在線調(diào)試方法-Vivado內(nèi)嵌邏輯分析儀器的使用

JLINK在下載程序的過程中怎么實現(xiàn)插入目標(biāo)板自動下載?

什么是D-ILA投影技術(shù)

Vivado中關(guān)于ILA的詳解

Vivado之ILA詳解

如何在Vivado下設(shè)置BITSTREAM配置信息

教你們怎么設(shè)置或獲取BITSTREAM屬性信息

ILA工作原理 ILA使用方法與注意

如何在SQL中創(chuàng)建觸發(fā)器

如何在汽車CAN應(yīng)用中使用負(fù)邊緣觸發(fā)觸發(fā)器節(jié)省電力

如何在下載Bitstream后自動觸發(fā)ILA采集

如何在下載Bitstream后自動觸發(fā)ILA采集

評論