2.5/3D-IC封裝是一種用于半導體封裝的先進芯片堆疊技術,它能夠把邏輯、存儲、模擬、射頻和微機電系統 (MEMS)集成到一起,是未來封裝的發展方向。作為晶圓代工一哥的臺積電,是半導體技術革新的領頭羊,那么它有哪些前沿的2.5/3D IC封裝技術呢?

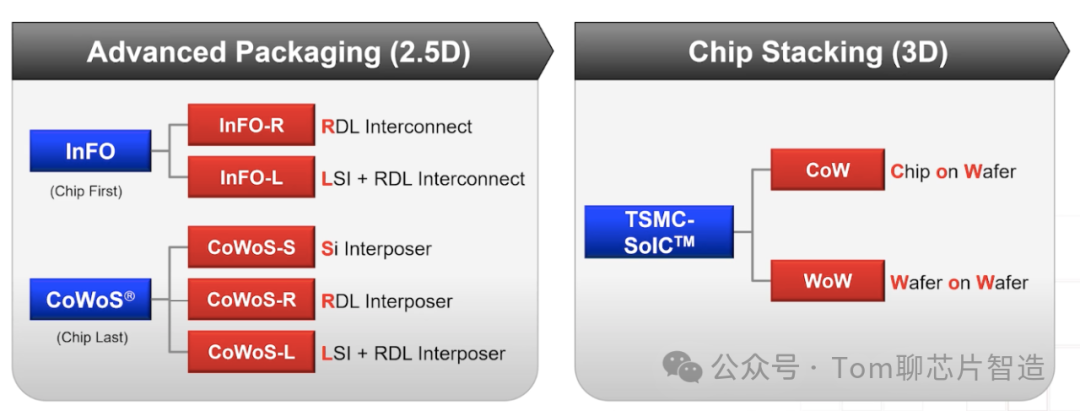

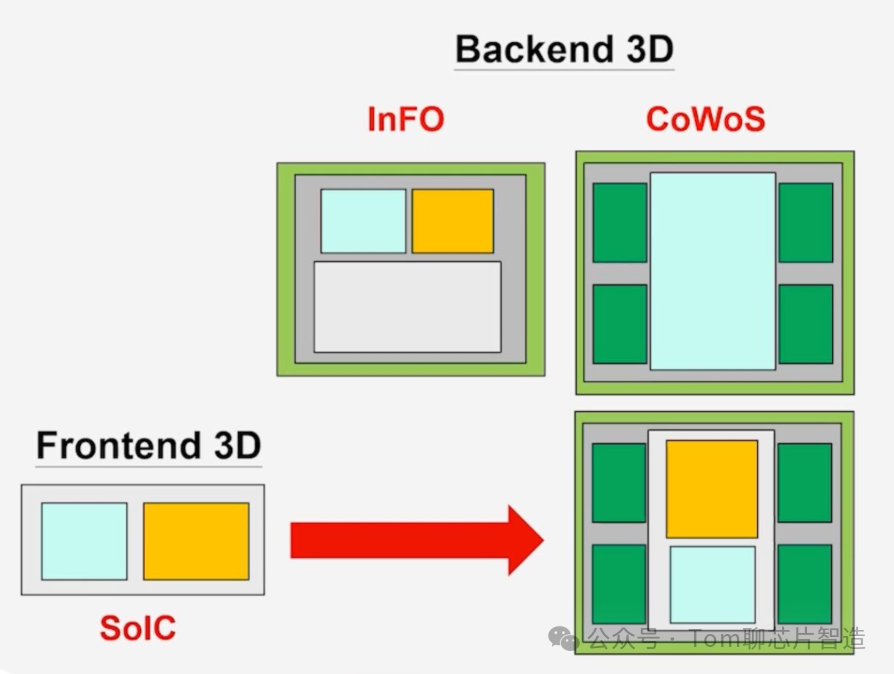

臺積電的2.5/3D IC 封裝主要有TSMC-SoIC,InFO,CoWoS三種類型。

TSMC-SoIC

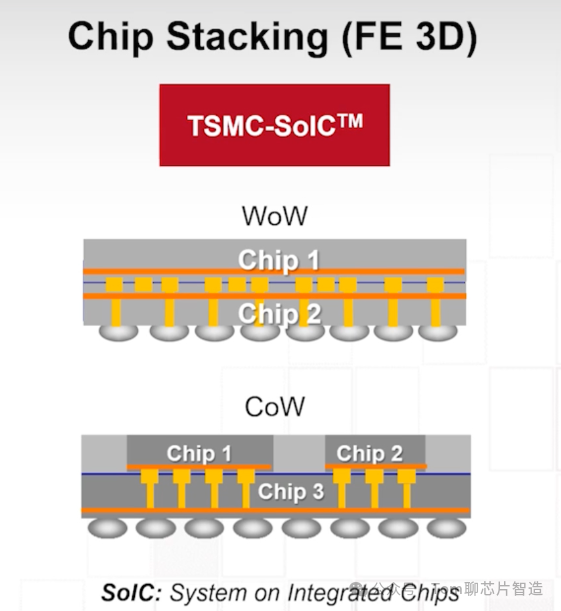

TSMC-SoIC(System on Integrated Chips),能對10納米以下的制程進行晶圓級的集成,最關鍵的創新是采用了無凸點(no-Bump)的鍵合結構。

傳統的3D IC封裝技術通常用微凸點(micro-bumps)作為芯片間的互連結構。然而,微凸點的間距限制了互連密度,因而限制了整體的集成密度和性能。

相比之下,SoIC技術采用了無凸點的直接鍵合技術,這種技術能夠減小芯片間距離,從而彌補了傳統3D IC封裝的短板。

TSMC的SoIC又包含了CoW(Chip-on-Wafer)和WoW(Wafer-on-Wafer)兩種形式。

CoW是將單獨的芯片(Chip)直接鍵合到一個待加工的晶圓(Wafer)上,而WoW則是將整個晶圓與另一個晶圓直接堆疊并鍵合。

InFO

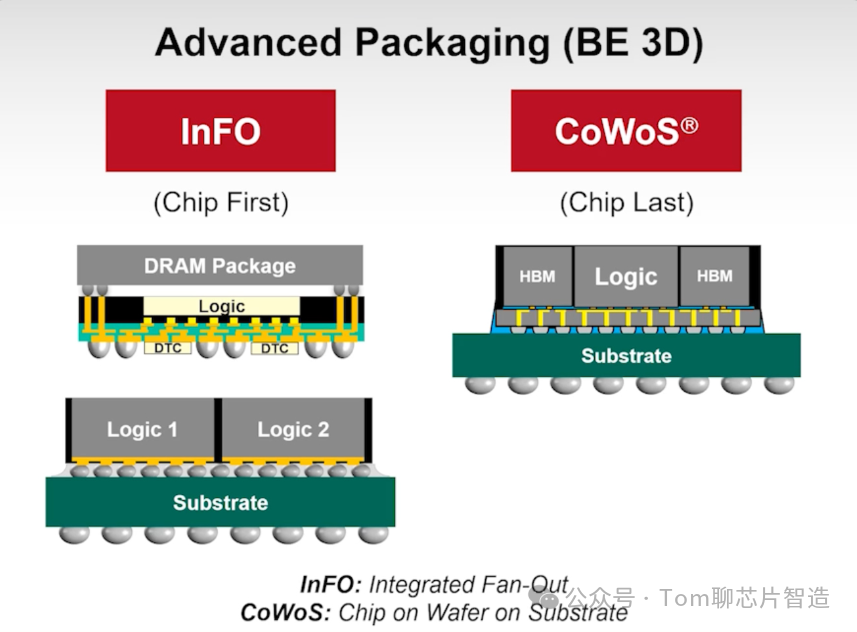

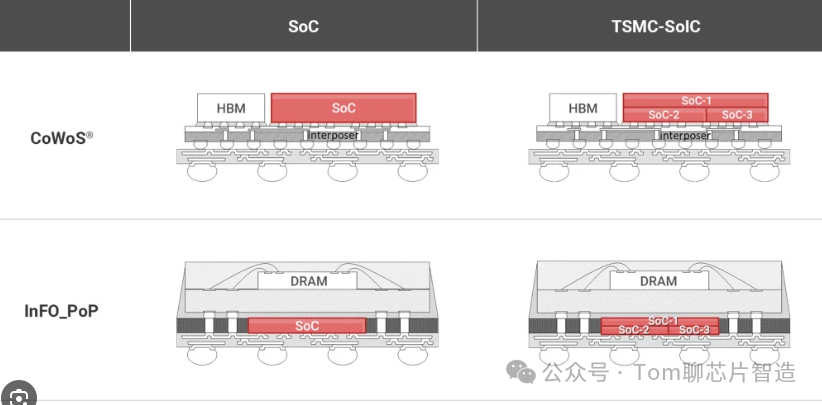

InFO(Integrated Fan-Out),是一種先進的扇出型晶圓級封裝(FOWLP)技術。InFO技術通過在晶圓上實現裸晶的扇出式布線(Fan-Out),使得芯片不需要傳統的基板,直接在芯片的外圍形成更多的I/O連接點。隨著技術的發展,TSMC推出了幾種不同的InFO技術變體,以滿足不同應用的需求,包括InFO-PoP、InFO-oS、InFO-LSI等。

CoWoS

CoWoS(Chip-on-Wafer-on-Substrate)是一種先進的2.5D封裝技術,它是將多個不同功能的芯片首先封裝到一個硅轉接板上,利用這個硅轉接板上的高密度布線實現芯片間的互連,然后整個結構再被安裝到一個更大的封裝基板上。CoWoS包括CoWoS-S,CoWoS-R,CoWoS-L. TSMC-SoIC,InFO,CoWoS之間的關系?

審核編輯:劉清

-

臺積電

+關注

關注

44文章

5685瀏覽量

166996 -

TSMC

+關注

關注

3文章

177瀏覽量

84599 -

晶圓

+關注

關注

52文章

4973瀏覽量

128313 -

IC封裝

+關注

關注

4文章

185瀏覽量

26817 -

mems芯片

+關注

關注

1文章

48瀏覽量

6604

原文標題:臺積電最前沿的2.5/3D IC封裝技術有哪些?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電它有哪些前沿的2.5/3D IC封裝技術呢?

臺積電它有哪些前沿的2.5/3D IC封裝技術呢?

評論