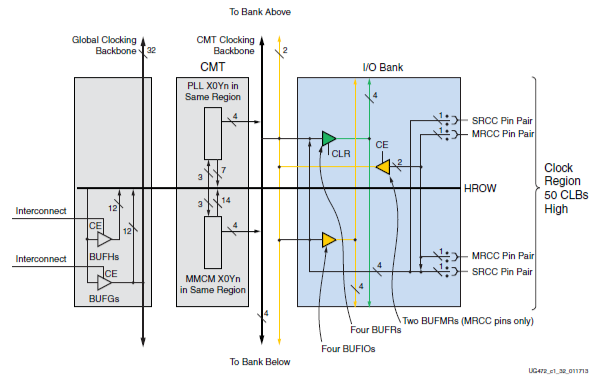

UltraScale架構的設備在時鐘架構上有顯著的創新,全局時鐘緩沖器和局部時鐘緩沖器之間的差異很小。因此,7系列的區域時鐘緩沖器已被新的時鐘緩沖器取代,這些新的時鐘緩沖器具有更廣泛的全局覆蓋范圍,同時自動利用局部時鐘緩沖器進行時鐘的局部分配。CMT模塊由一個MMCM和兩個PLL組成。MMCM與7系列家族非常相似,而PLL則為I/O PHY時鐘提供了新特性,但在時鐘設備其他部分的功能和連接性方面有所減少。

與7系列FPGA的關鍵差異

已從該架構中移除BUFMRs、BUFRs、BUFIOs及其相關的路由資源,并被新的時鐘緩沖器、時鐘路由和全新的I/O時鐘架構所取代。

BUFGCTRL及其衍生物仍然可用。新架構中引入了兩種新的全局時鐘緩沖器資源BUFGCE和BUFGCE_DIV。在局部時鐘層面,新的BUFCE_LEAF時鐘緩沖器提供了具有額外特性的局部垂直時鐘。

添加了用于GT時鐘分頻的BUFG_GT緩沖器。

現在可用的是一種新的改進的時鐘路由架構。現在有兩種類型的全局路由軌跡,稱為路由和分發。這兩種類型的路由都在CR級別提供了可分段的時鐘網絡。這兩種類型都可以由全局時鐘緩沖器驅動。分發軌跡可以由路由軌跡或直接由時鐘緩沖器資源驅動。分發軌跡提供了連接到UltraScale設備中所有時鐘點的連通性。

CMT現在有兩個PLL而不是一個。

MMCM與7系列設備中的MMCM相似。PLL具有與I/O PHY時鐘相關的新特性。然而,與其他時鐘相關的功能和連通性已經減少,與7系列FPGA相比。例如,PLL不支持相位補償或外部反饋,輸出較少,與PHY時鐘共享電壓控制振蕩器(VCO),并且與其他特性相比,與7系列設備相比有所減少。因此,大多數客戶應該使用MMCM進行一般時鐘。然而,剩余的PLL也可以使用。

MMCM輸出時鐘頻率可以在不重置MMCM的情況下動態更改。

時鐘區域的定義已經改變。時鐘區域不再在水平方向跨越半個設備寬度。UltraScale架構的時鐘區域具有固定寬度和高度的矩形形狀,并以瓦片形式組織。水平和垂直時鐘軌跡在時鐘區域邊界處分段。

時鐘能力引腳(CC)已被全局時鐘引腳(GC)所取代。此外,UltraScale+架構具有高密度(HD)I/O銀行。這些銀行包含四個全局時鐘引腳,稱為HDGC,可以連接到BUFGCEs。

審核編輯:黃飛

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

時鐘緩沖器

+關注

關注

2文章

96瀏覽量

50908 -

UltraScale

+關注

關注

0文章

118瀏覽量

31519

原文標題:UltraScale系列在時鐘架構上的升級

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

針對UltraScale/UltraScale+芯片DFX應考慮的因素有哪些(2)

Xilinx UltraScale 系列發布常見問題匯總

UltraScale– UltraScale FPGA中IODelay相比7Series FPGA的改變

xilinx 7系列FPGA之電源簡介

面向移動無線基站的Xilinx(r) Ultrascale(r)系列FPGA/SoC電源解決方案

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Xilinx 7系列與Ultrascale系列FPGA的區別

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產品

AMD推出全新Spartan UltraScale+ FPGA系列

UltraScale系列與7系列FPGA的差異

UltraScale系列與7系列FPGA的差異

評論