共讀好書

王磊,金祖偉,吳士娟,聶要要,錢晶晶,曹純紅

摘要:

基于焊點預測仿真軟件 Surface Evolver 對不同焊盤設計的球柵陣列( BGA ) 封裝焊點的回流形態進行預測。模擬不同回流焊的冷卻速率與焊盤設計對焊點的殘余應力和基板翹曲的影響。根據正交試驗和灰色關聯分析法對結果進行分析優化。結果表明,優化后的焊點芯片側的殘余應力降低了 17.9%,PCB 側的殘余應力降低了 17.1%,其翹曲值為 68.867 μm。

1 引言

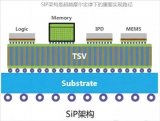

隨著封裝技術的發展,芯片封裝逐漸向復雜、高密度的 2.5D、3D 封裝發展。系統級封裝(SiP)在傳統封裝的基礎上,提升功能密度,縮短互連長度,進行系統重構,在一定程度上緩解了芯片集成的壓力。然而隨著集成度的增加,芯片的尺寸、引腳數量都在增加,設計難度提高,工藝成品良率降低,導致潛在的工藝制程風險增加 [1-2] 。球柵陣列(BGA)封裝的焊點在保證SiP 互連電性能的前提下,也承擔著機械可靠性的功能。由于焊點、基板、PCB 這一互連結構之間的熱膨脹系數(CTE)存在差異,工藝過程中的熱應力會導致BGA焊點產生較大的殘余應力以及基板翹曲等問題 [3] 。

對此,胡少華 [4] 研究了在不同回流冷卻速率下焊點結構對封裝殘余應力的影響。田文超等 [5] 研究了陶瓷封裝陣列焊點的結構參數對焊點回流焊應力應變的影響。GE 和 NJOKU 等 [6-7] 研究了焊點高度對芯片長期可靠性的影響。張浩敏等 [8] 研究了殘余應力對 BGA焊點可靠性的影響。以上研究結果表明,焊點高度、焊盤直徑、回流冷卻速率對焊點的殘余應力均有顯著影響,同時較大的殘余應力容易導致器件的焊盤坑裂。

本文針對不同的焊盤設計參數,采用 SurfaceEvolver 軟件對 BGA 焊點進行形態預測。同時以 40×40 面陣列 BGA 焊點的 SiP 封裝為研究對象,分析其芯片側、PCB 側的焊盤設計與回流冷卻速率對焊點回流殘余應力以及基板翹曲的影響。用正交試驗和灰色關聯法進行優化設計,找出最優參數組合進行驗證,為提高大尺寸陣列 SiP 封裝的設計優化提供數據參考。

2 SiP 封裝模型建立

2.1 BGA 焊點形態預測

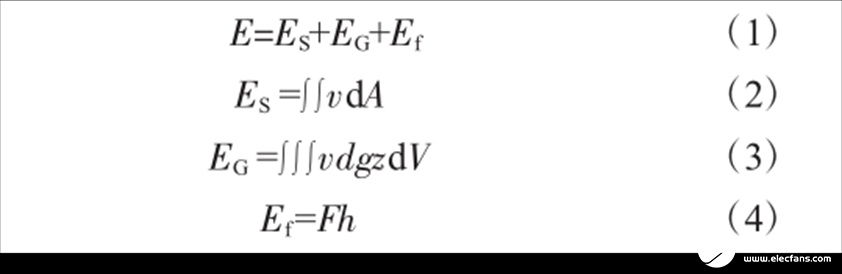

根據熱力學基本定律,自然界中任何封閉系統的存在總符合能量最小原理。因此在回流穩態后,熔融的 BGA 焊點(液相)與對流熱空氣(氣相)和上下基板焊盤(固相)組成的系統處于能量最小的狀態。單個BGA 焊點的系統能量 E 是表面勢能 E S 、焊點自身重力勢能 E G 和外力作用勢能 E f 之和,即

式中 v 為焊點表面張力,A 為焊點的自由表面積,d 為BGA 焊點密度,g 為重力加速度,z 為焊點高度坐標,V為焊點體積,F 為作用在 BGA 焊點上的壓力,h 為焊點高度。

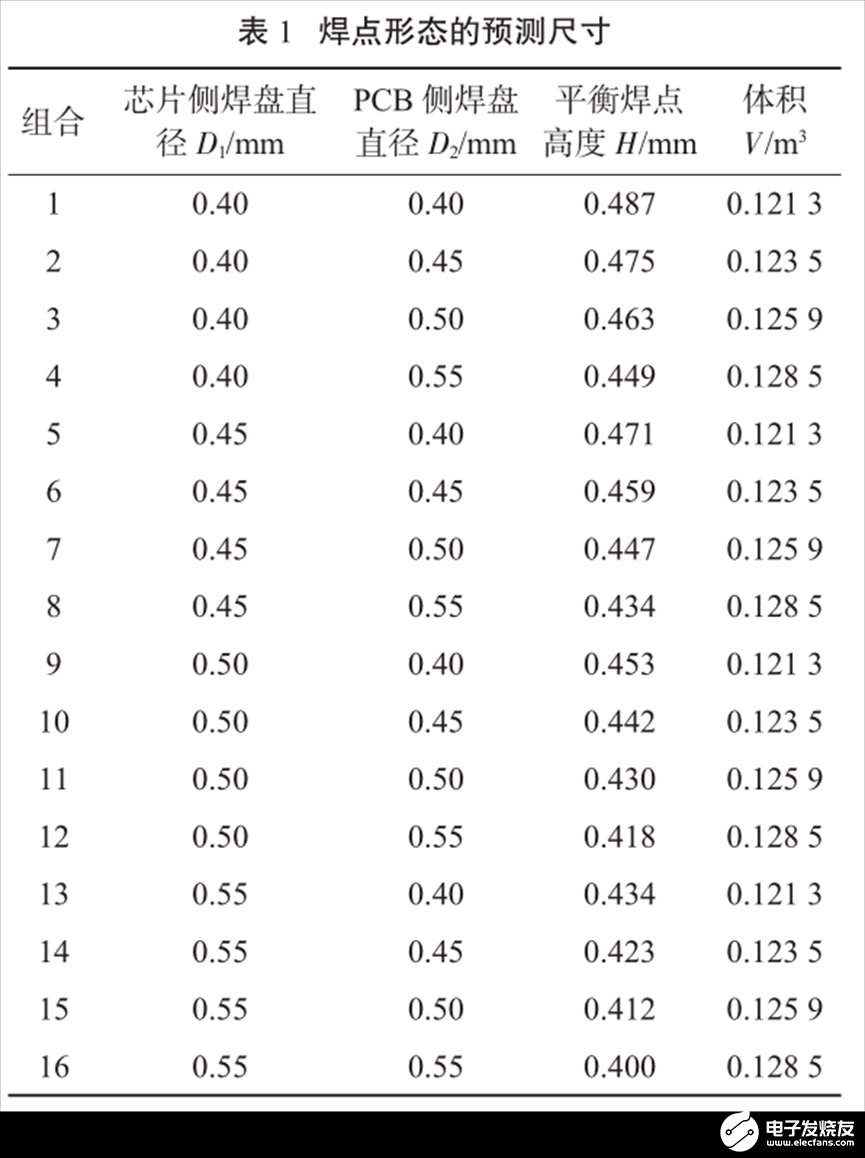

表面勢能總和 I 以泛函數形態描述為:

式中 λ 是拉格朗日乘子,V 0 為焊點的初始體積。式(5)中被積函數滿足歐拉-拉格朗日方程時,可得泛函極值,利用變分問題的數值解法可求解釬料的平衡形態 [9] 。

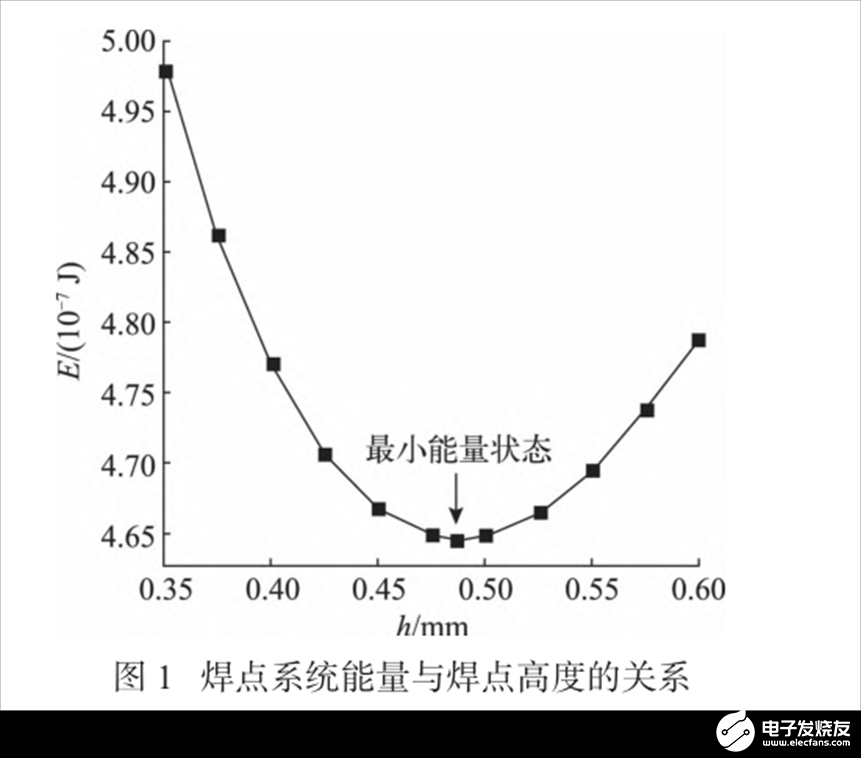

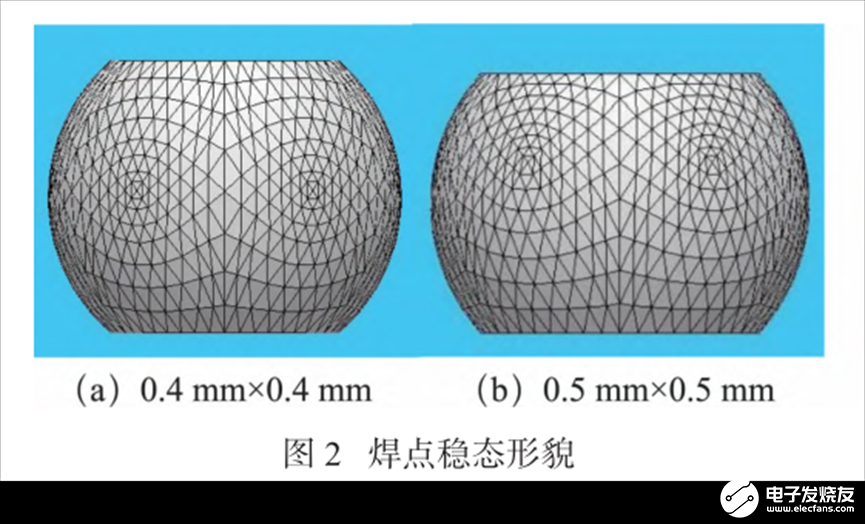

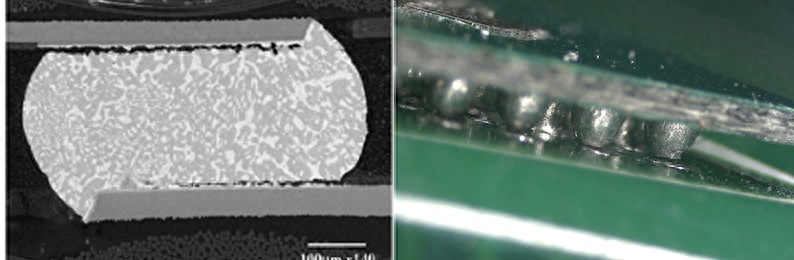

根據上述模型,采用 Surface Evolver 求解出焊點穩態形貌。本文采用 SAC305 無鉛焊點材料,其密度為7.3 g/cm 3 。BGA 的焊點間距為 1 mm 時,植球直徑為0.6mm,芯片側與PCB側的焊盤直徑分別選擇 0.4mm、0.45 mm、0.5 mm 和 0.55 mm。

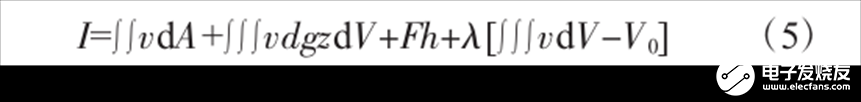

考慮到不同尺寸的焊盤在同一工藝下的錫量存在差異,最終形貌的焊點尺寸會不同。根據 IPC-7525A漏模板設計標準選擇 BGA 鋼網開孔比例以及錫膏厚度,避免選擇較大數值(容易導致實際表面貼裝過程中的焊接異常)。選擇厚度為 0.13 mm 的鋼網,開孔面積為 90%的 BGA 焊盤,樹脂的質量分數為 50%的錫膏,計算出不同焊盤設計條件下的焊點體積。當焊點體積和焊盤尺寸固定時,不同高度下的焊點系統能量與焊點高度的關系如圖 1 所示,其整體呈拋物線變化,選取不同參數組合下焊點系統能量曲線最低點時的平衡焊點高度 H,焊點形態的預測尺寸如表 1 所示。根據其尺寸參數擬合出的焊點穩態形貌如圖 2 所示。

2.2 仿真模型

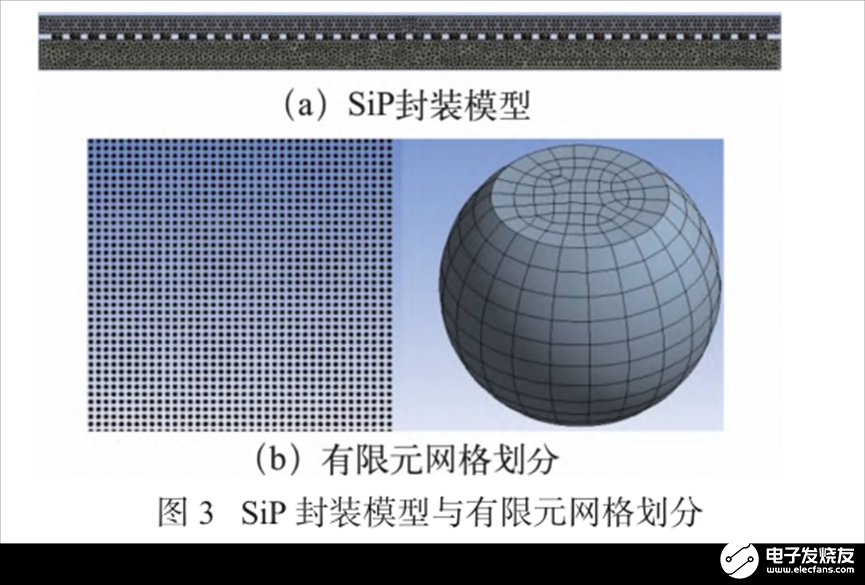

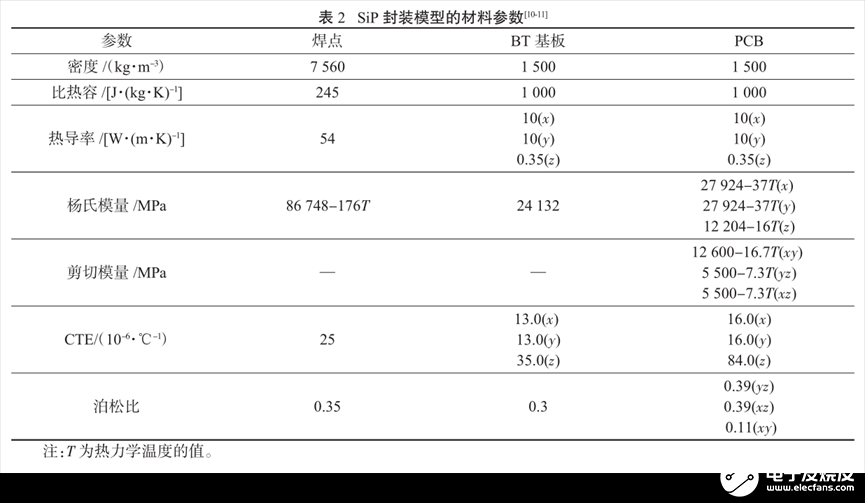

參考陣列為 40×40、pin 間距為 1 mm 的 SiP 芯片封裝結構,芯片基板尺寸為 41 mm×41 mm×1 mm,建立有限元分析模型,將模型簡化為 1/4 模型進行仿真計算,SiP 封裝模型與有限元網格劃分如圖 3 所示。焊點采用無鉛焊料,對局部焊點加密網格,采用 Anand

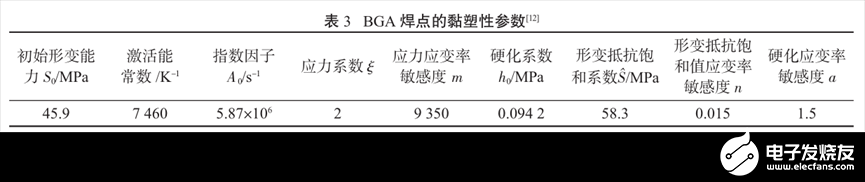

黏塑性網格單元,SiP 封裝模型的材料參數如表 2 所示,其中 x、y、z 表示坐標軸,xy、yz、xz 表示 2 個坐標軸形成的面 [10-11] 。BGA 焊點的黏塑性參數如表 3 所示 [12] 。

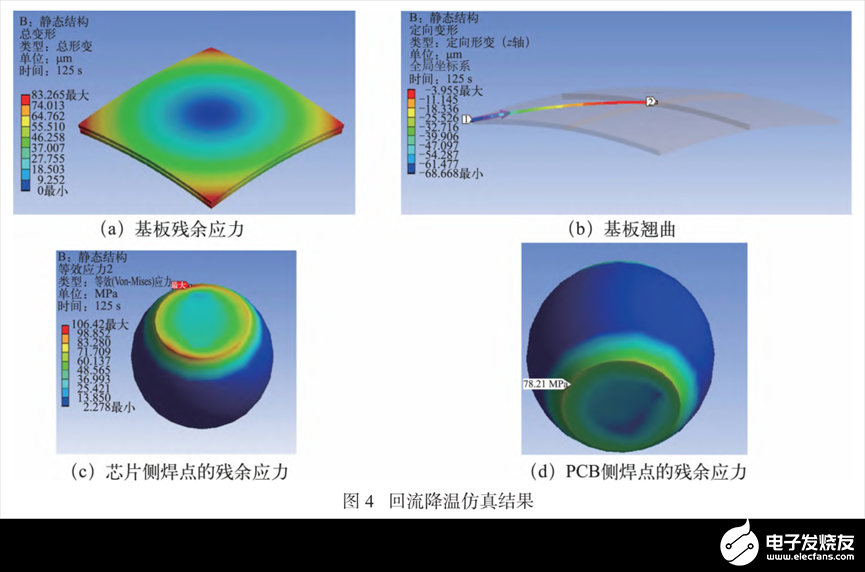

3 殘余應力與翹曲仿真

在 ANSYS workbench 仿真模塊中建立回流焊仿真分析模型。考慮到在回流冷卻過程中,焊點從液態逐漸固化,其應力會隨溫度變化。為了參考不同參數組合條件下殘余應力和翹曲的變化,以 150 ℃作為零應力參考溫度,設置環境溫度為 25 ℃。芯片側焊盤直徑為 0.4 mm,PCB 側焊盤直徑為 0.4 mm,在冷卻速率為 1 ℃·s -1 的條件下,SiP 基板的形變分布與 z 軸對角線的翹曲值如圖 4(a)(b)所示。由于 PCB 在 z 軸方向的 CTE 大于 BT 基板,在回流冷卻過程中,PCB 的收縮比例較大,產生的應力差使芯片基板向 PCB 側彎曲變形,最終呈現出哭臉型(芯片邊緣低于中心)翹曲,其翹曲值為 68.668 μm。此時四角位置的形變量最大。

芯片側焊點的殘余應力為 106.42 MPa,如圖 4(c)所示。PCB 側焊點的殘余應力為 78.21 MPa,如圖 4(d) 所示。芯片側焊點的殘余應力大于 PCB 側焊點。

4 正交試驗分析

4.1 確立變量因素與優化目標

將 BGA 焊點在回流過程中的殘余應力以及翹曲值作為優化目標,選取BGA焊點芯片側的焊盤直徑D 1 、PCB 側的焊盤直徑 D 2 以及冷卻速率 S 作為設計變量。

4.2 正交試驗設計

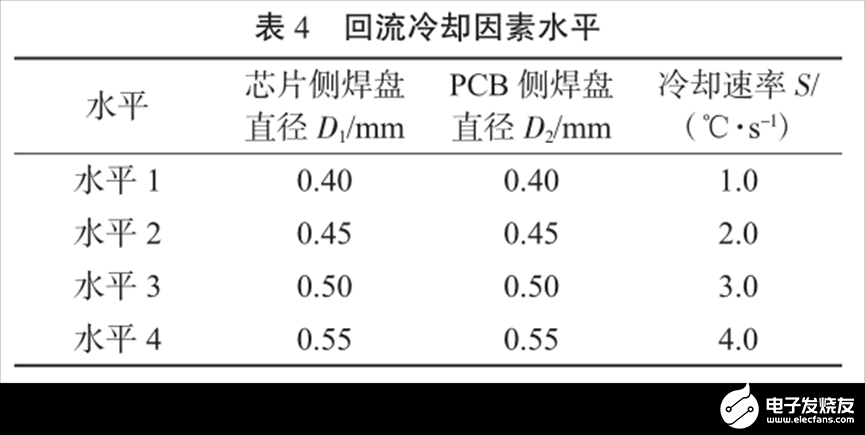

為了得出回流冷卻過程中 BGA 焊點殘余應力與翹曲值的最優組合,需要進行大量的組合試驗。為了減少試驗的工作量,同時得到各影響因子的影響程度,采用正交試驗法來優化分析方案。每個因素選取 4個水平,利用芯片側焊盤直徑和 PCB 側焊盤直徑的組合在表 1 里找到其焊點的體積和高度,據此設計出回流冷卻因素水平(見表 4)。

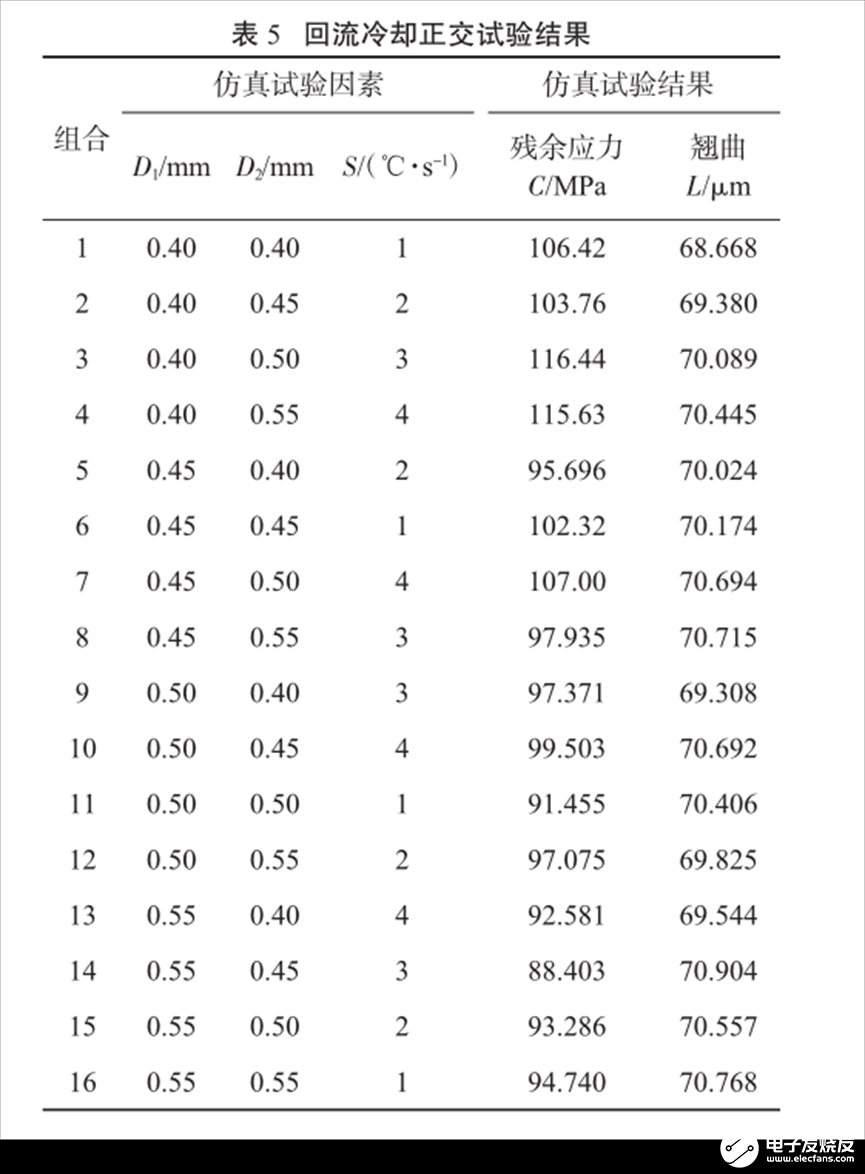

采用 L 16 (4 3 )正交表,再結合表 1 的焊點形態預測尺寸建立仿真模型,計算出回流冷卻過程中焊點的殘余應力以及基板翹曲值。得到的 16 組回流冷卻正交試驗結果如表 5 所示。

5 殘余應力與翹曲的灰色關聯分析

由于 L 16 (4 3 )正交表的試驗設計只確定了 16 組已知的白色系統組合,仍然有 48 組黑色系統組合未知,這就構成了已知和未知的灰色系統。對于雙優化目標的水平組合,常規的試驗設計優化分析無法滿足,因此引入灰色關聯分析法。2 個目標隨不同因素水平變化的關聯性量度稱為關聯度。當 2 個因素的變化區域一致時關聯度高,反之則低,因此灰色關聯分析方法會根據不同因素水平之間的灰色關聯度來衡量其數值關系 [13] 。

5.1 殘余應力與翹曲的灰色關聯系數

由于系統中數值的物理意義不同,為防止小數值序列被大數值掩蓋,統一對序列進行規范化處理。常見的處理方法有均值化法、初值化法和極差變換法,此處采用極差變換法對殘余應力和翹曲值進行規范化處理。參考序列和規范化序列分辨系數取一般值 0.5進行灰色關聯系數計算。灰色關聯系數越大,表明殘余應力與翹曲值貼合程度越大 [9] 。

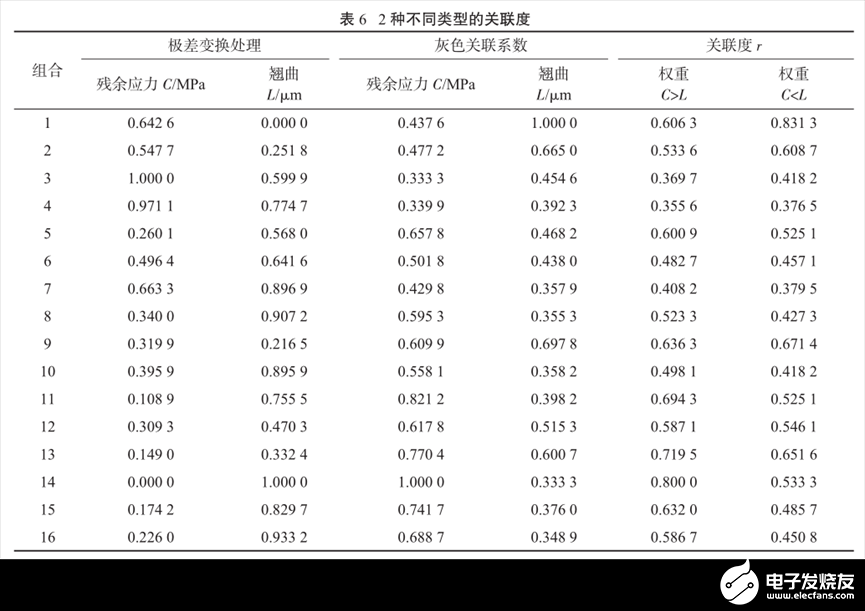

5.2 殘余應力與翹曲最優解的確定

在回流冷卻過程中,優化 BGA 焊點的殘余應力與 BT 基板的翹曲值有助于提高芯片的可靠性,其中焊點的殘余應力值與基板的翹曲值越小越好,但 2 個目標優化的權重比是個主觀因子,長期可靠性條件下的殘余應力權重大于翹曲值,工藝管控中的翹曲值權重大于殘余應力,因此 2 種不同類型的關聯度如表 6所示。

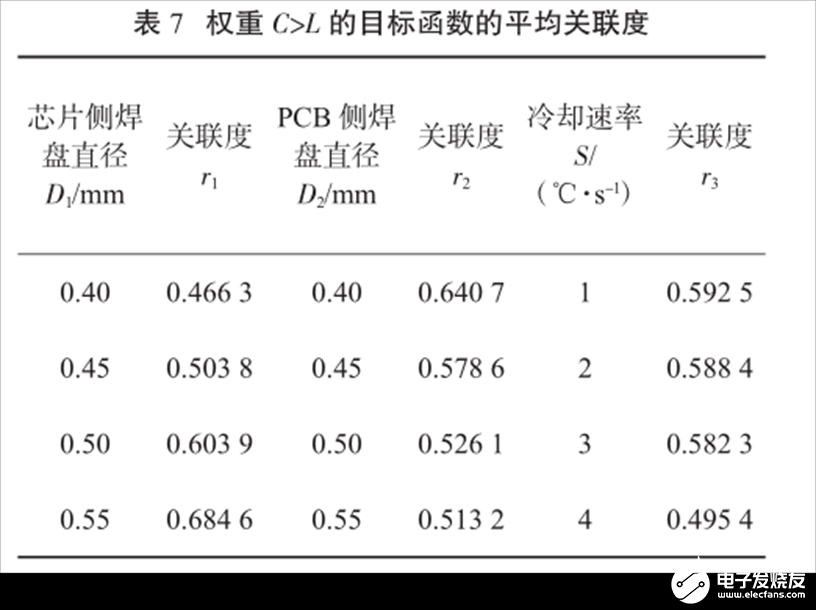

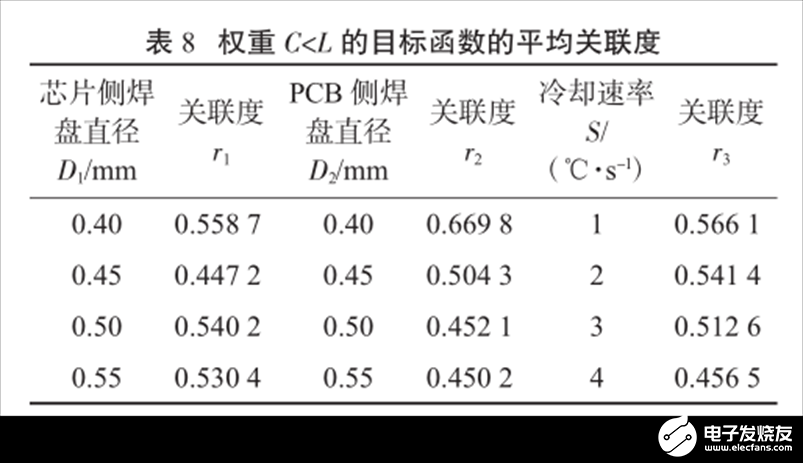

確定 BGA 最優參數組合前需計算出不同參數水平的平均關聯度,灰色關聯度的定義表明,平均關聯度越大越接近最優解,通過計算得出目標函數的平均關聯度 [9] 。其中殘余應力權重大于翹曲值的目標函數的平均關聯度如表 7 所示,其最優參數組合為D 14 D 21 S 1 ,即芯片側焊盤直徑 D 1 選第 4 組數據 0.55 mm,PCB 側焊盤直徑 D 2 選第 1 組數據 0.4 mm,冷卻速率 S選第 1 組數據 1 ℃·s -1 。翹曲值權重大于殘余應力的平均關聯度如表 8 所示,可以得出最優參數組合為D 11 D 21 S 1 ,即芯片側焊盤直徑 D 1 為 0.4 mm,PCB 側焊盤直徑 D 2 為 0.4 mm,冷卻速率 S 為1 ℃·s -1 。

5.3 焊點殘余應力與翹曲的最優參數組合仿真驗證

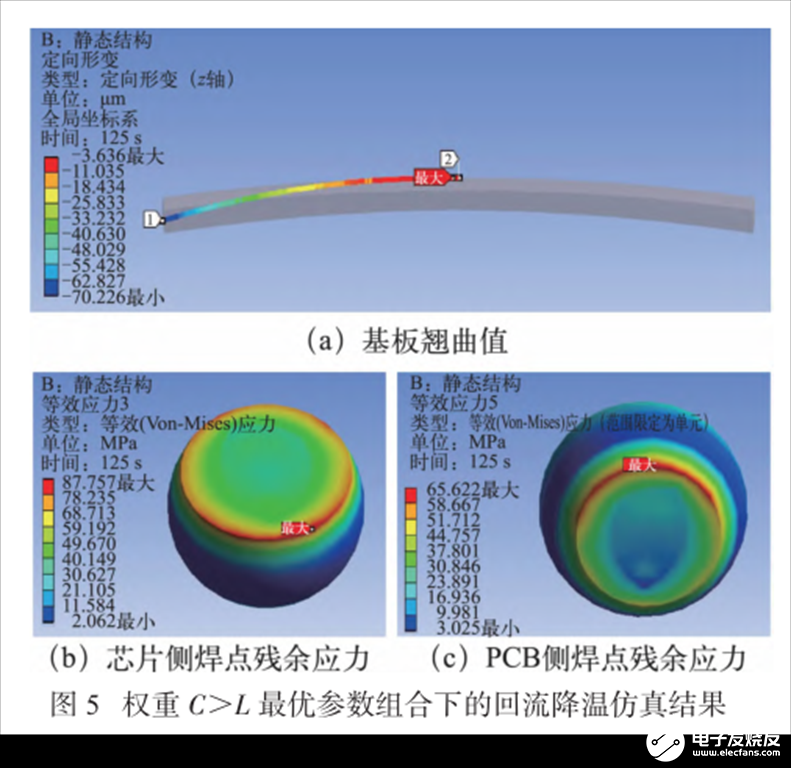

已經分析得出翹曲值權重大于殘余應力的最優參數組合為 D 11 D 21 S 1 (仿真結果見圖 4),殘余應力權重大于翹曲值的最優參數組合為 D 14 D 21 S 1 ,為了驗證灰色關聯分析的準確性,采用 D 14 D 21 S 1 的參數組合進行仿真驗證。參數組合 D 14 D 21 S 1 的仿真結果如圖 5 所示,其芯片側殘余應力為 87.757 MPa,PCB 側殘余應力為65.622 MPa,基板翹曲值為 70.226 μm。

5.4 焊點殘余應力與翹曲優化綜合仿真驗證

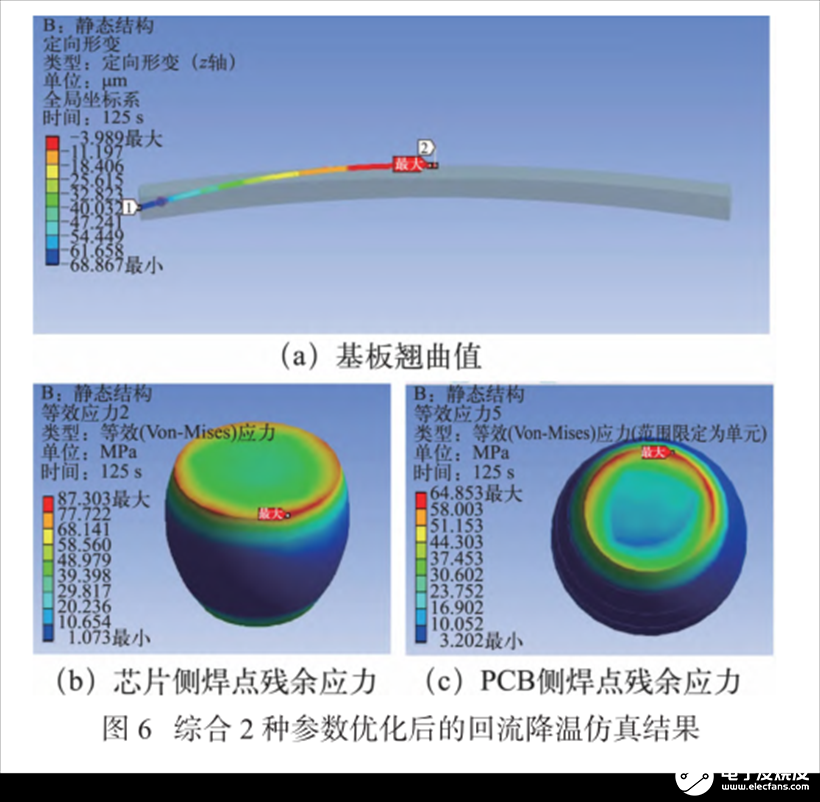

殘余應力權重大于翹曲值時的參數組合 D 14 D 21 S 1有一定的降低殘余應力的效果,但同時翹曲值會增加。同理參數組合 D 11 D 21 S 1 的翹曲值權重大于殘余應力,會導致其殘余應力增加,翹曲值降低。綜合 2 種組合結果,修改芯片側和 PCB 側的焊盤尺寸有助于優化殘余應力和翹曲值。

若同時優化 2 種參數,可將其組合,以 D 11 D 21 S 1 組合為主降低翹曲值,四角位置殘余應力較大的焊點均采用非功能焊點,采用 D 14 D 21 S 1 組合的焊點尺寸參數。綜合 2 種參數優化后的回流降溫仿真結果如圖 6 所示,其翹曲值為 68.867 μm,芯片側殘余應力為87.303 MPa,比初始值下降了 17.9%,PCB 側殘余應力為 64.853 MPa,比初始值下降了 17.1%。相比 D 11 D 21 S 1組合,其翹曲值比初始值 68.668 μm 略大,但殘余應力明顯降低,該組合綜合考慮了翹曲值與殘余應力,實現了設計優化。

6 結論

本文通過仿真軟件 Surface Evolver 對不同焊盤設計的 BGA 焊點的回流形態進行預測,研究了焊盤設計與冷卻速率對焊點的殘余應力和基板翹曲值的影響,總結出以下結論:

(1)可通過灰度分析法分析回流降溫速率,回流降溫速率的增加對基板翹曲和焊點殘余應力有一定的優化作用,可以指導工藝進行參數調整;

(2)調整芯片和 PCB 的焊盤設計可以優化基板翹曲和焊點殘余應力,可以通過設計降低工藝中的翹曲不良,減少殘余應力引起的焊點早期失效;

(3)不同產品對于翹曲和殘余應力的要求不同,可以有針對性地進行芯片側和 PCB 側的焊盤設計來降低翹曲和殘余應力或者對兩者進行綜合優化。

審核編輯 黃宇

-

芯片

+關注

關注

456文章

51170瀏覽量

427252 -

SiP

+關注

關注

5文章

506瀏覽量

105457 -

封裝

+關注

關注

127文章

7992瀏覽量

143404 -

焊點

+關注

關注

0文章

120瀏覽量

12819

發布評論請先 登錄

相關推薦

SIP封裝技術:引領電子封裝新革命!

BGA封裝器件焊點抗剪強度測試全解析,應用推拉力機

QFN封裝中焊點形成的過程

焊接應力是什么?6種方法輕松去除

2.5D封裝的熱力挑戰

PCB板彎板翹的原因及改善措施

機械應力和熱應力下的BGA焊點可靠性

電子制造中的翹曲難題:PCB板整平方法綜述

深入剖析PCB翹曲現象:成因、危害與預防策略

守護PCB板平整度!回流焊防彎曲翹曲全攻略

Sip技術是什么?Sip封裝技術優缺點

SiP 封裝的焊點形態對殘余應力與翹曲的影響

SiP 封裝的焊點形態對殘余應力與翹曲的影響

評論