FPGA設(shè)計(jì)流程主要包括以下幾個(gè)關(guān)鍵步驟:

首先,根據(jù)功能需求選擇合適的FPGA型號(hào)和開(kāi)發(fā)板,并進(jìn)行硬件資源評(píng)估、時(shí)序分析等,以確定芯片的工作頻率和性能參數(shù)。同時(shí),深入研究所選芯片的特點(diǎn)、布局、電氣參數(shù)等,為后續(xù)設(shè)計(jì)做好知識(shí)儲(chǔ)備。

接下來(lái),制定詳細(xì)的設(shè)計(jì)規(guī)劃。通過(guò)分析功能需求和硬件資源、時(shí)序等約束條件,確定FPGA設(shè)計(jì)的整體結(jié)構(gòu)和模塊劃分,以及各模塊之間的數(shù)據(jù)交互方式和通信協(xié)議。這一步驟需充分考慮設(shè)計(jì)的可擴(kuò)展性、性能和可維護(hù)性。

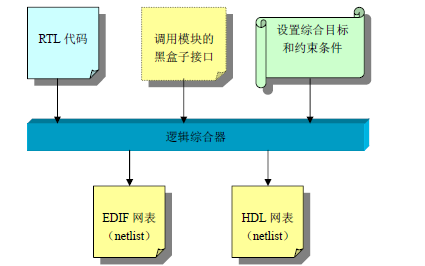

隨后,使用硬件描述語(yǔ)言(如VHDL或Verilog HDL)編寫(xiě)代碼,實(shí)現(xiàn)所需功能。在編寫(xiě)代碼前,進(jìn)行適當(dāng)?shù)哪K化設(shè)計(jì),便于后期測(cè)試和維護(hù)。

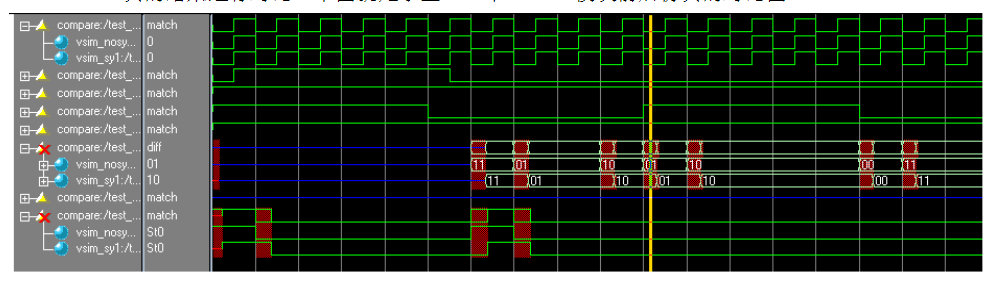

完成代碼編寫(xiě)后,進(jìn)入驗(yàn)證測(cè)試階段。包括仿真、功能測(cè)試、時(shí)序約束驗(yàn)證等多個(gè)環(huán)節(jié),確保設(shè)計(jì)的正確性和可靠性。

最后,將驗(yàn)證通過(guò)的設(shè)計(jì)下載至FPGA芯片上,進(jìn)行實(shí)際的硬件測(cè)試和驗(yàn)證。

在整個(gè)設(shè)計(jì)流程中,還需注意遵循最佳設(shè)計(jì)實(shí)踐,如優(yōu)化代碼結(jié)構(gòu)、減少資源消耗、提高時(shí)序性能等,以獲得高性能、低功耗的FPGA解決方案。

通過(guò)這一流程,可以確保FPGA設(shè)計(jì)的準(zhǔn)確性、高效性和可靠性,滿足各種復(fù)雜應(yīng)用的需求。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

606012 -

芯片

+關(guān)注

關(guān)注

456文章

51177瀏覽量

427263 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

5121瀏覽量

98195

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

華為FPGA設(shè)計(jì)流程指南

華為FPGA設(shè)計(jì)流程指南

FPGA的設(shè)計(jì)流程是怎樣的

Alter FPGA的設(shè)計(jì)流程以及DSP設(shè)計(jì)

FPGA設(shè)計(jì)流程指南

從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì)

FPGA設(shè)計(jì)流程“又臭又長(zhǎng)”?從eda工具理解超級(jí)簡(jiǎn)單!

FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載

FPGA設(shè)計(jì)流程及原理

FPGA設(shè)計(jì)流程

fpga設(shè)計(jì)流程

fpga設(shè)計(jì)流程

評(píng)論