FPGA(現(xiàn)場可編程邏輯門陣列)主要使用的編程語言是硬件描述語言(HDL)。在眾多的HDL中,Verilog HDL和VHDL是最常用的兩種。

Verilog HDL和VHDL都是用于邏輯設(shè)計的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。它們能形式化地抽象表示電路的結(jié)構(gòu)和行為,支持邏輯設(shè)計中層次與領(lǐng)域的描述,具有電路仿真與驗證機(jī)制以保證設(shè)計的正確性,并便于文檔管理和設(shè)計重用。

fpga用什么語言開發(fā)

FPGA(現(xiàn)場可編程邏輯門陣列)的開發(fā)主要使用硬件描述語言(HDL)。其中,Verilog HDL和VHDL是最常用的兩種編程語言。

Verilog HDL是一種硬件描述型語言,它主要通過文本的形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為。這種語言可以表達(dá)邏輯電路圖、邏輯表達(dá)等意義,并應(yīng)用于算法級、門級到開關(guān)機(jī)的多種數(shù)字系統(tǒng)建模。

VHDL則是一種用于電路設(shè)計的高級語言,它的全稱是VHSIC Hardware Description Language,意為甚高速集成電路的硬件描述語言。VHDL主要應(yīng)用在數(shù)字電路的領(lǐng)域當(dāng)中,其硬件描述語言以及其描述風(fēng)格都和高級計算機(jī)語言較為相似。

此外,SystemVerilog也是一種可用于FPGA開發(fā)的語言,它主要是建立在Verilog語言的基礎(chǔ)之上,將硬件描述語言(HDL)與現(xiàn)代的高層級驗證語言(HVL)結(jié)合了起來,并成為下一代硬件設(shè)計和驗證的語言。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605987 -

硬件

+關(guān)注

關(guān)注

11文章

3381瀏覽量

66447 -

編程語言

+關(guān)注

關(guān)注

10文章

1950瀏覽量

34980 -

數(shù)字系統(tǒng)

+關(guān)注

關(guān)注

0文章

145瀏覽量

20907

發(fā)布評論請先 登錄

相關(guān)推薦

用MATLAB或者C語言開發(fā)FPGA有什么問題嗎

VHDL語言在FPGA/CPLD開發(fā)中的應(yīng)用?

用VHDL/VerilogHD語言開發(fā)PLD/FPGA的完整流程

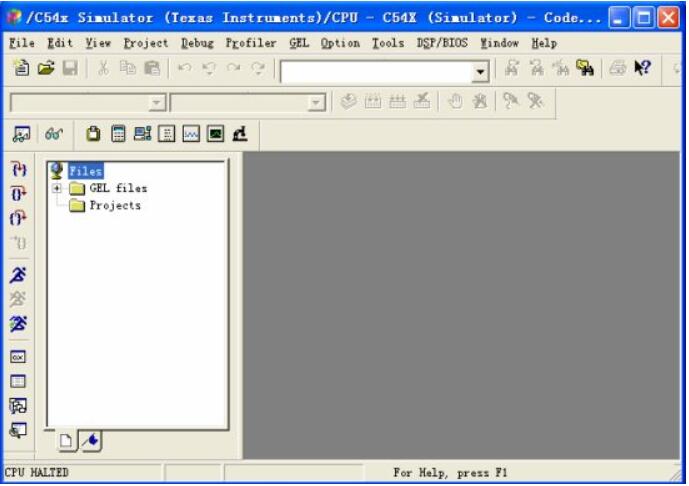

dsp編程用什么語言_dsp編程如何實現(xiàn)的

fpga用的是什么編程語言 fpga用什么語言開發(fā)

fpga用的是什么編程語言 fpga用什么語言開發(fā)

評論