還記得上次的文章,PCIe阻抗控制,85ohm和100ohm哪個好?PCIE-阻抗-高速PCB,文章里面只講到目前的主要問題,但沒有給出具體怎么解決這個問題,今天我們就通過無源仿真的方式來聊聊上次那個問題的最終解決方案。

目前我們看到PCIe系統主要有以下幾種連接方式,也可以說主要的幾種拓撲結構。

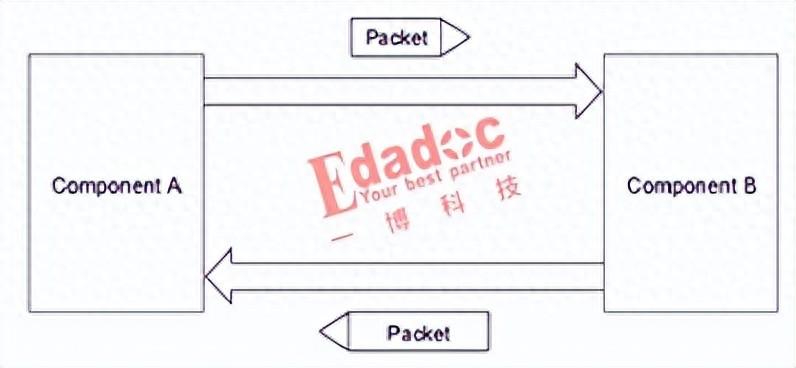

1、沒有連接器,板內芯片到芯片的PCIe總線互聯,如下圖所示:

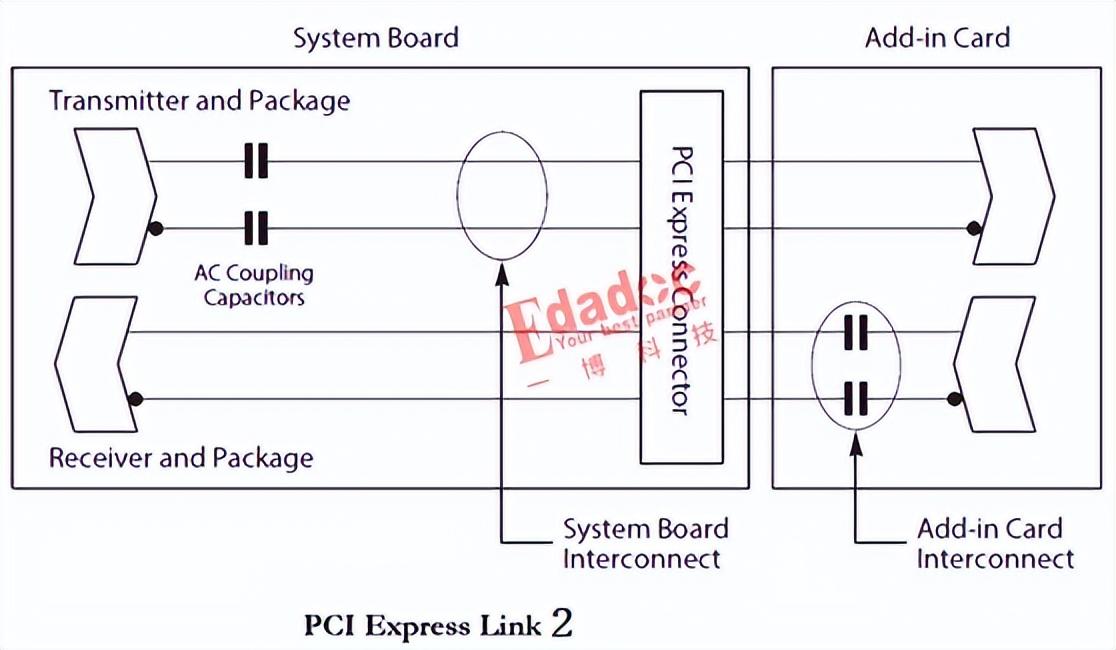

2、有一個標準的PCIe連接器,主板通過連接器到PCIe標準子卡(也叫Add-in卡),如下圖所示:

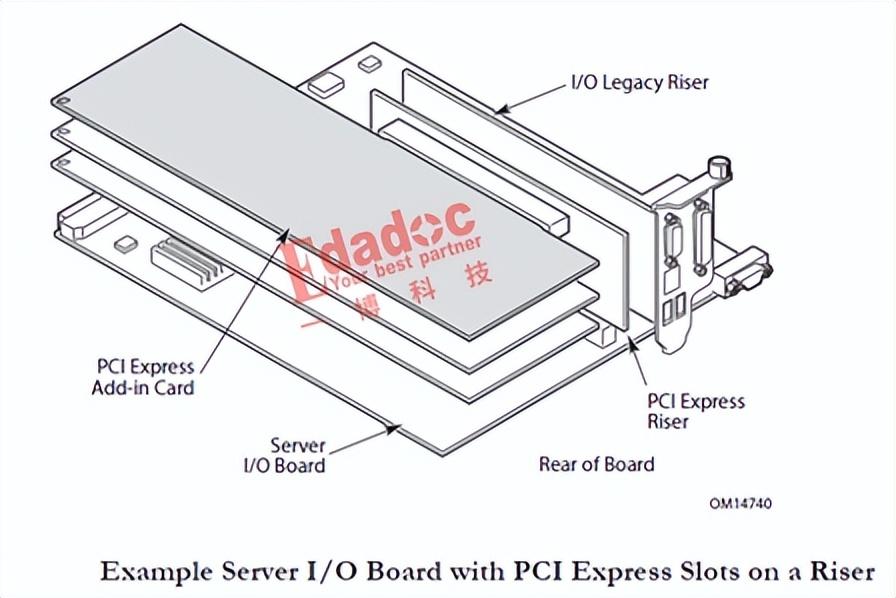

3、在上面2的基礎上,中間通過一個Riser卡互聯,如下圖所示:

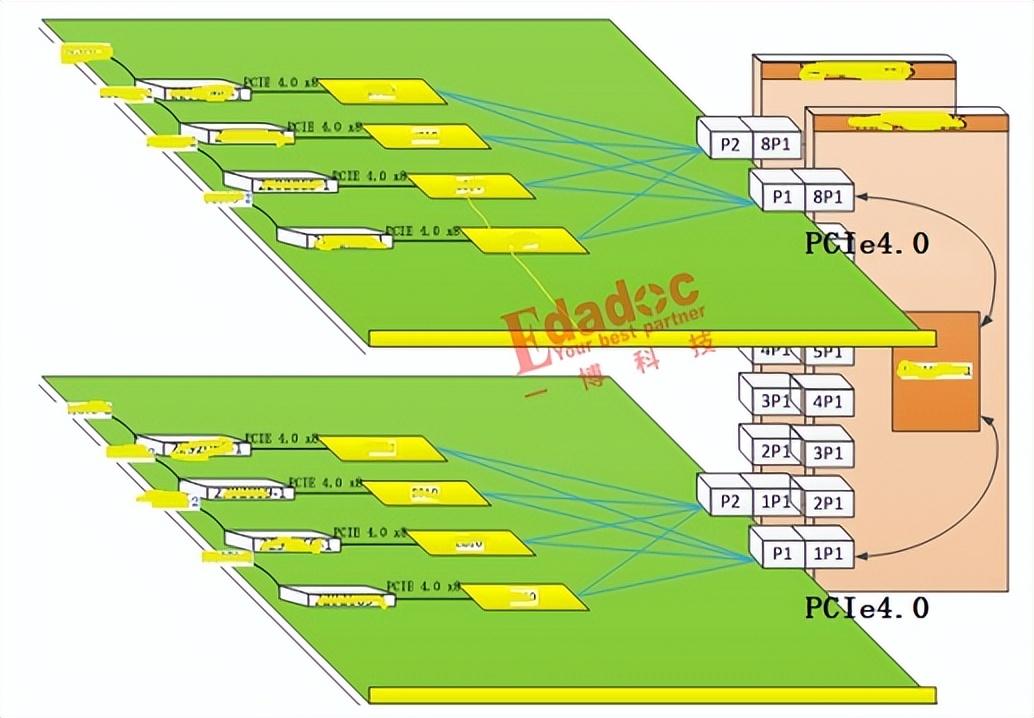

4、自定義的連接,遵循PCIe信號協議,兩塊或兩塊以上的板卡通過連接器或者線纜互聯,如下圖所示:

通過連接器互聯

通過線纜互聯

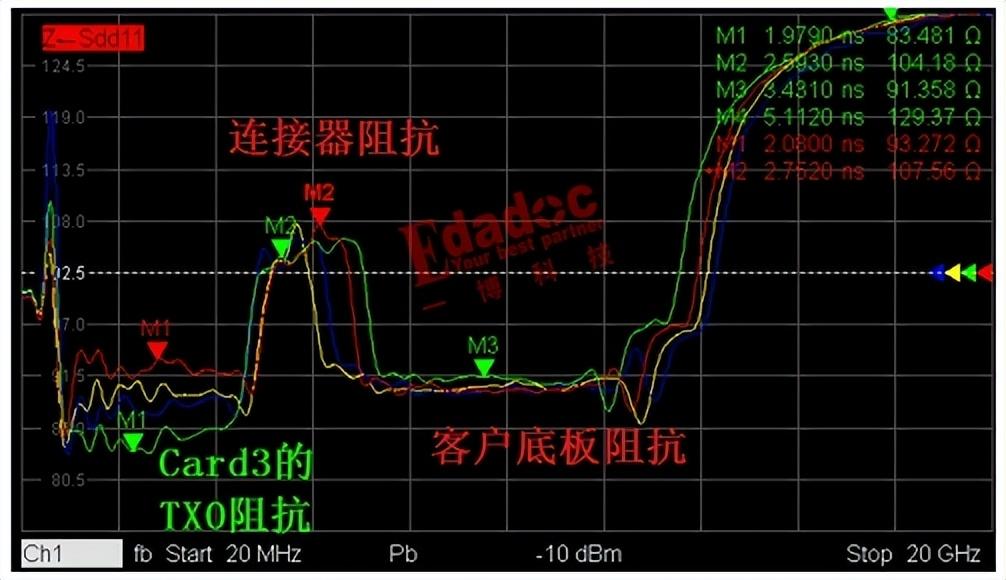

當然還有其他不同的連接方式,我們今天主要以上次案例里面的兩塊板子通過背板連接器的方式來講,和上面第四種方式比較類似。下面我們按照子卡和底板通過標準的背板連接器來連接的方式進行舉例仿真,同時也看能否還原案例中出問題板子的情況,如下圖為之前測試的結果。

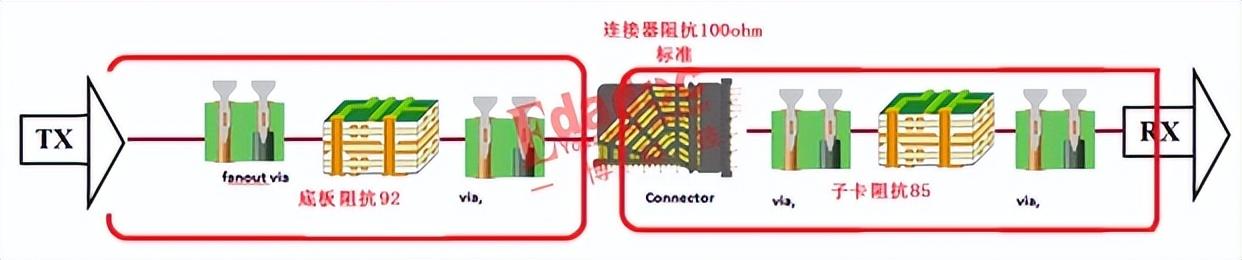

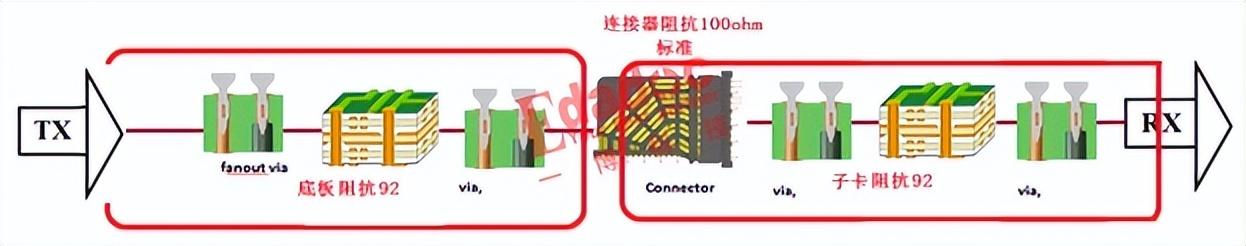

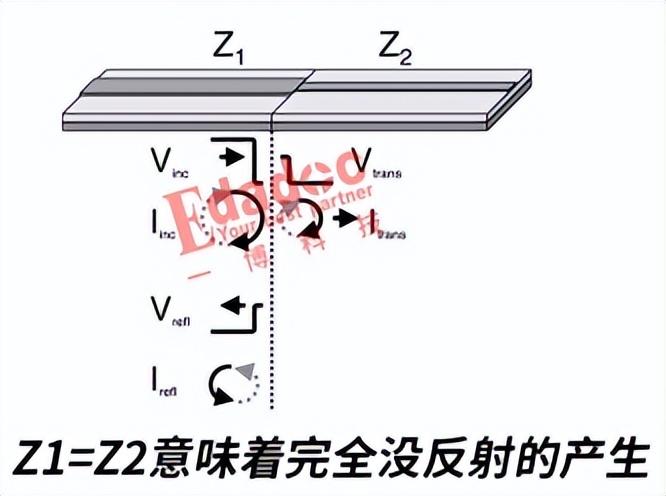

根據上文測試的結果,當前子卡85ohm的阻抗要求,連接器阻抗100ohm的標準,底板阻抗又是92ohm的測試結果,按照如下拓撲進行仿真設置。

仿真結果如下,底板阻抗稍微高了一點,子卡阻抗差不多,相當于有點正負偏差在里面,另外加了連接器的模型,連接器的阻抗確實是有點高,和實際測試也比較接近。

可以看到此時由于阻抗的偏差比較大,回損已經壓到協議要求的Spec了,基本上沒什么裕量了。

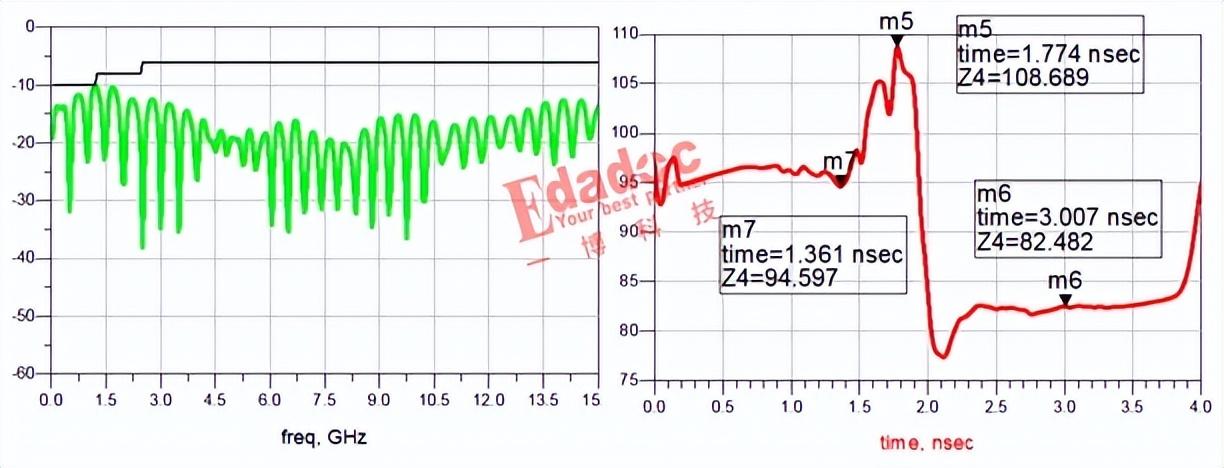

接著我們再來看如果連接器和底板固定,只修改子卡的設計,這樣把子卡的阻抗也按照92ohm來管控,拓撲如下所示:

仿真結果如下所示:

此時回損改善明顯,還有一定的裕量。

這篇文章由于模型的局限,我們只是簡單驗證了一下無源的性能,從無源回損和阻抗一致性兩個方面來看,確實優化后整個系統有一定的改善,后面客戶改版后反饋確實是沒有再發生之前的問題,說明問題已經得到了改善。

今日答題:從系統的角度來看,大家建議高速差分走線按照95甚至92ohm好,還是直接100ohm好?歡迎大家暢所欲言。

審核編輯 黃宇

-

無源

+關注

關注

0文章

83瀏覽量

15036 -

PCIe

+關注

關注

15文章

1262瀏覽量

83195 -

阻抗控制

+關注

關注

1文章

55瀏覽量

10674

發布評論請先 登錄

相關推薦

PCIe 6.0 互操作性PHY驗證測試方案

吉事勵微網電纜阻抗模擬系統是什么?

CPM PCIE做RC時如何完成對復位信號的控制

PCIe延遲對系統性能的影響

盤古100 pro開發板

新思科技PCIe 7.0驗證IP(VIP)的特性

差分阻抗為什么是100歐姆

如何簡化PCIe 6.0交換機的設計

深度論證-高速走線控制100歐姆阻抗一定是最好的選擇嗎?

盤古100K開發板

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

PCIe系統阻抗控制85還是100的驗證

PCIe系統阻抗控制85還是100的驗證

評論