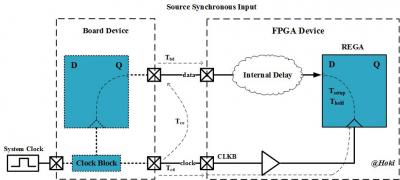

在數字集成電路設計中,Synopsys Design Constraints(SDC)是一種重要的約束語言,用于指導綜合、布局布線等后續流程。本文將詳細講解SDC語法中的set_input_delay和set_output_delay,解釋它們的原理、作用,并通過實例進行說明。

一、set_input_delay和set_output_delay的基本原理

1. 時序約束:在數字集成電路設計中,時序約束是一個重要的概念。它定義了信號從一個時鐘邊沿到另一個時鐘邊沿之間的時間延遲。時序約束有助于確保設計滿足性能要求,如時鐘周期、時鐘偏斜、時鐘抖動等。

2. set_input_delay和set_output_delay:在SDC語法中,set_input_delay和set_output_delay是兩種常用的時序約束命令。它們分別用于設置輸入信號的建立時間和保持時間,以及輸出信號的建立時間和保持時間。

3. 建立時間和保持時間:在時序分析中,建立時間和保持時間是兩個關鍵參數。建立時間是指信號從低電平跳變到高電平,并在時鐘邊沿之后保持一段時間的最小要求。保持時間是指信號從高電平跳變到低電平,并在時鐘邊沿之前保持一段時間的最小要求。

二、set_input_delay和set_output_delay的作用

1. 確保信號正確傳輸:通過設置輸入輸出信號的建立時間和保持時間,可以確保信號在時鐘邊沿之前和之后都保持一段時間,從而保證信號的正確傳輸。

2. 優化設計性能:合理的設置輸入輸出信號的建立時間和保持時間,可以優化設計性能,提高電路的可靠性。

3. 支持時序分析:set_input_delay和set_output_delay是時序分析的重要組成部分,有助于確保設計滿足時序要求。

三、set_input_delay和set_output_delay的舉例說明

1. set_input_delay: 假設我們設計了一個簡單的時序電路,包含一個時鐘信號clk和一個輸入信號A。為了確保信號A能夠在時鐘邊沿之前和之后保持一段時間,我們可以使用set_input_delay命令進行設置。

set_input_delay -clock clk -max 2 [get_ports A]這條命令設置了輸入信號A的最大建立時間為2ns,確保信號A在時鐘邊沿之前至少保持2ns。

2. set_output_delay: 同樣,為了確保信號A在時鐘邊沿之后保持一段時間,我們可以使用set_output_delay命令進行設置。

set_output_delay-clockclk-min1[get_portsA]這條命令設置了輸入信號A的最小保持時間為1ns,確保信號A在時鐘邊沿之后至少保持1ns。

四、總結

set_input_delay和set_output_delay是SDC語法中常用的時序約束命令,它們有助于確保信號的正確傳輸,優化設計性能,并支持時序分析。通過合理的設置輸入輸出信號的建立時間和保持時間,可以提高電路的可靠性。在數字集成電路設計中,了解和使用set_input_delay和set_output_delay是設計者必備的技能。

審核編輯:劉清

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363177 -

SDC

+關注

關注

0文章

49瀏覽量

15580 -

時鐘信號

+關注

關注

4文章

453瀏覽量

28664 -

CLK

+關注

關注

0文章

127瀏覽量

17236

原文標題:深入解析SDC語法中的set_input_delay和set_output_delay

文章出處:【微信號:快樂的芯片工程師,微信公眾號:快樂的芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的IO約束如何使用

Vivado IP核心約束錯誤的解決辦法?

IC中inout port需要同時設置input_delay和output_delay嗎?

input_delay應該設置為多少?

FPGA設計約束技巧之XDC約束之I/O篇 (上)

set_max_delay被覆蓋的解決辦法

Xilinx Vivado I/O延遲約束介紹

時序約束中如何精確找到匹配的template?

FPGA的虛擬時鐘用于什么地方?

創建輸入輸出接口時序約束的竅門

set_output_delay的本質是什么?淺談set_ouput_delay時序

怎樣查看input/output delay是否生效

詳細講解SDC語法中的set_input_delay和set_output_delay

詳細講解SDC語法中的set_input_delay和set_output_delay

評論