高速pcb布線規(guī)則有哪些

高速PCB布線規(guī)則

摘要:隨著電子技術(shù)的快速發(fā)展,高速PCB設(shè)計(jì)變得越來越重要。為了確保信號完整性和電磁兼容性,遵循一定的布線規(guī)則至關(guān)重要。本文將詳細(xì)介紹高速PCB布線規(guī)則,包括信號完整性、電源完整性、電磁兼容性、熱設(shè)計(jì)、布線密度和布線長度等方面的內(nèi)容。

關(guān)鍵詞:高速PCB;布線規(guī)則;信號完整性;電源完整性;電磁兼容性

1. 引言

高速PCB設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心部分,它涉及到信號傳輸、電源分配、電磁兼容性等多個(gè)方面。為了確保高速PCB的性能和可靠性,遵循一定的布線規(guī)則至關(guān)重要。本文將詳細(xì)介紹高速PCB布線規(guī)則,以幫助設(shè)計(jì)者在設(shè)計(jì)過程中遵循最佳實(shí)踐。

2. 信號完整性

信號完整性(Signal Integrity,SI)是指信號在傳輸過程中保持其完整性的能力。為了確保信號完整性,需要遵循以下布線規(guī)則:

2.1 阻抗控制

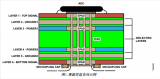

阻抗控制是高速PCB設(shè)計(jì)中的關(guān)鍵因素。為了實(shí)現(xiàn)阻抗控制,需要選擇合適的傳輸線類型(如微帶線、帶狀線等),并確保傳輸線的寬度、間距和介質(zhì)厚度在整個(gè)PCB上保持一致。

2.2 差分信號對

差分信號對可以有效地減少電磁干擾(EMI)并提高信號完整性。在布線時(shí),應(yīng)盡量使差分信號對的長度、間距和走線保持一致,以實(shí)現(xiàn)良好的差分平衡。

2.3 避免過孔

過孔會對信號傳輸產(chǎn)生影響,尤其是在高速信號傳輸中。在設(shè)計(jì)過程中,應(yīng)盡量減少過孔的使用,或者使用盲孔和埋孔技術(shù)來降低過孔對信號完整性的影響。

2.4 信號走線長度匹配

為了降低時(shí)鐘偏斜和時(shí)序錯(cuò)誤,需要對信號走線長度進(jìn)行匹配。在布線時(shí),應(yīng)盡量使關(guān)鍵信號(如時(shí)鐘信號、復(fù)位信號等)的走線長度保持一致。

3. 電源完整性

電源完整性(Power Integrity,PI)是指電源系統(tǒng)在提供穩(wěn)定電源的同時(shí),不產(chǎn)生過多的噪聲。為了確保電源完整性,需要遵循以下布線規(guī)則:

3.1 電源和地平面

在高速PCB設(shè)計(jì)中,應(yīng)使用完整的電源和地平面,以提供穩(wěn)定的電源和良好的信號參考。同時(shí),應(yīng)盡量避免在電源和地平面之間布線,以降低噪聲和干擾。

3.2 去耦電容

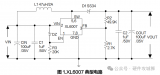

去耦電容可以有效地降低電源噪聲和電磁干擾。在設(shè)計(jì)過程中,應(yīng)在電源輸入處和關(guān)鍵芯片的電源引腳處放置去耦電容,并確保去耦電容的布局和布線滿足高速信號的要求。

3.3 電源分配網(wǎng)絡(luò)

為了確保電源的穩(wěn)定性和可靠性,應(yīng)設(shè)計(jì)合適的電源分配網(wǎng)絡(luò)(Power Distribution Network,PDN)。在布線時(shí),應(yīng)盡量使電源分配網(wǎng)絡(luò)的阻抗保持一致,以降低電源噪聲和干擾。

4. 電磁兼容性

電磁兼容性(Electromagnetic Compatibility,EMC)是指電子設(shè)備在電磁環(huán)境中正常工作的能力。為了確保電磁兼容性,需要遵循以下布線規(guī)則:

4.1 減少電磁干擾

在布線時(shí),應(yīng)盡量避免高速信號線與敏感信號線(如模擬信號、時(shí)鐘信號等)并行布線,以降低電磁干擾。同時(shí),可以使用地平面和屏蔽技術(shù)來降低電磁干擾。

4.2 差分信號

如前所述,差分信號可以有效降低電磁干擾。在設(shè)計(jì)過程中,應(yīng)盡量使用差分信號,并確保差分信號對的布局和布線滿足高速信號的要求。

4.3 濾波和屏蔽

在高速PCB設(shè)計(jì)中,可以使用濾波器和屏蔽技術(shù)來降低電磁干擾。例如,可以在電源輸入處添加濾波器,以降低電源噪聲;在關(guān)鍵信號線周圍添加屏蔽層,以降低電磁干擾。

5. 熱設(shè)計(jì)

熱設(shè)計(jì)是高速PCB設(shè)計(jì)中的一個(gè)重要方面。為了確保PCB的可靠性和穩(wěn)定性,需要遵循以下布線規(guī)則:

5.1 散熱通道

在設(shè)計(jì)過程中,應(yīng)考慮PCB的散熱需求,并設(shè)計(jì)合適的散熱通道。例如,可以在PCB的頂部和底部設(shè)置散熱孔,以提高散熱效果。

5.2 熱敏感元件

對于熱敏感元件(如電容、電感等),應(yīng)盡量避免將其放置在高溫區(qū)域,并確保其布局和布線滿足熱設(shè)計(jì)的要求。

5.3 熱隔離

在布線時(shí),應(yīng)盡量避免將熱源(如功率器件、大電流走線等)與熱敏感元件并行布線,以降低熱干擾。

高速PCB布線規(guī)則

摘要:隨著電子技術(shù)的快速發(fā)展,高速PCB設(shè)計(jì)變得越來越重要。為了確保信號完整性和電磁兼容性,遵循一定的布線規(guī)則至關(guān)重要。本文將詳細(xì)介紹高速PCB布線規(guī)則,包括信號完整性、電源完整性、電磁兼容性、熱設(shè)計(jì)、布線密度和布線長度等方面的內(nèi)容。

關(guān)鍵詞:高速PCB;布線規(guī)則;信號完整性;電源完整性;電磁兼容性

1. 引言

高速PCB設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心部分,它涉及到信號傳輸、電源分配、電磁兼容性等多個(gè)方面。為了確保高速PCB的性能和可靠性,遵循一定的布線規(guī)則至關(guān)重要。本文將詳細(xì)介紹高速PCB布線規(guī)則,以幫助設(shè)計(jì)者在設(shè)計(jì)過程中遵循最佳實(shí)踐。

2. 信號完整性

信號完整性(Signal Integrity,SI)是指信號在傳輸過程中保持其完整性的能力。為了確保信號完整性,需要遵循以下布線規(guī)則:

2.1 阻抗控制

阻抗控制是高速PCB設(shè)計(jì)中的關(guān)鍵因素。為了實(shí)現(xiàn)阻抗控制,需要選擇合適的傳輸線類型(如微帶線、帶狀線等),并確保傳輸線的寬度、間距和介質(zhì)厚度在整個(gè)PCB上保持一致。

2.2 差分信號對

差分信號對可以有效地減少電磁干擾(EMI)并提高信號完整性。在布線時(shí),應(yīng)盡量使差分信號對的長度、間距和走線保持一致,以實(shí)現(xiàn)良好的差分平衡。

2.3 避免過孔

過孔會對信號傳輸產(chǎn)生影響,尤其是在高速信號傳輸中。在設(shè)計(jì)過程中,應(yīng)盡量減少過孔的使用,或者使用盲孔和埋孔技術(shù)來降低過孔對信號完整性的影響。

2.4 信號走線長度匹配

為了降低時(shí)鐘偏斜和時(shí)序錯(cuò)誤,需要對信號走線長度進(jìn)行匹配。在布線時(shí),應(yīng)盡量使關(guān)鍵信號(如時(shí)鐘信號、復(fù)位信號等)的走線長度保持一致。

3. 電源完整性

電源完整性(Power Integrity,PI)是指電源系統(tǒng)在提供穩(wěn)定電源的同時(shí),不產(chǎn)生過多的噪聲。為了確保電源完整性,需要遵循以下布線規(guī)則:

3.1 電源和地平面

在高速PCB設(shè)計(jì)中,應(yīng)使用完整的電源和地平面,以提供穩(wěn)定的電源和良好的信號參考。同時(shí),應(yīng)盡量避免在電源和地平面之間布線,以降低噪聲和干擾。

3.2 去耦電容

去耦電容可以有效地降低電源噪聲和電磁干擾。在設(shè)計(jì)過程中,應(yīng)在電源輸入處和關(guān)鍵芯片的電源引腳處放置去耦電容,并確保去耦電容的布局和布線滿足高速信號的要求。

3.3 電源分配網(wǎng)絡(luò)

為了確保電源的穩(wěn)定性和可靠性,應(yīng)設(shè)計(jì)合適的電源分配網(wǎng)絡(luò)(Power Distribution Network,PDN)。在布線時(shí),應(yīng)盡量使電源分配網(wǎng)絡(luò)的阻抗保持一致,以降低電源噪聲和干擾。

4. 電磁兼容性

電磁兼容性(Electromagnetic Compatibility,EMC)是指電子設(shè)備在電磁環(huán)境中正常工作的能力。為了確保電磁兼容性,需要遵循以下布線規(guī)則:

4.1 減少電磁干擾

在布線時(shí),應(yīng)盡量避免高速信號線與敏感信號線(如模擬信號、時(shí)鐘信號等)并行布線,以降低電磁干擾。同時(shí),可以使用地平面和屏蔽技術(shù)來降低電磁干擾。

4.2 差分信號

如前所述,差分信號可以有效降低電磁干擾。在設(shè)計(jì)過程中,應(yīng)盡量使用差分信號,并確保差分信號對的布局和布線滿足高速信號的要求。

4.3 濾波和屏蔽

在高速PCB設(shè)計(jì)中,可以使用濾波器和屏蔽技術(shù)來降低電磁干擾。例如,可以在電源輸入處添加濾波器,以降低電源噪聲;在關(guān)鍵信號線周圍添加屏蔽層,以降低電磁干擾。

5. 熱設(shè)計(jì)

熱設(shè)計(jì)是高速PCB設(shè)計(jì)中的一個(gè)重要方面。為了確保PCB的可靠性和穩(wěn)定性,需要遵循以下布線規(guī)則:

5.1 散熱通道

在設(shè)計(jì)過程中,應(yīng)考慮PCB的散熱需求,并設(shè)計(jì)合適的散熱通道。例如,可以在PCB的頂部和底部設(shè)置散熱孔,以提高散熱效果。

5.2 熱敏感元件

對于熱敏感元件(如電容、電感等),應(yīng)盡量避免將其放置在高溫區(qū)域,并確保其布局和布線滿足熱設(shè)計(jì)的要求。

5.3 熱隔離

在布線時(shí),應(yīng)盡量避免將熱源(如功率器件、大電流走線等)與熱敏感元件并行布線,以降低熱干擾。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

布線

+關(guān)注

關(guān)注

9文章

777瀏覽量

84428 -

高速PCB

+關(guān)注

關(guān)注

4文章

94瀏覽量

25090

發(fā)布評論請先 登錄

相關(guān)推薦

高速信號線走線規(guī)則有哪些

在高速數(shù)字電路設(shè)計(jì)中,信號完整性(SI)是確保系統(tǒng)性能和可靠性的核心要素。高速信號線的走線規(guī)則對于維持信號質(zhì)量、減少噪聲干擾以及優(yōu)化時(shí)序性能至關(guān)重要。本文將深入探討高速信號線走線的關(guān)鍵

104條關(guān)于PCB布局布線的小技巧

在電子產(chǎn)品設(shè)計(jì)中,PCB布局布線是重要的一步,PCB布局布線的好壞將直接影響電路的性能。 現(xiàn)在,雖然有很多軟件可以實(shí)現(xiàn)PCB自動布局

高速PCB設(shè)計(jì)EMI防控手冊:九大關(guān)鍵步驟詳解

一站式PCBA智造廠家今天為大家講講高速PCB設(shè)計(jì)EMI有什么規(guī)則?高速PCB設(shè)計(jì)EMI九大關(guān)鍵規(guī)則

PCB可制造性設(shè)計(jì):開啟高效生產(chǎn)的鑰匙

設(shè)計(jì)規(guī)則方面 1.布線規(guī)則 ①.線寬和間距需要合理設(shè)置。線寬要根據(jù)電流大小確定,以避免線路過熱。同時(shí),線間距應(yīng)考慮電氣絕緣要求和制造工藝能力,防止短路。例如,在高密度布線區(qū)域,線間距不能過小,否則會增加制造難度。 ②.

了解TI基于PCB布線規(guī)則的DDR時(shí)序規(guī)范

電子發(fā)燒友網(wǎng)站提供《了解TI基于PCB布線規(guī)則的DDR時(shí)序規(guī)范.pdf》資料免費(fèi)下載

發(fā)表于 10-15 11:47

?1次下載

如何理解PCB設(shè)計(jì)的爬電距離?

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)爬電距離要求與走線規(guī)則有哪些?PCB設(shè)計(jì)爬電距離要求與走線規(guī)則。在PCB設(shè)計(jì)中,爬電距離和走

高速ADC PCB布局布線技巧分享

在高速模擬信號鏈設(shè)計(jì)中,印刷電路板(PCB)布局布線需??要考慮許多選項(xiàng),有些選項(xiàng)比其它選項(xiàng)更重要,有些選項(xiàng)??則取決于應(yīng)用。最終的答案各不相同,但在所有情況下,??設(shè)計(jì)工程師都應(yīng)盡量消除最佳做法

非常實(shí)用的PCB布局布線規(guī)則,畫出美而高性能的板子

網(wǎng)絡(luò)規(guī)則

在高速數(shù)字電路中,當(dāng)PCB布線的延遲時(shí)間大于信號上升時(shí)間(或下降時(shí)間) 的1/4時(shí),該布線即可以看成傳輸線,為了保證信號的輸入和輸

發(fā)表于 07-17 15:43

高速pcb的定義是什么

高速pcb的定義是什么 高速PCB(Printed Circuit Board,印刷電路板)是指在高速信號傳輸、高頻應(yīng)用和高密度布局等方面具

射頻PCB走線規(guī)則簡析

射頻(RF)PCB走線規(guī)則是確保無線通信設(shè)備性能的關(guān)鍵因素之一。在高頻信號設(shè)計(jì)中,PCB走線不僅承載著電流,還對信號的完整性和質(zhì)量有著顯著影響。

pcb電源布線規(guī)則分享 PCB電源布線的六大技巧

PCB電源布線是印刷電路板設(shè)計(jì)中非常重要的一環(huán)。電源布線的好壞直接影響到電路的穩(wěn)定性和性能。本文將介紹幾個(gè)PCB電源布線的技巧,幫助大家在設(shè)

發(fā)表于 05-16 11:50

?2197次閱讀

BOOST拓?fù)?b class='flag-5'>PCB布線規(guī)則

對于開關(guān)電源來說,輸入端通常采用電解電容與陶瓷電容組合使用(主要是經(jīng)濟(jì)實(shí)惠),電容具有儲能與濾波作用,電解電容給芯片提供瞬態(tài)電流,確保輸入端電壓不出現(xiàn)較大波動,陶瓷電容用來濾除輸入端高頻毛刺電壓,給芯片內(nèi)部邏輯電路提供純凈電源。

發(fā)表于 02-28 13:46

?1310次閱讀

如何優(yōu)化 PCB 布線規(guī)則?

本文要點(diǎn)在PCB布線中不使用規(guī)則可能會出現(xiàn)的問題。設(shè)計(jì)中可使用的不同類型PCB布線規(guī)則。如何在PCB

高速pcb布線規(guī)則有哪些

高速pcb布線規(guī)則有哪些

評論