在開始閱讀本系列文章之前,請先參閱《有關CR52 MPU配置說明》。因為這篇文章講述了,cache配置所涉及到的寄存器的設置和MPU的一些基本概念。如果讀者都已經理解了上述內容,可以跳過。本章內容主要講述cache屬性的具體含意、注意事項、以及在RZ/T2M的性能測試。

RZ/T2M cache的相關說明

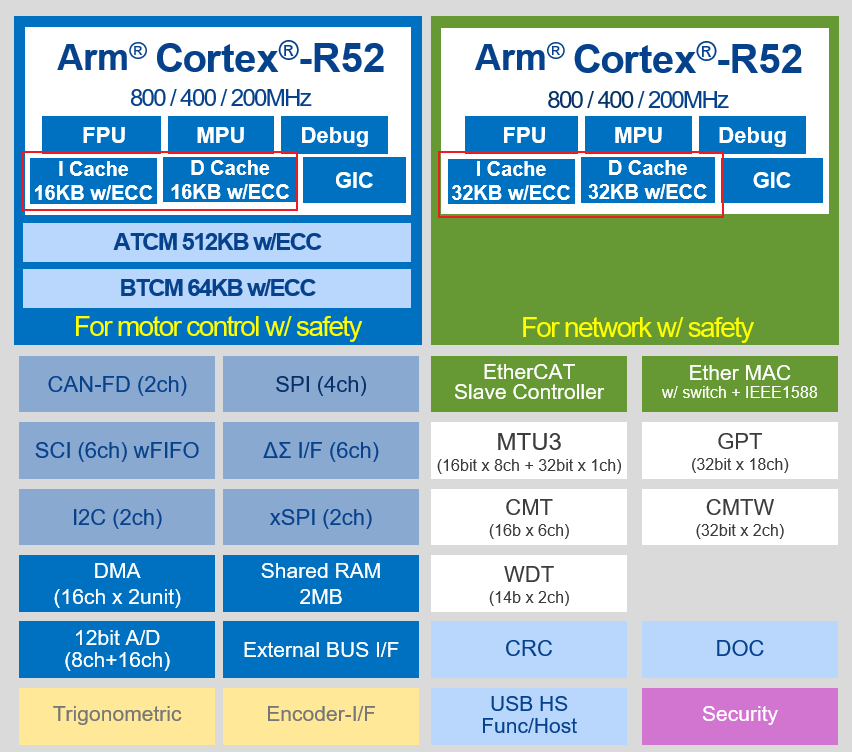

RZ/T2M用的Cortex-r52內核芯片做了一級Cache支持,Cache又分數據緩存D-Cache和指令緩存I-Cache,RZ/T2M cpu0的數據緩存和指令緩存大小都是16KB,cpu1的數據緩存和指令緩存大小都是32KB。對于指令緩存,用戶不必過于關注,對于有執行效率要求的代碼,盡量放在TCM或者使能cache的SRAM區域。這里主要說的是數據緩存D-Cache。如果Rzt2m主頻是400MHz,TCM和Cache都以400MHz工作,但是如果主頻是800MHz,那么TCM必須有一個指令周期的等待。也就是說TCM的工作頻最高就是400MHz,而cache的工作頻與CPU主頻一致。

這就是為什么當用戶代碼比較小的時候,如果代碼放在SRAM,但是代碼又大部分被cache緩存了,在CPU的主頻是800MHz的情況下,此時代碼的執行效率高于TCM的原因。因為cache可以達到800MHz的主頻,而TCM只能達到400MHz。如果CPU主頻是400MHz,在代碼很小的情況下,TCM的性能與SRAM的性能幾乎相當。但是用戶代碼很大又比較復雜的時候,遠超過16KB的緩存大小時,這就要看具體情況另當別論了。

TCM不是本章內容的重點,本章內容重點是SRAM的cache的說明。T2/N2 SRAM的總線頻是200MHz。數據緩存D-Cache就是為了CPU加速訪問SRAM。如果每次CPU要讀寫SRAM區的數據,都能夠在Cache里面進行,自然是最好的,實現了200MHz到400MHz的飛躍,實際是做不到的,因為數據Cache大小是有限的,總有用完的時候。

RZ/T2M系統框圖

Cache相關概念

對際cache的操作主要分讀寫兩種情況:

1Read操作

如果CPU要讀取的SRAM區域的數據在Cache中已經加載好了,這就叫讀命中(Cache hit)。讀命中的情況下,自然效率是高的。但是如果cache里面沒有,這就是所謂的cache miss,那么就要從SRAM里面加載,然后再讀取。

2Write操作

如果CPU要寫的SRAM區域數據在cache中已經開辟了對應的區域,這就叫寫命中,如果Cache里面沒有開辟對應的區域,這就是寫cache miss了。

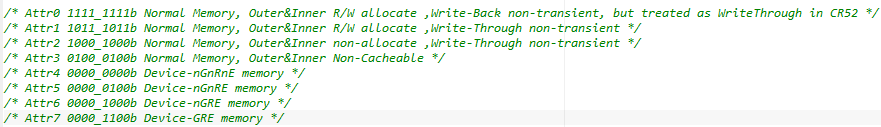

Cache的配置是通過MPU來設置的,通常用到以下幾種方式:

左右滑動查看完整內容

長按可保存查看大圖

對上述的幾種方式說明一下:

1Normal Memory

通常我們用的塊存儲設備,可讀,可寫或者只讀。

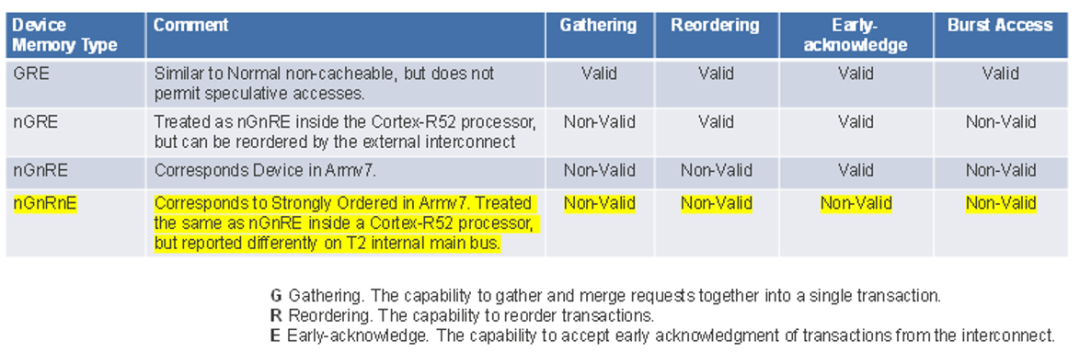

2Device

這通常用于外圍設備,這些外圍設備可能對讀敏感或對寫敏感。這個Arm體系結構限制了對設備內存的訪問的排序、合并或推測。比如FPGA,這里的排序,合并和推測請看下表的解釋。內容不在本章展開說明。下表對GRE,nGRE,nGnRE…等概念都有具體說明,相關的GRE的屬性也都有說明。

點擊可查看大圖

-

內核

+關注

關注

3文章

1382瀏覽量

40422 -

瑞薩

+關注

關注

35文章

22310瀏覽量

86744 -

Cortex

+關注

關注

2文章

203瀏覽量

46599

原文標題:解密Cortex R52內核Cache:操作實踐、性能測試與深度解析(1)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

東芝推出七款基于Arm Cortex-M4內核的32位微控制器

實際項目開發中為何選擇ARM? Cortex?-M4 內核的HK32MCU?

Arm Cortex-R82AE賦能高性能區域控制器設計

RM57L843基于ARM? Cortex?-R內核的Hercules?微控制器數據表

TMS570LC4357基于ARM Cortex?-R內核的Hercules?微控制器數據表

摩芯半導體與安謀科技達成合作

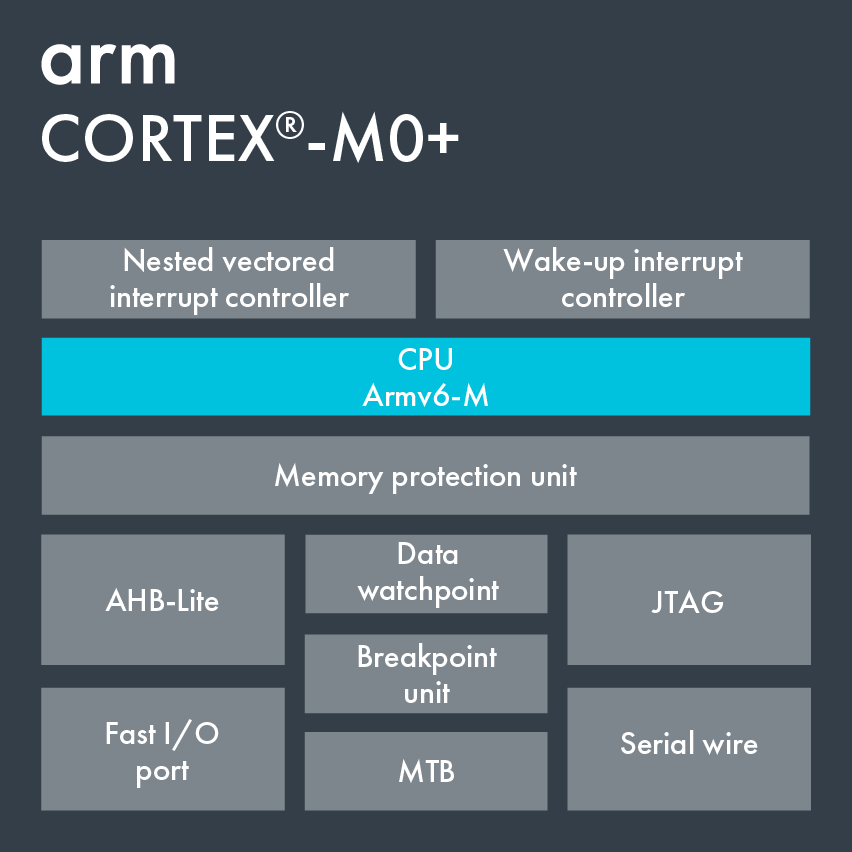

Cortex-M0+內核介紹

兆易創新推出GD32F5系列Cortex-M33內核MCU

Cortex-M85內核單片機如何快速上手

Linux內核內存管理之slab分配器

Cortex R52內核Cache的相關概念(1)

Cortex R52內核Cache的相關概念(1)

評論