今天我們看的這篇論文介紹了在多FPGA集群上實現高級并行編程的研究,其主要目標是為非FPGA專家提供一個成熟且易于使用的環境,以便在多個并行運行的設備上擴展高性能計算(HPC)應用。

背景

該論文的研究背景集中在解決高性能計算(HPC)領域中利用現場可編程門陣列(FPGA)進行并行計算的挑戰。由于FPGA在HPC領域相對新穎,尚未形成一個成熟的生態系統,能夠方便非FPGA專家在多個FPGA設備上擴展并行應用程序。論文指出,盡管FPGA具備高性能計算潛力,但在實際應用中,缺乏一種有效的方法讓非專業人士能夠輕松地利用FPGA的并行處理能力。

FPGA在HPC領域的新興地位:FPGA技術在HPC中尚未得到充分開發,尤其是在構建大規模并行計算環境方面。

并行編程的復雜性:直接編程FPGA通常需要深入的硬件知識,這對非FPGA工程師來說是一個重大障礙。

缺乏成熟的工具和平臺:與傳統的CPU或GPU相比,用于FPGA的編程工具和平臺不夠成熟,難以支持大規模的并行應用開發。

基于上述背景,論文旨在開發一種更友好的編程模型和平臺,使得非FPGA工程師也能利用FPGA的并行計算能力,特別是在多FPGA集群的環境下。這涉及到創建一個支持消息傳遞接口(MPI)風格通信的軟件堆棧,以及一個能夠跨多臺FPGA設備進行高效并行計算的編程環境。此外,論文還提到了評估這一新環境的性能和效率,特別是在與傳統超級計算機的比較中,特別是在能耗比方面。

FPGA design

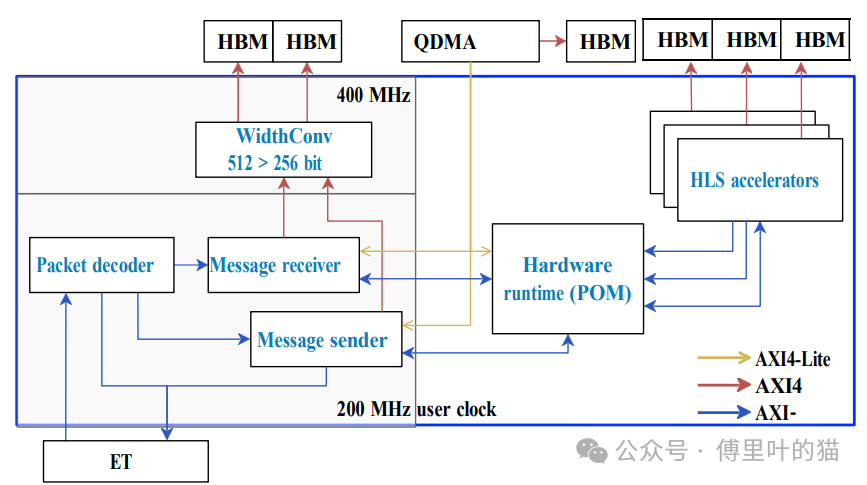

論文中關于FPGA設計的部分描述了一個高度優化的架構,旨在促進高級并行編程在多FPGA集群上的實現。

設計組成:

用戶應用:這部分包含High-Level Synthesis (HLS) 加速器和運行時,它們與FPGA的High Bandwidth Memory (HBM) 和以太網開關接口進行交互。

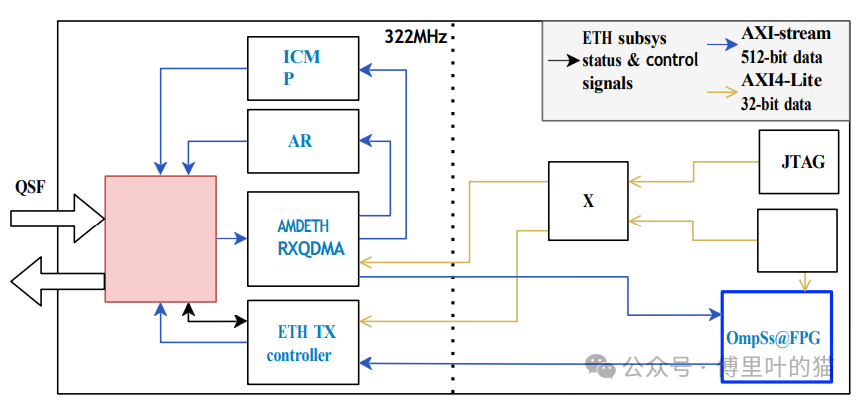

以太網子系統:這個子系統負責處理以太網頭信息和尋址系統,為應用程序提供一個簡單的流式接口,用于發送和接收網絡消息。

用戶應用與內存互聯:

設計中包括POM運行時(Pico OmpSs Manager),HLS加速器,以及與內存的互聯機制。

OMPIF運行時被添加到設計中,它連接到以太網接口,允許消息發送者接收來自POM的任務,并處理用戶傳遞的參數。

通信架構:

每個FPGA有兩個QSFP28端口,其中一個連接到以太網交換機,另一個連接到鄰近的FPGA,但設計依賴于與交換機相連的端口,以實現整個集群的完全連通性。

自動化設計生成:

FPGA設計和架構可以自動由Accelerator Integrator Tool (AIT)生成,該工具只需用戶HLS代碼作為輸入。

AIT是OmpSs@FPGA框架的一部分,框架還包括Xtasks庫和Nanos6運行時,用于處理FPGA設置、管理和通信。

以太網接口的抽象層:

為了使用以太網接口,設計中加入了一個抽象層,它簡化了網絡消息的發送和接收,使應用程序無需關心底層以太網協議細節。

HBM使用:

FPGA設計充分利用HBM,這是現代FPGA提供的一種高速存儲解決方案,可以顯著提高數據吞吐量和訪問速度。

硬件與軟件協同:

硬件設計與軟件棧緊密配合,使得用戶可以專注于編寫基于任務和消息傳遞的高級并行代碼,而低級別的細節(如以太網、PCIe和JTAG管理)則對程序員透明。

SOFTWARE STACK

論文中描述的軟件堆棧是為了使多FPGA集群的管理與使用更加高效和便捷,特別是對于那些基于高級并行編程模型的應用程序。

Xtasks遠程支持:

Xtasks庫是OmpSs@FPGA框架的一部分,用于卸載任務到FPGA加速器,并在FPGA和主機內存之間復制數據。

新增了對遠程FPGA節點的支持,這通過Xtasks遠程實現,它能描述集群中所有FPGA節點,無論本地還是遠程,以及一個名為Xtasks服務器的應用程序。

這種改進使得從單個CPU服務器可以管理整個FPGA集群,無論是通過本地PCIe還是通過網絡。

Nanos6運行時:

Nanos6運行時用于分析任務依賴性和調度可并行執行的任務,它是OmpSs-2任務基礎編程模型的核心。

在FPGA上下文中,Nanos6運行時通過Xtasks庫管理FPGA的設置、任務調度和通信。

OMPIF集成:

OMPIF(Open MPI over FPGA)是一種通信協議,允許類似MPI(Message Passing Interface)的通信模式在FPGA上運行。

這一集成使得C/C++代碼能夠在FPGA上運行,并且能夠調用類似于MPI_Send/Recv的功能,通過MEEP集群的100Gb以太網網絡進行消息傳遞。

MEEP Manager:

提供了一個統一的界面來管理FPGA集群,包括加載位流、配置設備和傳輸數據到遠程CPU節點所托管的FPGAs。

自動化工具:

Accelerator Integrator Tool (AIT)用于自動生成FPGA設計和架構,只需要用戶提供的HLS代碼作為輸入。

整體而言,軟件堆棧提供了一套完整的解決方案,使得非FPGA工程師也能夠利用多FPGA集群來擴展他們的應用,同時避免了與低級別硬件交互相關的復雜性。通過這一堆棧,程序員可以專注于編寫基于任務和消息傳遞的高級并行代碼,而無需擔心底層的以太網、PCIe或JTAG管理等技術細節。此外,堆棧還提供了對遠程FPGA節點的管理能力,從而增強了集群的靈活性和可擴展性。

EVALUATION

在論文的評估(Evaluation)部分,作者們展示了他們構建的多FPGA集群——Marenostrum Exascale Emulation Platform (MEEP)的性能,特別是在高帶寬通信和高性能計算(HPC)應用方面。

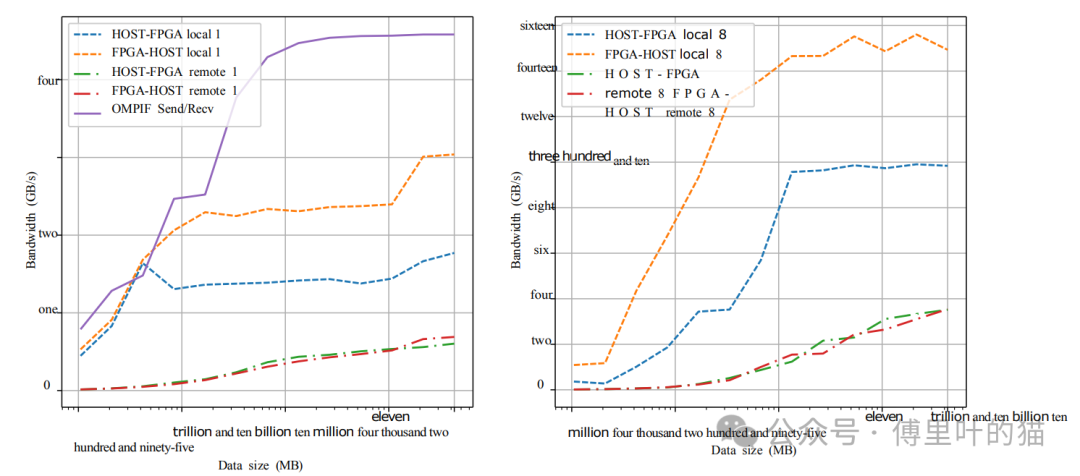

帶寬測量:

使用OMPIF (Open MPI over FPGA)在兩個FPGA之間測得的帶寬最高可達約4.5GB/s,當數據量約為100MB時。

主機到FPGA以及反向的通信,包括本地(僅PCIe)和遠程(PCIe+網絡)的組合,顯示了不同的帶寬特性。在遠程情況下,由于數據需要通過網絡傳輸,因此帶寬會受到顯著影響。

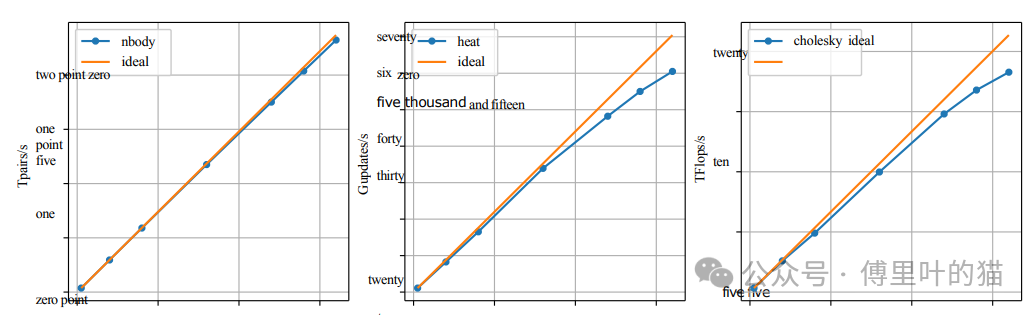

性能評估:

對三個基準測試進行了評估:N-body模擬、Heat擴散模擬(使用Gauss-Seidel求解器)和Cholesky分解。

N-body基準測試使用了4194304個粒子和16個步驟,在64個FPGA上的表現接近理想,效率達到98%,達到每秒2.3G對力的計算。

Heat基準測試展示了熱傳導在二維矩陣上的模擬,使用Gauss-Seidel方法計算每個位置的平均值。結果顯示,該應用能夠有效利用FPGA資源,處理大量的依賴關系。

與HPC的比較:

將MEEP集群的性能與MareNostrum 4超級計算機進行了對比,發現在N-body和Heat基準測試中,MEEP的性能功耗比分別提高了2.3倍和3.5倍。

這些結果表明,MEEP集群在處理大規模并行計算任務時具有顯著的優勢,尤其是在功耗效率方面。同時,該評估證明了使用OMPIF和100Gb以太網網絡在FPGA集群間實現高速通信的可行性。通過使用先進的硬件和優化的軟件堆棧,研究人員能夠展示出FPGA集群在HPC領域的潛力,尤其是在要求高性能和高效率的應用場景中。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605984 -

gpu

+關注

關注

28文章

4774瀏覽量

129350 -

編程

+關注

關注

88文章

3637瀏覽量

93980 -

HPC

+關注

關注

0文章

324瀏覽量

23853

原文標題:多FPGA集群上的High-Level并行編程

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于SMP集群的混合并行編程模型研究

基于微機集群系統的MPI并行計算

并行CRC在FPGA上的實現研究

如何在工程應用中合理采用并行編程技術

如何使用OpenCL輕松實現FPGA應用編程

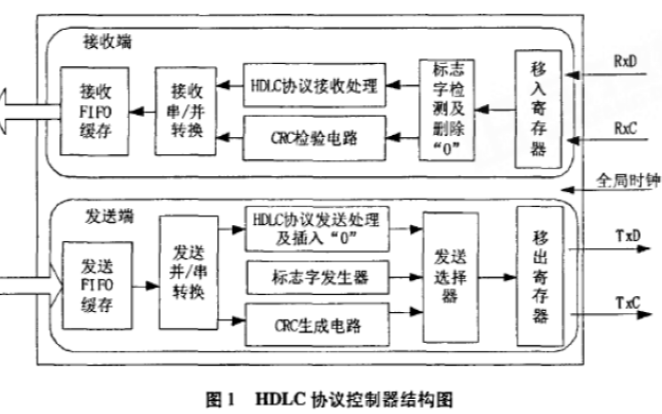

如何使用FPGA實現HDLC協議控制器

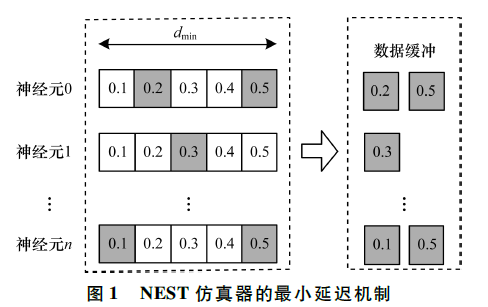

基于FPGA集群的NEST脈沖神經網絡仿真器

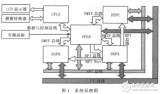

在多FPGA集群上實現高級并行編程

在多FPGA集群上實現高級并行編程

評論