采用Σ-Δ ADC,你可以自由選擇sinc濾波器延遲或輸出數據保真度。抽取率較高時,延遲較長,但信號質量較高;抽取率較低時則相反。這種靈活性對于電機控制算法設計十分有利。通常,算法的某些部分對延遲敏感,而對反饋精度較不敏感。其它部分適合在較低動態特性和較高精度下工作,但對延遲較不敏感。

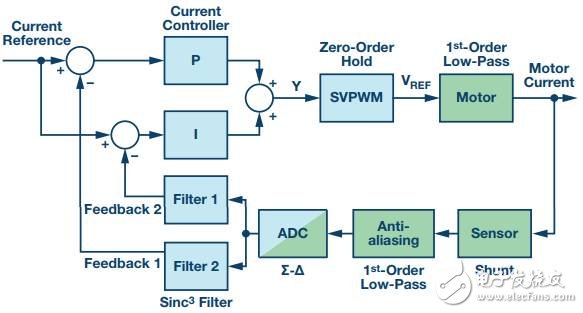

舉個例子,考慮圖1 (a)所示的常規比例積分控制器(PI)。 P部分和 I 部分采用相同的反饋信號工作,意味著該信號的動態特性必須適合兩種控制路徑。不過,P路徑和I路徑可以分離,如圖1 (b)所示。由此還可以再前進一小步,圖1 (c)顯示P路徑和I路徑分離,并且采用具有不同動態特性的反饋信號工作。

圖1. PI控制器方案

*(a)常規方案

*(b) P路徑和I路徑分離

*(c) P路徑和I路徑分離且反饋分離

P部分的任務是抑制快速負載變化和快速速度變化,但精度不是主要考慮。換言之,低抽取率和短延遲的sinc濾波器對P部分有利。I部分的任務是確保穩態性能穩定且精確,它要求高精度。因此,高抽取率和較長延遲的sinc濾波器對I部分有利。這就產生了圖2所示的實現方案。

圖2. 雙sinc濾波器和分離的電流控制器 P 路徑和 I 路徑

電機相電流由一個傳感器(分流電阻)測量,并流經一個抗混疊濾波器,供應給Σ-Δ ADC。然后,1位數據流輸入兩個sinc濾波器,一個針對P控制器調諧,另一個針對I控制器調諧。

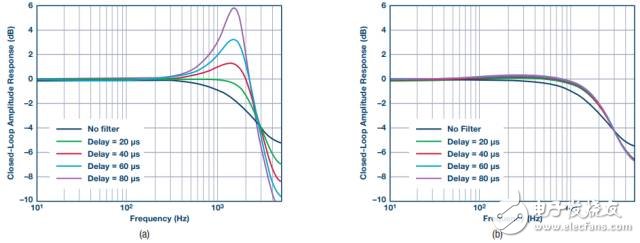

為了評估電流反饋分為兩條路徑的影響,我們對該閉環執行了穩定性分析。對于傳統的Z域分析,sinc濾波器會帶來問題。它會引入一個延遲,對于任何實際抽取率,該延遲小于一個采樣周期。例如,若系統以fsw = 10 kHz的速率運行,濾波器延遲將短于100 μs。從控制環路方面看,sinc模塊是一個小數延遲濾波器。為了模擬小數延遲,將sinc濾波器近似看作一個全通濾波器。在最高為奈奎斯特頻率一半的較低頻率時,該近似處理是精確的,但在更高的頻率,其與理想濾波器有一些偏差。然而,這里的目的是了解雙反饋如何影響環路穩定性,就此而言,該近似是合適的。

作為對比,圖3(a)顯示了反饋路徑(無雙反饋)中僅使用一個sinc濾波器時的閉環幅度響應。開關頻率fsw為10 kHz,奈奎斯特頻率設置為5 kHz。在這些系統參數下,對于0 μs至80 μs的sinc濾波器群延遲,繪制閉環響應曲線。注意,群延遲與抽取率直接相關。同預期一樣,低抽取率和群延遲對閉環穩定性的影響很小,但隨著延遲增加,系統阻尼變得越來越小。

圖3. 雙反饋對電流控制性能的影響,(a) sinc濾波器為P控制器和I控制器共用,(b) P控制器和I控制器分別使用單獨的sinc濾波器

現在將反饋分離,使P控制器和I控制器具有單獨的路徑,便可獲得圖3 (b)。這種情況下,用于P控制器的sinc濾波器抽取率是固定值,使得群延遲為10 μs。僅I控制器的抽取率發生變化。

從圖3 (b)可看出,提高I控制器的延遲對閉環穩定性的影響非常小。如上所述,可利用這些特性來提高環路的動態和穩態性能。

本文中,使用分離反饋的算法為PI控制器。不過,這只是一個例子,大多數控制系統都有多個算法,根據動態和精度要求調諧反饋對這些算法是有利的。磁通觀測器、前饋控制器和PID控制器的差分部分就是一些例子。

-

電機控制

+關注

關注

3540文章

1896瀏覽量

269253 -

adc

+關注

關注

99文章

6533瀏覽量

545747

原文標題:燒腦丨Σ-Δ ADC對控制性能的影響

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AN-1267: 使用ADSP-CM408F ADC控制器的電機控制反饋采樣時序

數字電機控制的未來:一個MCU上的多個電機、嵌入式AI和高級算法

常用的ADC濾波算法有哪些

在單個C2000?MCU上使用FCL和SFRA進行雙軸電機控制

Σ-Δ型ADC在電機控制算法設計上的應用

Σ-Δ型ADC在電機控制算法設計上的應用

評論