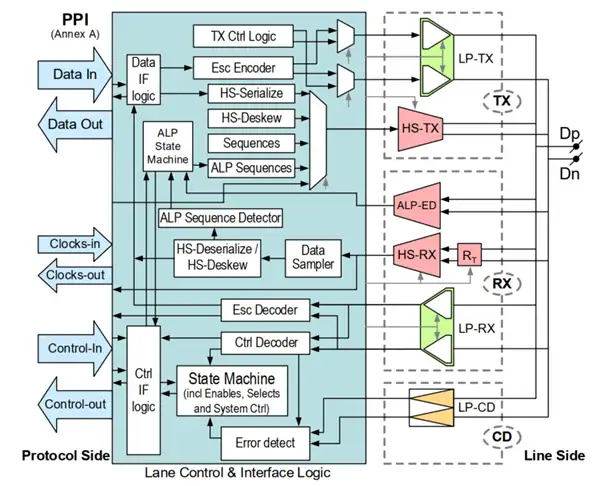

無(wú)論您正在設(shè)計(jì)的處理系統(tǒng)是用于汽車、物聯(lián)網(wǎng),還是用于 VR/AR 應(yīng)用,符合 MIPI 標(biāo)準(zhǔn)的傳感器及顯示器均是實(shí)現(xiàn)可擴(kuò)展性、高抗噪性及高抖動(dòng)容限的必要條件。此外,他們的高速度和低功耗模式也是獲得最佳功耗性能平衡的關(guān)鍵。然而,使用外部橋接器芯片或 PHY 會(huì)增加材料清單成本(BOM),甚至?xí)谀承?yīng)用中引起合規(guī)性問題。為此,可借助集成 1.5Gb/s MIPI 標(biāo)準(zhǔn) I/O 的 Zynq UltraScale+ MPSoC 和 Kintex UltraScale+ FPGA 等符合 MIPI 標(biāo)準(zhǔn)的處理平臺(tái)移除外部 MIPI 橋接器。

Xilinx UltraScale+ 器件提供:

-

高達(dá) 1.5Gb/s 的 MIPI D-PHY 本地操作

-

業(yè)界最佳單位功耗性能比的 16nm 可編程邏輯

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122132

原文標(biāo)題:[器件更新] Xilinx UltraScale+ 器件集成 MIPI D-PHY

文章出處:【微信號(hào):xilinx_inc,微信公眾號(hào):賽靈思】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

Gowin MIPI D-PHY RX TX Advance用戶使用指南

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

MIPI和Xilinx MIPI解決方案的介紹

對(duì)于MIPI系列之“D-PHY”的性能分析和介紹以及應(yīng)用

MIPI D-PHY的靜噪措施

IP_數(shù)據(jù)表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_數(shù)據(jù)表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

IP_數(shù)據(jù)表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

IP_數(shù)據(jù)表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_數(shù)據(jù)表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

IP_數(shù)據(jù)表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

Diodes公司推出一款符合MIPI D-PHY 1.2協(xié)議的信號(hào)ReDriver

聚焦MIPI 系列之四:一文盤點(diǎn)D-PHY/C-PHY/M-PHY之架構(gòu)與測(cè)試解決方案

Xilinx UltraScale+ 器件集成 MIPI D-PHY

Xilinx UltraScale+ 器件集成 MIPI D-PHY

評(píng)論