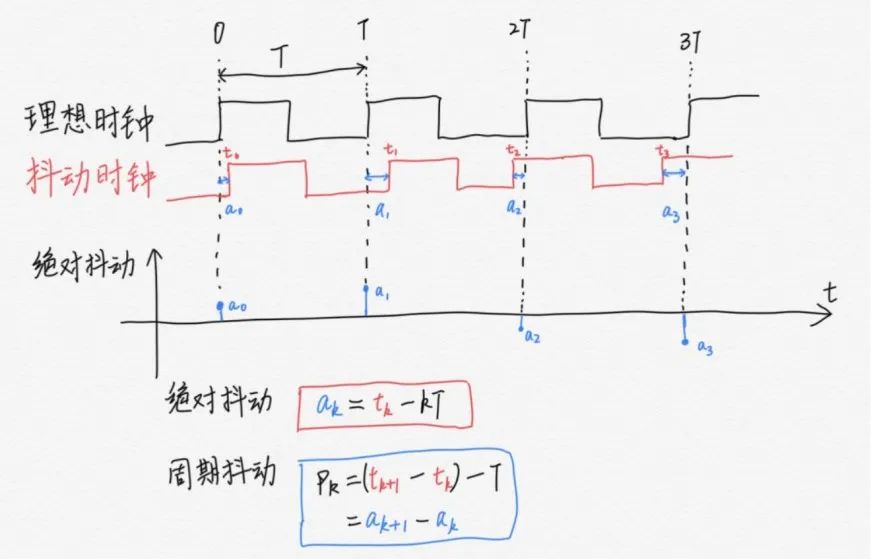

在高速串行通信系統(tǒng)中,CDR(時(shí)鐘數(shù)據(jù)恢復(fù))技術(shù)是實(shí)現(xiàn)數(shù)據(jù)傳輸?shù)年P(guān)鍵技術(shù)之一。然而,CDR電路的設(shè)計(jì)面臨著一個(gè)重要的挑戰(zhàn)——抖動(dòng)。抖動(dòng)現(xiàn)象指的是數(shù)據(jù)信號在實(shí)際傳輸過程中的位置相對于理想位置的偏離。這種偏離可能導(dǎo)致數(shù)據(jù)傳輸錯(cuò)誤,因此,理解和控制抖動(dòng)對于保證通信系統(tǒng)的可靠性至關(guān)重要。

抖動(dòng)通常分為兩種類型:確定性抖動(dòng)和隨機(jī)抖動(dòng)。確定性抖動(dòng)是由多個(gè)因素引起的,包括碼間干擾、串?dāng)_、占空失真以及周期性抖動(dòng)等。這些抖動(dòng)的來源通常是可以預(yù)測的,比如開關(guān)電源引起的干擾。與之相對的是隨機(jī)抖動(dòng),它通常是由半導(dǎo)體器件的熱噪聲引起的,并且難以預(yù)測。

在CDR電路中,傳送參考時(shí)鐘、傳送PLL(相位鎖定環(huán))、串化器以及高速輸出緩沖器等部件都可能對傳送抖動(dòng)產(chǎn)生影響。傳送抖動(dòng)的大小通常用單位間隔的百分比或UI來表示。例如,0.2 UI的傳送抖動(dòng)意味著抖動(dòng)占據(jù)了比特周期的20%。在設(shè)計(jì)中,我們希望這個(gè)數(shù)值盡可能低,因?yàn)楦偷腢I數(shù)值代表更少的抖動(dòng),從而意味著更優(yōu)的信號質(zhì)量。

同樣地,CDR接收器也會有一個(gè)規(guī)格,指明在給定的比特率下它能容忍的最大抖動(dòng)量。一般來說,比特誤碼率的標(biāo)準(zhǔn)設(shè)定為1e-12。接收器的抖動(dòng)容限也用UI來表示,一個(gè)較大的UI值表明接收器能夠容忍更多的抖動(dòng)。例如,0.8 UI的接收抖動(dòng)容限意味著即使80%的比特周期被噪聲占據(jù),接收器仍然能夠可靠地接收數(shù)據(jù)。

抖動(dòng)的量化通常借助于統(tǒng)計(jì)上的鐘形分布來進(jìn)行,該分布的中心點(diǎn)代表了理想的信號邊沿位置。通過這種方式,設(shè)計(jì)人員可以直觀地看到抖動(dòng)對信號質(zhì)量的影響,并據(jù)此進(jìn)行優(yōu)化設(shè)計(jì)。

在面對抖動(dòng)問題時(shí),設(shè)計(jì)人員需要采取一系列措施來確保信號的穩(wěn)定傳輸。首先,選擇合適的電路板材料和布線策略可以減小串?dāng)_和碼間干擾。其次,使用高質(zhì)量的電源和電源濾波器可以減少周期性抖動(dòng)。此外,優(yōu)化PLL的參數(shù)和串化器的設(shè)計(jì)也是降低確定性抖動(dòng)的有效方法。對于隨機(jī)抖動(dòng),雖然難以徹底消除,但可以通過改進(jìn)半導(dǎo)體制程和散熱設(shè)計(jì)來盡量降低其影響。

總之,抖動(dòng)是CDR電路設(shè)計(jì)中的一個(gè)核心挑戰(zhàn),它直接關(guān)系到高速串行通信系統(tǒng)的性能和可靠性。通過深入理解抖動(dòng)的來源和特性,以及采取合理的設(shè)計(jì)措施,可以有效地管理和減輕抖動(dòng)的影響。隨著通信技術(shù)的不斷進(jìn)步,對抖動(dòng)的控制和管理將變得更加重要,這要求設(shè)計(jì)人員不斷創(chuàng)新和優(yōu)化,以實(shí)現(xiàn)更高效、更可靠的數(shù)據(jù)傳輸解決方案。

-

接收器

+關(guān)注

關(guān)注

14文章

2479瀏覽量

72212 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6677文章

2464瀏覽量

205335 -

cdr

+關(guān)注

關(guān)注

1文章

50瀏覽量

18145

發(fā)布評論請先 登錄

相關(guān)推薦

簡談數(shù)字電路設(shè)計(jì)中的抖動(dòng)

SERDES接口電路設(shè)計(jì)

請問如何在具有抖動(dòng)的Artix-7 GTP數(shù)據(jù)流的情況下提高CDR性能?

采用bang-bang PD的CDR電路設(shè)計(jì)常見問題解答

簡談數(shù)字電路設(shè)計(jì)中的抖動(dòng)

基于磁集成的CDR電路

去抖動(dòng)延時(shí)可調(diào)鍵盤電路的設(shè)計(jì)

旋轉(zhuǎn)編碼器抗抖動(dòng)接口電路設(shè)計(jì)

旋轉(zhuǎn)編碼器抗抖動(dòng)接口電路設(shè)計(jì)

簡談數(shù)字電路設(shè)計(jì)中的抖動(dòng)

抖動(dòng)的概念和類型 量化時(shí)域抖動(dòng)、隨機(jī)抖動(dòng)和頻域抖動(dòng)的方法

CDR電路設(shè)計(jì)與抖動(dòng)管理

CDR電路設(shè)計(jì)與抖動(dòng)管理

評論