LDO(Low Dropout Regulator,低壓差線性穩壓器)輸出電壓振蕩是一個復雜的問題,涉及多個方面的因素。以下是對LDO輸出電壓振蕩原因的詳細分析:

一、負反饋機制與相位延遲

LDO通過負反饋機制來調節其輸出電壓,以保持輸出電壓的穩定。然而,當反饋回路中的信號相位延遲達到180°時,負反饋可能轉變為正反饋,從而導致輸出電壓的振蕩。這種相位延遲通常是由于反饋回路中的電容和電阻等元件引起的。

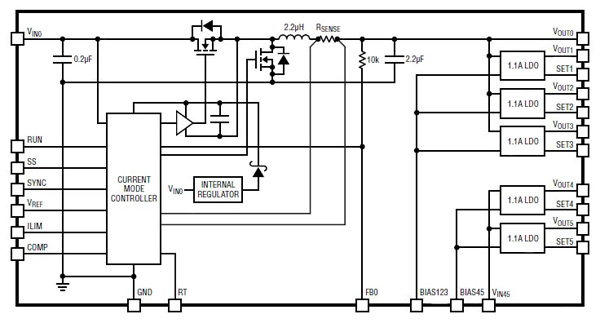

具體來說,LDO包含一個誤差放大器、一個用于輸出晶體管的驅動電路和一個輸出晶體管。這些電路中的電容和電阻構成了反饋回路的一部分,它們會導致信號在傳輸過程中產生延遲。當這個延遲導致的相位偏移達到180°時,原本用于穩定輸出電壓的負反饋信號將變為增強輸出電壓的信號,從而引發振蕩。

二、輸出電容的ESR特性

輸出電容的ESR(Equivalent Series Resistance,等效串聯電阻)特性也是影響LDO輸出電壓穩定性的重要因素。ESR是電容在交流電路中的表現,它反映了電容在高頻下的損耗特性。在LDO電路中,輸出電容的ESR與電路的穩定性密切相關。

如果輸出電容的ESR過大或過小,都可能導致LDO輸出電壓的振蕩。ESR過大時,電容的濾波效果減弱,無法有效抑制輸出電壓的波動;而ESR過小時,則可能使反饋回路的相位裕度減小,導致系統處于不穩定狀態。因此,在設計LDO電路時,需要仔細選擇輸出電容的容值和ESR值,以確保電路的穩定性。

三、負載電流變化

負載電流的變化也是引起LDO輸出電壓振蕩的常見原因。當負載電流突然增加時,LDO需要提供更多的電流來滿足負載需求。然而,由于LDO內部調節機制的反應速度有限,輸出電壓可能無法立即穩定在新的設定值,而是會出現短暫的波動或振蕩。同樣地,當負載電流突然減少時,也可能導致類似的振蕩現象。

為了減小負載電流變化對LDO輸出電壓的影響,可以采取一些措施來優化電路設計。例如,在輸出端并聯一個大容量電容來提供瞬態電流緩沖;或者采用具有快速響應能力的誤差放大器來提高LDO的瞬態響應能力。

四、電路設計問題

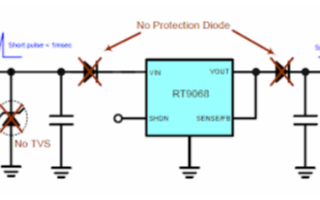

電路設計中的一些問題也可能導致LDO輸出電壓的振蕩。例如,反饋回路中的元件布局不合理、布線過長或存在寄生參數等都可能引入額外的相位延遲和噪聲干擾,從而影響電路的穩定性。此外,如果LDO的輸入電壓和輸出電壓之間存在較大的壓差或輸入電壓波動較大,也可能導致輸出電壓的振蕩。

為了解決這些問題,需要在電路設計時充分考慮各種因素,并采取相應的措施來優化電路設計。例如,合理布局元件、縮短布線長度、減少寄生參數等;同時還需要選擇具有較高電源抑制比(PSRR)和較低噪聲的LDO芯片來降低輸入電壓波動和噪聲對輸出電壓的影響。

五、元件質量問題

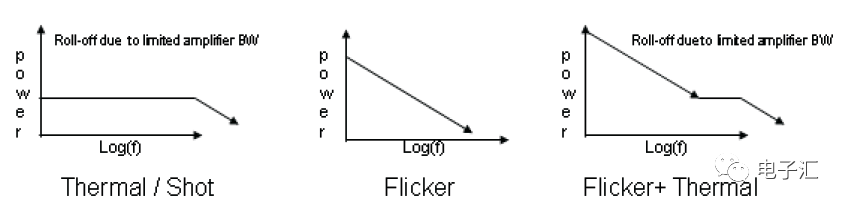

元件的質量問題也可能導致LDO輸出電壓的振蕩。例如,如果輸出電容存在漏電或容量衰減等問題,就可能導致其無法有效濾除輸出電壓中的波動成分;如果誤差放大器存在增益不穩定或噪聲過大等問題,也可能影響LDO的輸出電壓穩定性。

因此,在選擇LDO電路中的元件時,需要選擇質量可靠、性能穩定的產品,并嚴格按照相關規范進行測試和篩選。同時,在使用過程中還需要定期對元件進行檢查和維護,以確保其正常工作并延長使用壽命。

六、外部干擾

外部干擾也是影響LDO輸出電壓穩定性的一個重要因素。例如,電源線、信號線等周圍的電磁干擾可能通過耦合作用進入LDO電路中,引起輸出電壓的波動或振蕩。為了減小外部干擾對LDO輸出電壓的影響,可以采取一些屏蔽和濾波措施來降低干擾信號的幅度和頻率范圍。例如,在電源線和信號線上加裝磁珠或濾波器來抑制高頻噪聲;在LDO電路的輸入和輸出端分別加裝去耦電容和濾波電容來降低低頻噪聲等。

綜上所述,LDO輸出電壓振蕩的原因涉及多個方面的因素,包括負反饋機制與相位延遲、輸出電容的ESR特性、負載電流變化、電路設計問題、元件質量問題以及外部干擾等。為了解決這個問題,需要從多個方面入手進行綜合分析和處理。同時還需要注意在設計和使用過程中嚴格遵守相關規范和標準,以確保LDO電路的穩定性和可靠性。

-

ldo

+關注

關注

35文章

1952瀏覽量

153970 -

線性穩壓器

+關注

關注

5文章

775瀏覽量

66776 -

輸出電壓

+關注

關注

2文章

1122瀏覽量

38299

發布評論請先 登錄

相關推薦

適用于輸入輸出電壓組合的LDO應用

LDO輸出電壓為什么會振蕩

LDO輸出電壓為什么會振蕩

評論