DDS架構基本原理

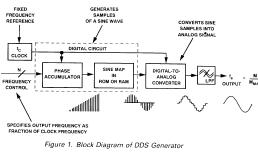

隨著數字技術在儀器儀表和通信系統中的廣泛使用,可從參考頻率源產生多個頻率的數字控制方法誕生了,即直接數字頻率合成(DDS)。其基本架構如圖1所示。該簡化模型采用一個穩定時鐘來驅動存儲正弦波(或其它任意波形)一個或多個整數周期的可編程只讀存儲器(PROM)。隨著地址計數器逐步執行每個存儲器位置,每個位置相應的信號數字幅度會驅動DAC,進而產生模擬輸出信號。最終模擬輸出信號的頻譜純度主要取決于DAC。相位噪聲主要來自參考時鐘。

DDS是一種采樣數據系統,因此必須考慮所有與采樣相關的問題,包括量化噪聲、混疊、濾波等。例如,DAC輸出頻率的高階諧波會折回奈奎斯特帶寬,因而不可濾波,而基于PLL的合成器的高階諧波則可以濾波。此外,還有其它幾種因素需要考慮,稍后將會討論。

圖1:直接數字頻率合成系統的基本原理

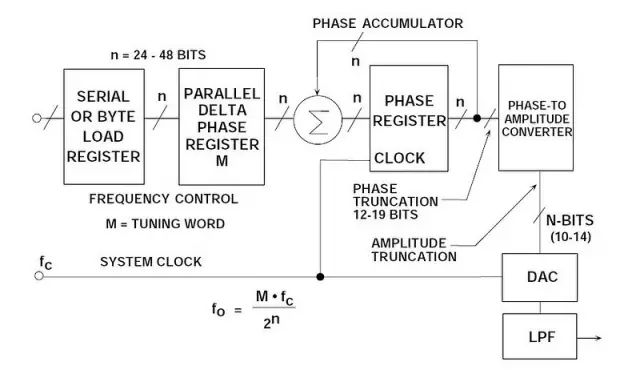

這種簡單DDS系統的基本問題在于,最終輸出頻率只能通過改變參考時鐘頻率或對PROM重新編程來實現,非常不靈活。實際DDS系統采用更加靈活有效的方式來實現這一功能,即采用名為數控振蕩器(NCO)的數字硬件。圖2所示為該系統的框圖。

圖2:靈活的DDS系統

系統的核心是相位累加器,其內容會在每個時鐘周期更新。相位累加器每次更新時,存儲在△相位寄存器中的數字字M就會累加至相位寄存器中的數字。假設△相位寄存器中的數字為00...01,相位累加器中的初始內容為00...00。相位累加器每個時鐘周期都會按00...01更新。如果累加器為32位寬,則在相位累加器返回至00...00前需要232(超過40億)個時鐘周期,周期會不斷重復。

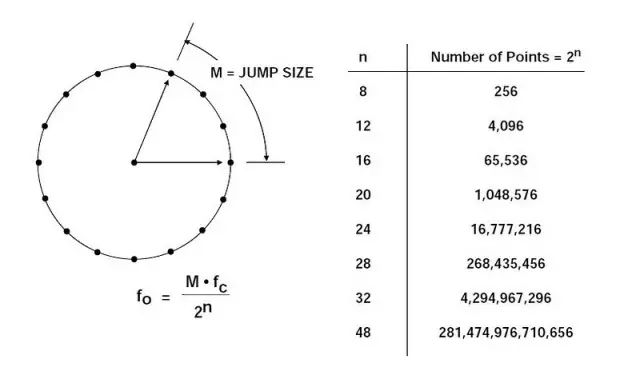

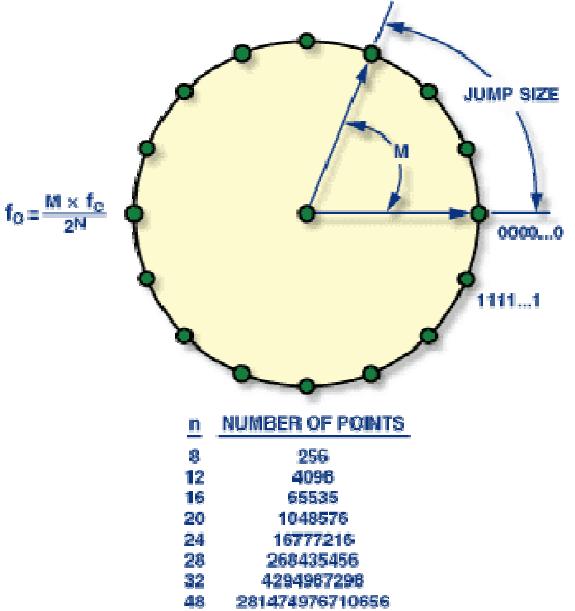

相位累加器的截斷輸出用作正弦(或余弦)查找表的地址。查找表中的每個地址均對應正弦波的從0°到360°的一個相位點。查找表包括一個完整正弦波周期的相應數字幅度信息。(實際上,只需要90°的數據,因為兩個MSB中包含了正交數據)。因此,查找表可將相位累加器的相位信息映射至數字幅度字,進而驅動DAC。圖3用圖形化的“相位輪”顯示了這一情況。

考慮n = 32,M = 1的情況。相位累加器會逐步執行232個可能的輸出中的每一個,直至溢出并重新開始。相應的輸出正弦波頻率等于輸入時鐘頻率232分頻。若M=2,相位累加器寄存器就會以兩倍的速度“滾動”計算,輸出頻率也會增加一倍。以上內容可總結如下:

圖3:數字相位輪

n位相位累加器(大多數DDS系統中,n的范圍通常為24至32)存在2n個可能的相位點。△相位寄存器中的數字字M代表相位累加器每個時鐘周期增加的數量。如果時鐘頻率為fc,則輸出正弦波頻率計算公式為:

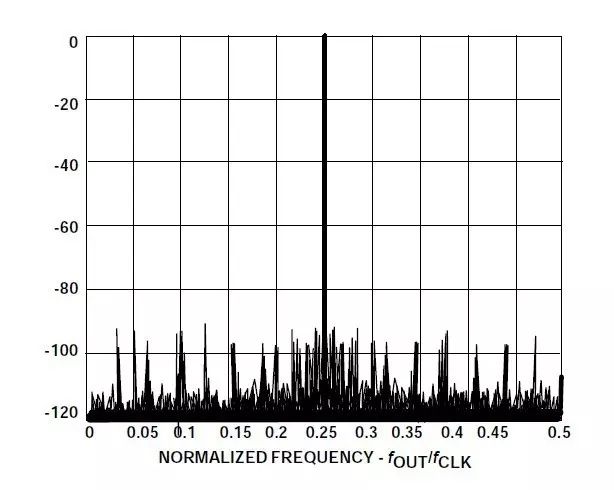

該公式稱為DDS“調諧公式”。注意,系統的頻率分辨率等于fc/2n。n = 32時,分辨率超過40億分之一!在實際DDS系統中,溢出相位寄存器的位不會進入查找表,而是會被截斷,只留下前13至15個MSB。這樣可以減小查找表的大小,而且不會影響頻率分辨率。相位截斷只會給最終輸出增加少量可接受的相位噪聲。(參見圖4)。

圖4:計算得出的輸出頻譜顯示15位相位截斷時90 dB SFDR

DAC的分辨率通常比查找表的寬度少2至4位。即便是完美的N位DAC,也會增加輸出的量化噪聲。圖4顯示的是32位相位累加器15位相位截斷時計算得出的輸出頻譜。選擇M值后,輸出頻率會從0.25倍時鐘頻率開始稍有偏移。注意,相位截斷和有限DAC分辨率產生的雜散都至少比滿量程輸出低90 dB。這一性能遠遠超出了任何商用12位DAC,足以滿足大多數應用的需求。

上述基本DDS系統極為靈活,且具有高分辨率。只需改變M寄存器的內容,頻率就可以立即改變,不會出現相位不連續。但是,實際DDS系統首先需要執行串行或字節加載序列,以將新的頻率字載入內部緩沖寄存器,然后再載入M寄存器。這樣就可以盡可能減少封裝引腳數。新的頻率字載入緩沖寄存器后,并行輸出△相位寄存器就會同步操作,從而同時改變所有位。加載△相位緩沖寄存器所需的時鐘周期數決定了輸出頻率的最大改變速率。

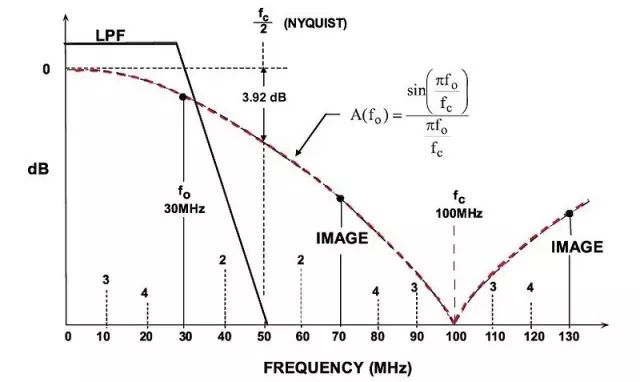

DDS系統中的混疊

簡單DDS系統中可能會產生一種重要的輸出頻率范圍限制。奈奎斯特準則表明,時鐘頻率(采樣速率)必須至少為輸出頻率的兩倍。實際最高輸出頻率限制在約1/3時鐘頻率范圍內。圖5所示為DDS系統中的DAC輸出,其中輸出頻率為30 MHz,時鐘頻率為100 MHz。如圖所示,重構DAC后必須跟隨一個抗混疊濾波器,以消除較低的圖像頻率(100 – 30 = 70 MHz)。

圖5:DDS系統中的混疊

注意,DAC輸出(濾波前)的幅度響應跟隨著一個sin(x)/x響應,在時鐘頻率及其整數倍時,該值為零。歸一化輸出幅度A(fO)的精確計算公式如下:

其中,fO為輸出頻率,fc為時鐘頻率。

出現該滾降的原因是由于DAC輸出并非一系列零寬脈沖(和最佳重新采樣器中一樣),而是一系列矩形脈沖,寬度等于更新速率的倒數。sin(x)/x響應的幅度比奈奎斯特頻率低3.92 dB(DAC更新速率的1/2)。實際上,抗混疊濾波器的傳遞函數可用來補償sin(x)/x滾降,使整體頻率響應相對平坦,達到最大輸出DAC頻率(一般為1/3更新速率)。

另一個重要的考慮因素在于,和基于PLL的系統不同,DDS系統中的基本輸出頻率高階諧波會因混疊而折回至基帶。這些諧波無法通過抗混疊濾波器去除。例如,如果時鐘頻率為100 MHz,輸出頻率為30 MHz,則30 MHz的第二個諧波會出現在60 MHz(帶外),但也會出現在100 – 60 = 40 MHz(混疊成分)。同樣,第三個諧波(90 MHz)會出現在帶內,頻率為100 – 90 = 10 MHz,第四個諧波出現在120 – 100 MHz = 20 MHz。高階諧波也會落在奈奎斯特帶寬內(直流至fc/2)。前4個諧波的位置如圖所示。

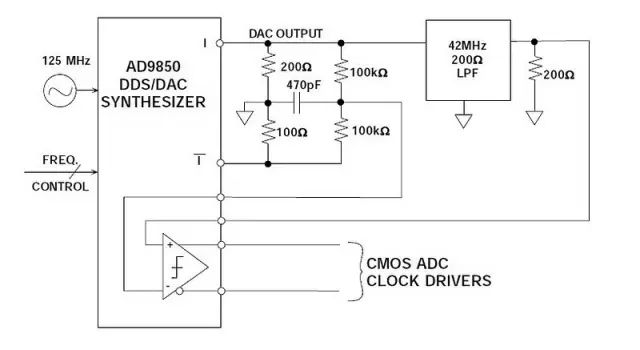

DDS系統(如AD9850)可以提供產生ADC采樣時鐘的出色方法,尤其適合ADC采樣頻率必須受到軟件控制,且鎖定至系統時鐘的情況(參見圖6)。DAC輸出電流IOUT驅動200 Ω、42 MHz的低通濾波器,源和負載阻抗端接,等效負載為100 Ω。濾波器可以消除42 MHz以上的雜散頻率成分。經過濾波的輸出可以驅動AD9850內部比較器的一個輸入端。DAC補償輸出電流可以驅動100 Ω的負載。位于兩個輸出之間的100 kΩ電阻分壓器輸出經過去耦,可以產生參考電壓以供內部比較器使用。

比較器輸出有2 ns的上升和下降時間,可以產生與TTL/CMOS邏輯電平兼容方波。比較器輸出邊緣的抖動小于20 ps rms。輸出和補償輸出均可按要求提供。

圖6:將DDS系統用作ADC時鐘驅動器

在圖6所示的電路中,40 MSPS ADC時鐘的總輸出均方根抖動為50 ps rms,由此產生的信噪比下降在寬動態范圍應用中必須加以考慮。

DDS系統中的幅度調制

DDS系統中的幅度調制可以通過在查找表和DAC輸入之間放置數字乘法器來實現,如圖7所示。調制DAC輸出幅度的另一種方法是改變DAC的參考電壓。在AD9850中,內部參考控制放大器的帶寬約為1 MHz。這種方法在輸出幅度變化相對較小的情況下非常有效,只要輸出信號不超過+1 V的規格即可。

圖7:DDS系統中的幅度調制

DDS系統中的無雜散動態范圍考慮

在大多數DDS應用中,首要考慮因素是DAC輸出的頻譜純度。遺憾的是,該性能的測量、預測和分析十分復雜,涉及大量相互作用的因素。

即便是理想的N位DAC,也會在DDS系統中產生諧波。這些諧波的幅度主要取決于輸出頻率與時鐘頻率的比值。原因在于,DAC量化噪聲的頻譜成分會隨著該比值的變化而變化,雖然其理論均方根值仍等于q/√12(其中q是LSB的權重)。“量化噪聲表現為白噪聲,在奈奎斯特帶寬內均勻分布”這條假設在DDS系統中并不適用(這條假設在ADC系統中更為適用,因為ADC會給信號增加一定的噪聲,從而“擾動”量化誤差或使其隨機化。但是,依然存在一定的相關性)。例如,如果DAC輸出頻率精確設置為時鐘頻率的約數,則量化噪聲會集中在輸出頻率的倍數,也就是說,主要取決于信號。如果輸出頻率稍有失調,量化噪聲會變得更加隨機,從而改進有效SFDR。

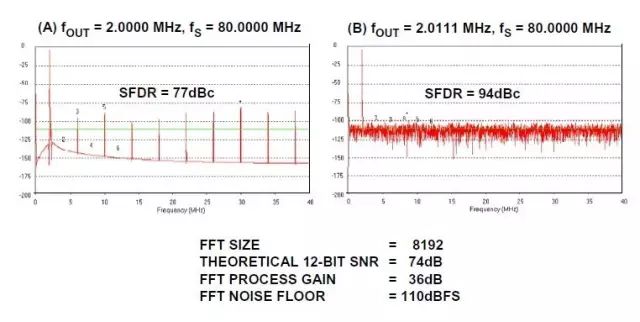

圖8說明了上述情況,其中4096 (4k)點FFT基于理想12位DAC中數字化生成的數據計算得出。左側圖表(A)中,所選的時鐘頻率和輸出頻率的比值恰好等于40,獲得的SFDR約為77 dBc。右側圖表中,比例稍有失調,有效SFDR增至94 dBc。在這一理想情況下,只是略微改變了頻率比,SFDR就改變了17 dB。

圖8:采用4096點FFT時,時鐘與輸出頻率比值對理論12位DAC SFDR的影響

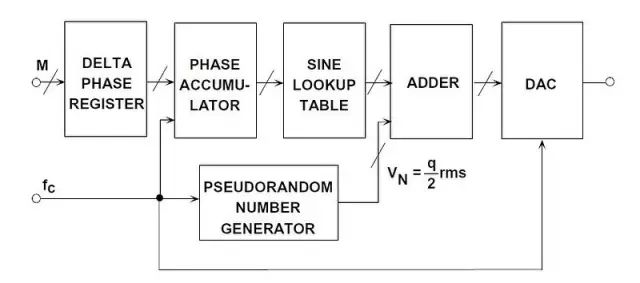

因此,通過仔細選擇時鐘與輸出頻率,就可以獲得最佳SFDR。但是,在有些應用中,這點可能難以實現。在基于ADC的系統中,增加少量的隨機噪聲至輸入就可能使量化誤差隨機化,并且減少這種效應。DDS系統中也可以實現同樣的效果,如圖9所示。偽隨機數字噪聲發生器輸出先增加至DDS正弦幅度字,然后再載入DAC。數字噪聲的幅度設置為1/2 LSB左右。這樣就能實現隨機化過程,代價是整體輸出本底噪聲會略微增加。但是,在大多數DDS系統中,有足夠的靈活性可以選擇不同的頻率比,因此不需要擾動。

圖9:向DDS系統注入數字擾動以使量化噪聲隨機化并提高SFDR

-

adc

+關注

關注

99文章

6534瀏覽量

545770 -

pll

+關注

關注

6文章

781瀏覽量

135333 -

DDS

+關注

關注

21文章

636瀏覽量

152943 -

時鐘驅動器

+關注

關注

0文章

34瀏覽量

13885

原文標題:一文看懂DDS原理、混疊、幅度調制

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【小梅哥帶你做項目】基于DDS技術的信號發生器系統

利用FPGA怎么設計DDS系統?

DDS在SIMULINK中的仿真設計

DDS,什么是DDS,DDS的結構

DDS是什么意思,DDS結構,DDS原理是什么

直接數字合成(DDS),直接數字合成(DDS)是什么意思

通過FPGA與并行處理技術實現DDS系統時鐘電路

dds系統的那些原理和知識

dds系統的那些原理和知識

評論