邏輯電平輸出是數(shù)字電路中的一個(gè)重要概念,它涉及到數(shù)字信號(hào)的表示和傳輸。在數(shù)字電路中,邏輯電平通常指的是電路中用于表示二進(jìn)制數(shù)字(0和1)的電壓水平。邏輯電平輸出則是指電路輸出端能夠提供的邏輯電平信號(hào)。

邏輯電平輸出的定義

邏輯電平輸出是指數(shù)字電路中的輸出端能夠產(chǎn)生的電壓水平,這些電壓水平用于表示邏輯狀態(tài)。在數(shù)字電路中,通常使用兩個(gè)不同的電壓水平來表示邏輯0和邏輯1。例如,邏輯0可能對(duì)應(yīng)于0V,而邏輯1可能對(duì)應(yīng)于5V或3.3V,這取決于電路的設(shè)計(jì)。

邏輯電平輸出的重要性

- 信號(hào)表示 :邏輯電平輸出是數(shù)字電路中信號(hào)表示的基礎(chǔ)。

- 信號(hào)傳輸 :邏輯電平輸出決定了信號(hào)在電路中的傳輸方式和效率。

- 兼容性 :不同的電路和設(shè)備可能需要不同的邏輯電平,邏輯電平輸出的兼容性對(duì)于系統(tǒng)的整體性能至關(guān)重要。

- 功耗 :邏輯電平輸出的電壓水平也影響電路的功耗。

邏輯電平輸出的類型

- TTL(晶體管-晶體管邏輯) :TTL邏輯電平輸出是早期數(shù)字電路中常用的一種標(biāo)準(zhǔn),邏輯1通常為3.3V或5V,邏輯0為0V。

- CMOS(互補(bǔ)金屬氧化物半導(dǎo)體) :CMOS邏輯電平輸出具有更低的功耗和更高的噪聲容限,邏輯1和邏輯0的電壓水平可能因不同的CMOS標(biāo)準(zhǔn)而異。

- LVDS(低壓差分信號(hào)) :LVDS是一種高速、低功耗的信號(hào)傳輸技術(shù),使用差分信號(hào)來表示邏輯電平。

邏輯電平輸出的應(yīng)用

- 微處理器與內(nèi)存 :在微處理器和內(nèi)存之間的數(shù)據(jù)傳輸中,邏輯電平輸出用于確保數(shù)據(jù)的正確表示和傳輸。

- 通信接口 :在串行通信接口如RS-232、USB、以太網(wǎng)等中,邏輯電平輸出用于信號(hào)的編碼和解碼。

- 傳感器與控制器 :在傳感器與微控制器之間的接口中,邏輯電平輸出用于信號(hào)的傳輸和處理。

技術(shù)細(xì)節(jié)

- 電壓水平 :邏輯電平輸出的電壓水平需要精確控制,以確保信號(hào)的正確解釋。

- 驅(qū)動(dòng)能力 :輸出端需要有足夠的驅(qū)動(dòng)能力,以確保信號(hào)能夠被接收端正確接收。

- 抗干擾能力 :邏輯電平輸出需要具備一定的抗干擾能力,以保證信號(hào)在噪聲環(huán)境下的穩(wěn)定性。

- 功耗 :邏輯電平輸出的設(shè)計(jì)需要考慮功耗,尤其是在電池供電的便攜設(shè)備中。

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

1952瀏覽量

64852 -

電壓

+關(guān)注

關(guān)注

45文章

5637瀏覽量

116254 -

數(shù)字信號(hào)

+關(guān)注

關(guān)注

2文章

982瀏覽量

47662 -

邏輯電平

+關(guān)注

關(guān)注

0文章

158瀏覽量

14473

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

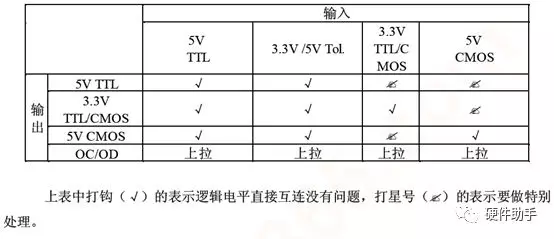

邏輯電平TTL/CMOS電平的互連、OC/OD的互連規(guī)范

邏輯電平設(shè)計(jì)規(guī)范(一)

232串聯(lián)電阻什么作用

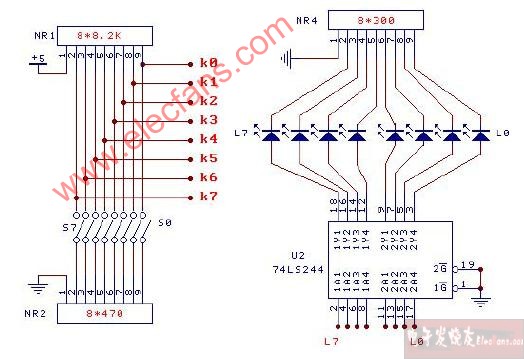

邏輯電平開關(guān)電路

邏輯電平詳細(xì)介紹

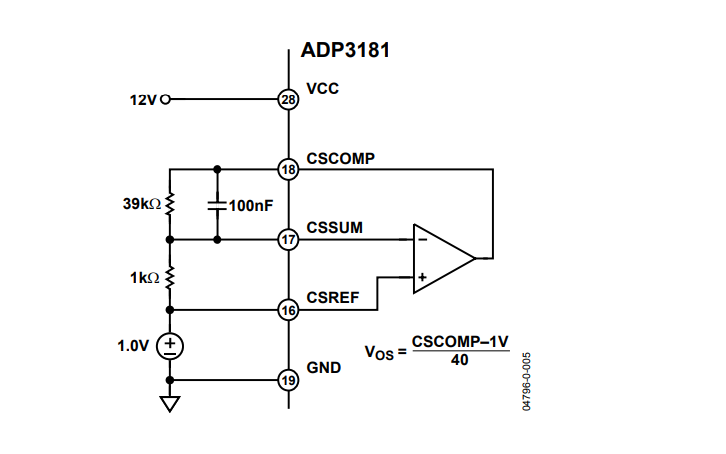

ADP3181多相同步降壓開關(guān)調(diào)節(jié)器控制器的數(shù)據(jù)手冊(cè)免費(fèi)下載

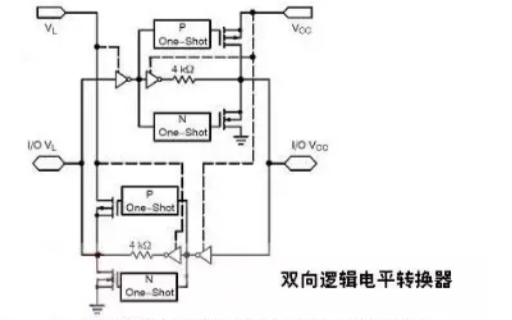

FPGA邏輯電平的互連電平轉(zhuǎn)換詳細(xì)說明

邏輯電平--差分信號(hào)(PECL、LVDS、CML)電平匹配

【硬聲推薦】邏輯電平視頻合集

引腳可編程輸出頻率、輸出邏輯電平及扇出功能的時(shí)鐘分配電路

什么是邏輯電平?如何實(shí)現(xiàn)電平轉(zhuǎn)換?(原理講解+電路圖)

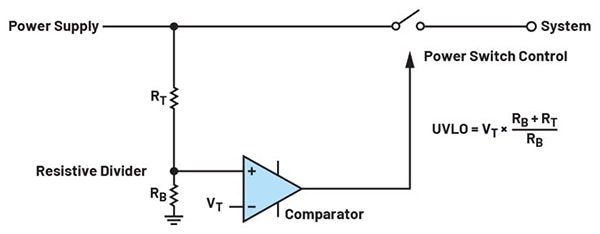

用于系統(tǒng)功率循環(huán)的高壓側(cè) MOSFET 輸入開關(guān)選擇

邏輯電平輸出是什么意思

邏輯電平輸出是什么意思

評(píng)論