工作模式

線程模式(Thread mode):處理器復位或異常退出時為此模式。此模式下的代碼可以是特權代碼也可以是用戶代碼,通過CONTROL[0]控制。

處理模式(Handler mode):出現異常(包括中斷)時進入此模式,此模式下所有代碼為特權訪問。

代碼權限

特權訪問:對處理器資源擁有完全訪問限權;處理器復位后進入此訪問模式;清零 CONTROL[0]進入用戶模式。

用戶訪問:禁止訪問多數系統寄存器。只能通過進入異常(中斷)來返回特權模式。進入異常前是用戶級訪問,則退出異常時自動回到用戶及,除非在異常中修改CONTROL[0]位。

工作狀態

Thumb狀態(正常執行指令狀態)和調試狀態。

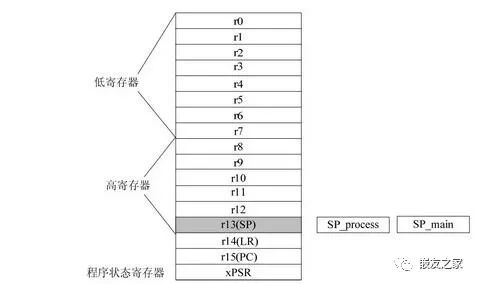

寄存器

r0-r12:通用寄存器,其中r8-r12只能被32位指令訪問。

r13(SP):堆棧指針;線程模式時可以在線程堆棧和主堆棧之間切換,但處理模式只使用主堆棧。兩個堆棧同一時刻只有一個可見,進入、退出異常時自動切換堆棧。

r14(LR):鏈接寄存器,保存子程序或異常的返回地址(要實現嵌套,必須入棧)。

r15(PC):程序計數器。

xPSR:特殊用途的程序狀態寄存器。

異常

進入異常步驟:

1.處理器在當前堆棧上把xPSR、PC、LR、r12、r3~r0八個寄存器自動依次入棧。

2.讀取向量表(如果是復位中斷,更新SP值)。

3.根據向量表更新PC值。

4.加載新PC處的指令(2、3、4步與1步同時進行)。

5.更新LR為EXC_RETURN(EXC_RETURN表示退出異常后返回的模式及使用的堆棧)。

退出異常步驟

1.根據EXC_RETURN指示的堆棧,彈出進入中斷時被壓棧的8個寄存器。

2.從剛出棧的IPSR寄存器[8:0]位檢測恢復到那個異常(此時為嵌套中斷中),若為0則恢復到線程模式。

3.根據EXC_RETURN,選擇使用相應SP。

末尾連鎖(Tail-chaining):當前正在執行中斷,又有一個中斷到來且這個中斷優先級比正在執行的中斷優先級低(如果有其他被壓棧的低優先級中斷則要比這些中斷優先級高),這個中斷暫時被掛起,等到當前中斷執行完后不再執行堆棧操作,而直接進入掛起的中斷。

遲來:前一個中斷還沒有進入執行階段(但處理器狀態已經保存),后面來了一個高優先級中,則前一個中斷被搶占,后來的高優先級中斷不需要再保存寄存器狀態。

中斷

Cortex-M3中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作'亞優先級'或'副優先級',每個中斷源都需要被指定這兩種優先級。

具有高搶占式優先級的中斷可以在具有低搶占式優先級的中斷處理過程中被響應,即中斷嵌套,或者說高搶占式優先級的中斷可以嵌套低搶占式優先級的中斷。

當兩個中斷源的搶占式優先級相同時,這兩個中斷將沒有嵌套關系,當一個中斷到來后,如果正在處理另一個中斷,這個后到來的中斷就要等到前一個中斷處理完之后才能被處理。如果這兩個中斷同時到達,則中斷控制器根據他們的響應優先級高低來決定先處理哪一個;如果他們的搶占式優先級和響應優先級都相等,則根據他們在中斷表中的排位順序決定先處理哪一個。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121198 -

中斷

+關注

關注

5文章

900瀏覽量

41759 -

Cortex-M3

+關注

關注

9文章

270瀏覽量

59591

原文標題:Cortex-M3的一些關鍵概念!

文章出處:【微信號:mcuworld,微信公眾號:嵌入式資訊精選】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

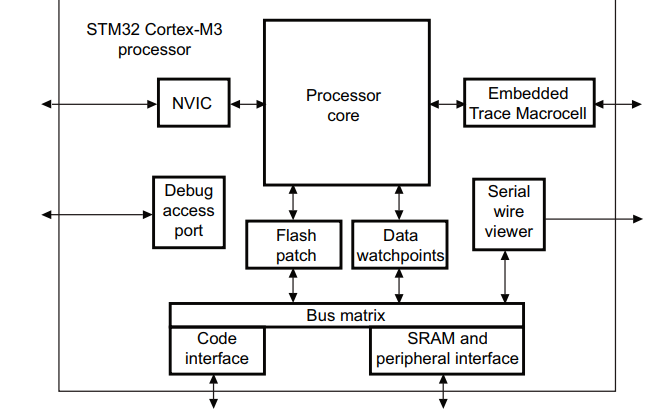

Cortex-M3處理器是什么

STM32的核心Cortex-M3處理器是什么

Cortex-M3處理器中斷與FreeRTOS中斷優先級配置

STM32的核心Cortex-M3處理器的標準化是什么意思

基于ARM Cortex-M3內核的STM32處理器有何性能

制造一種基于Cortex-M0和Cortex-M3處理器的SoC

基于ARM Cortex-M3處理器的電源設計及應用

STM32系列Cortex-M3處理器編程手冊免費下載

Cortex-M3處理器內核與基于Cortex-M3的MCU關系

詳細剖析Cortex-M3處理器

詳細剖析Cortex-M3處理器

評論